FPGA时钟无毛刺切换电路的制作方法

本发明涉及fpga,尤其涉及一种fpga时钟无毛刺切换电路。

背景技术:

1、在专用集成电路(application specific integrated circuit,asic)芯片设计中,对设计的低功耗措施之一就是门控时钟。门控时钟,指的是组合逻辑产生的时钟,其中,组合逻辑的输入可以全部是数据信号,也可以包含原始时钟信号。由于组合逻辑中的基本单元是与、或、非门等门电路,而与门和非门又具有“开关性”,故该类时钟又称为门控时钟。

2、但是在现场可编程逻辑门阵列(field programmable gate array,fpga)设计中,由于无法解决glitch(信号毛刺)、skew(时钟偏差)、jitters(时钟抖动)的问题,基本很少用到门控时钟,对有时钟频率切换的fpga产品都是以牺牲业务的连续性、从系统层面解决时钟切换的需求,例如:准备多份fpga配置文件,每个fpga配置文件使用不同的时钟频率。这种方法有着很大的局限性。

技术实现思路

1、针对现有技术存在的问题,本发明提供一种fpga时钟无毛刺切换电路。

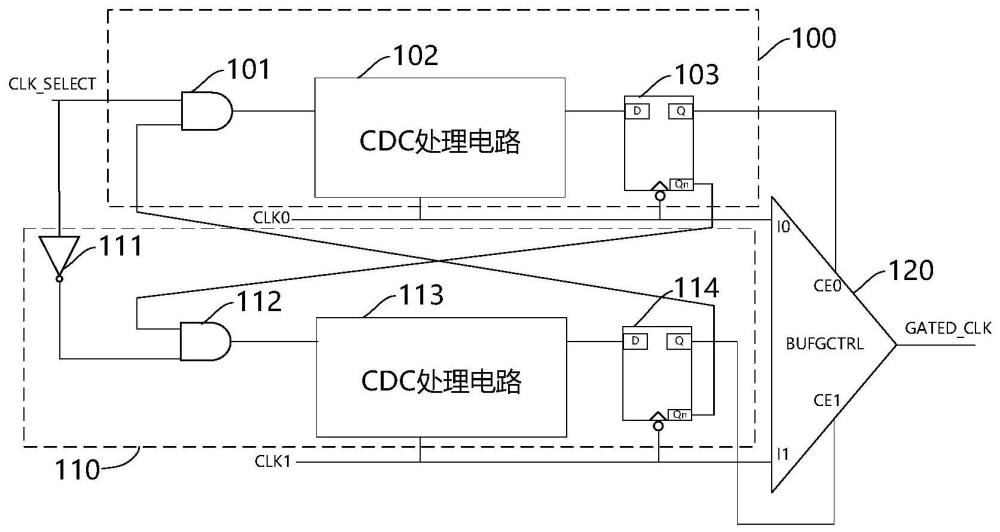

2、第一方面,本发明提供一种fpga时钟无毛刺切换电路,包括:

3、第一时钟电路,所述第一时钟电路包括第一与门、第一cdc处理电路和第一d触发器;

4、第二时钟电路,所述第二时钟电路包括反相器、第二与门、第二cdc处理电路和第二d触发器;

5、以及bufgctrl单元;

6、其中,时钟选择信号输入所述第一与门的第一输入端,所述第二d触发器的反相输出端连接所述第一与门的第二输入端,所述第一与门的输出信号输入所述第一cdc处理电路,所述第一cdc处理电路的输出信号输入所述第一d触发器的数据输入端,所述第一d触发器的输出端连接所述bufgctrl单元的第一使能端,第一时钟信号输入所述第一cdc处理电路、所述第一d触发器的时钟输入端、以及所述bufgctrl单元的第一输入端;

7、所述第一d触发器的反相输出端连接所述第二与门的第一输入端,所述时钟选择信号经所述反相器反相后输入所述第二与门的第二输入端,所述第二与门的输出信号输入所述第二cdc处理电路,所述第二cdc处理电路的输出信号输入所述第二d触发器的数据输入端,所述第二d触发器的输出端连接所述bufgctrl单元的第二使能端,第二时钟信号输入所述第二cdc处理电路、所述第二d触发器的时钟输入端、以及所述bufgctrl单元的第二输入端;

8、所述bufgctrl单元的输出为门控时钟信号。

9、在一些实施例中,所述第一cdc处理电路包括第三d触发器和第四d触发器;

10、其中,所述第一与门的输出信号输入所述第三d触发器的数据输入端,所述第三d触发器的输出端连接所述第四d触发器的数据输入端,所述第四d触发器的输出端连接所述第一d触发器的数据输入端,所述第一时钟信号输入所述第三d触发器的时钟输入端和所述第四d触发器的时钟输入端。

11、在一些实施例中,所述第三d触发器和所述第四d触发器均为上升沿触发的d触发器。

12、在一些实施例中,所述第二cdc处理电路包括第五d触发器和第六d触发器;

13、其中,所述第二与门的输出信号输入所述第五d触发器的数据输入端,所述第五d触发器的输出端连接所述第六d触发器的数据输入端,所述第六d触发器的输出端连接所述第二d触发器的数据输入端,所述第二时钟信号输入所述第五d触发器的时钟输入端和所述第六d触发器的时钟输入端。

14、在一些实施例中,所述第五d触发器和所述第六d触发器均为上升沿触发的d触发器。

15、在一些实施例中,所述第一d触发器和/或所述第二d触发器为下降沿触发的d触发器。

16、在一些实施例中,所述第四d触发器的输出端与所述第一d触发器的数据输入端之间的最大时延小于或等于所述第一时钟信号的半周期。

17、在一些实施例中,所述第六d触发器的输出端与所述第二d触发器的数据输入端之间的最大时延小于或等于所述第二时钟信号的半周期。

18、在一些实施例中,所述第一d触发器的输出端与所述bufgctrl单元的第一使能端之间的最大时延小于或等于所述第一时钟信号的半周期。

19、在一些实施例中,所述第二d触发器的输出端与所述bufgctrl单元的第二使能端之间的最大时延小于或等于所述第二时钟信号的半周期。

20、本发明提供的fpga时钟无毛刺切换电路,通过合理利用现有fpga的基础原语器件bufgctrl,结合asic专有芯片才有的无相关时钟切换free-glitch电路设计思路,可以有效解决现有门控时钟技术存在的skew、jitters、glitch等问题,从而实现fpga时钟无毛刺切换,并为变频fpga低功耗技术提供了设计上的强有力的基础。

技术特征:

1.一种fpga时钟无毛刺切换电路,其特征在于,包括:

2.根据权利要求1所述的fpga时钟无毛刺切换电路,其特征在于,所述第一cdc处理电路包括第三d触发器和第四d触发器;

3.根据权利要求2所述的fpga时钟无毛刺切换电路,其特征在于,所述第三d触发器和所述第四d触发器均为上升沿触发的d触发器。

4.根据权利要求1所述的fpga时钟无毛刺切换电路,其特征在于,所述第二cdc处理电路包括第五d触发器和第六d触发器;

5.根据权利要求4所述的fpga时钟无毛刺切换电路,其特征在于,所述第五d触发器和所述第六d触发器均为上升沿触发的d触发器。

6.根据权利要求3或5所述的fpga时钟无毛刺切换电路,其特征在于,所述第一d触发器和/或所述第二d触发器为下降沿触发的d触发器。

7.根据权利要求2或3所述的fpga时钟无毛刺切换电路,其特征在于,所述第四d触发器的输出端与所述第一d触发器的数据输入端之间的最大时延小于或等于所述第一时钟信号的半周期。

8.根据权利要求4或5所述的fpga时钟无毛刺切换电路,其特征在于,所述第六d触发器的输出端与所述第二d触发器的数据输入端之间的最大时延小于或等于所述第二时钟信号的半周期。

9.根据权利要求1、2或3所述的fpga时钟无毛刺切换电路,其特征在于,所述第一d触发器的输出端与所述bufgctrl单元的第一使能端之间的最大时延小于或等于所述第一时钟信号的半周期。

10.根据权利要求1、4或5所述的fpga时钟无毛刺切换电路,其特征在于,所述第二d触发器的输出端与所述bufgctrl单元的第二使能端之间的最大时延小于或等于所述第二时钟信号的半周期。

技术总结

本发明提供一种FPGA时钟无毛刺切换电路,涉及FPGA技术领域,该电路包括:第一时钟电路,第一时钟电路包括第一与门、第一CDC处理电路和第一D触发器;第二时钟电路,第二时钟电路包括反相器、第二与门、第二CDC处理电路和第二D触发器;以及BUFGCTRL单元。通过合理利用现有FPGA的基础原语器件BUFGCTRL,结合ASIC专有芯片才有的无相关时钟切换free‑glitch电路设计思路,可以有效解决现有门控时钟技术存在的skew、jitters、glitch等问题,从而实现FPGA时钟无毛刺切换,并为变频FPGA低功耗技术提供了设计上的强有力的基础。

技术研发人员:王利,赵维,刘银栋,赵亚琼,沈少辉,谢刚强,曹正,周永忠

受保护的技术使用者:北京国科天迅科技股份有限公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!