一种SUB-1G全频覆盖频率综合电路的制作方法

本发明属于射频通信芯片,具体涉及一种sub-1g全频覆盖频率综合电路。

背景技术:

1、根据各国无线通信的规定,在低于1ghz频段(sub-1g)划分出很多子频段用于各种不同的应用,有些是授权频段用于电信,广播,电视等。有些是开放频段比如:315mhz频段,433mhz频段,868mhz频段,915mhz频段等等。有些是专用频段比如:用于无线抄表470~510mhz频段,用于无人机频段840.5~845mhz,用于医疗,工业遥控174~216m,230m,407~425m,608~630m频段等等。由于sub-1g覆盖频率非常大,因而目前的技术,一般是针对某些应用频段设计芯片。

2、如图1所示的芯片设计方案。通过小数锁相环产生高频信号,再经过预分频电路(包括iq分频器1,iq分频器2,分频器2,mux(多路选择器))实现了对压控振荡器分频得到正交信号,i路输出信号ip/in,q路输出信号qp/qn,接到正交下混频电路iq-mixer,iq分频器1实现了对压控振荡器的2分频。iq分频器2实现了对iq分频器1输出信号的2分频。再通过多路选择器mux的选择,实现了对锁相环信号的正交2分频以及2次2分频实现4分频。pa的发射信号是单相,因而分频器2实现了对锁相环的单相除2或除4分频。

3、现有技术很难做到sub-1g频段(120~960mhz)全覆盖,只能是对特定频段的覆盖。

4、另外锁相环是频率综合模块的主要电路,随着锁相环的频率范围增加,其相位噪声将会有很大的恶化。由于压控振荡器的电感和电容决定了频率的范围,而在大量量产时电感和电容将各有最大±20%内的变化,因而为了达到稳定的覆盖所需频段,设计的频率范围需要有比较大的余量才能稳定覆盖所需频段。而过大的频率范围将对频率综合的锁相环的相位噪声有很大的影响,最终恶化接收芯片的抗干扰性能。

技术实现思路

1、本发明的目的在于提供一种sub-1g全频覆盖频率综合电路,在不需要过大的额外频率余量的情况下利用锁相环频率和预分频电路分频比的匹配,达到了sub-1g全频段无缝覆盖,并且保持比较好的相位噪声性能,以解决上述背景技术中提出的问题。

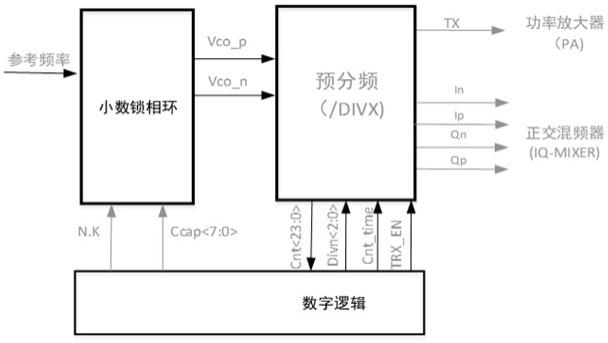

2、为实现上述目的,本发明采用了如下技术方案:一种sub-1g全频覆盖频率综合电路,包括小数锁相环,预分频电路、数字逻辑模块、功率放大器以及正交混频器,其中:所述小数锁相环的输出信号vco_n和vco_p接预分频电路;所述预分频电路输出的tx信号送到功率放大器、输出的ip,in,qp,qn信号送到正交混频器、输出cnt<23:0>接数字逻辑模块;所述数字逻辑模块输出的信号divn<2:0>、cnt_time和trx_en信号接预分频电路;所述数字逻辑模块输出的信号ccap<7:0>和n.k信号接小数锁相环。

3、优选地,所述预分频电路包括分频器1、分频器2、iq分频器1、iq分频器2、mux以及计数器,其中:所述信号vco_n和vco_p连接分频器1和分频器2,vco_n还接到计数器电路,所述计数器的另一个输入信号为cnt_time,其输出信号为cnt<23:0>;所述分频器1的另一个输入信号divn<2:0>用于设置分频器1的分频比,分频器1的输出信号dp,dn接iq分频器1,dp信号还接到分频器2;所述分频器2的另外两个输入信号为divn<2:0>和trx_en,其输出信号为tx;所述iq分频器1的另一个为输入信号trx_en,输入信号i4n,i4p,q4n,q4p接mux;所述iq分频器2的另一个信号为trx_en,输出为i6n,i6p,q6n,q6p接mux电路;所述mux根据输入信号divn<2:0>选择i4n,i4p,q4n,q4p或i6n,i6p,q6n,q6p输出。

4、优选地,所述数字逻辑模块的输出信号包括:trx_en信号、divn<2:0>信号以及cnt_time信号,其中:所述trx_en信号用于确定预分频是工作在发射或接收的分频状态;所述divn<2:0>信号用于设置预分频电路对压控振荡器的分频值;所述cnt_time信号为一个固定周期的脉冲信号,用于预分频的计数器电路,对压控振荡器输出vco_n信号进行计数,以得到vco的最大频率和最小频率。

5、优选地,所述数字逻辑模块的输出信号还包括:ccap<7:0>信号和n.k信号,其中:所述ccap<7:0>信号用于粗调vco的频率;所述n.k信号用于设置小数锁相环的分频值。

6、优选地,所述计数器输出的cnt<23:0>信号存到寄存器中,用于计算预分频的分频值的设定,以及锁相环的n.k的设定。

7、优选地,所述小数锁相环的频率为2.8~4.2ghz,预分频配置为除4分频,除6分频,除8分频,除12分频,除16分频,除20分频,除24分频,除28分频。

8、优选地,所述ccap<7:0>信号为小数锁相环的压控振荡器的开关电容控制位,通过设定ccap<7:0>信号的值,可调节压控振荡器的频率。

9、优选地,所述预分频电路用于把小数锁相环的信号分频到所需的射频频率上,用于接收的本振混频信号,或pa发射所需的射频信号。

10、优选地,所述预分频电路的输入为压控振荡器的高频信号输出vco_n,vco_p和分频比divn<2:0>;输出信号为用于接收正交混频的i路的差分信号ip,in,q路的差分信号qp,qn.以及用于功率放大器pa发射的单端信号tx。

11、优选地,所述分频器1用于对压控振荡器输出信号vco_n和vco_p的1~7分频。

12、本发明的技术效果和优点:本发明提出的一种sub-1g全频覆盖频率综合电路,与现有技术相比,具有以下优点:

13、本发明通过芯片上电时,对锁相环的最大频率和最小频率的测量及相应的算法,从而规避了压控振荡器的电感和电容值的偏差造成频率范围变化的影响,实现了在最小的锁相环压控振荡器的频率范围的情况下,无缝覆盖了120~960mhz频段,通过自适应的频率配置方式以及灵活的预分频电路,由于锁相环的频率范围减小了,其相位噪声得到了很大程度改善,芯片的抗干扰能力得到了很大的提高,在不需要过大的额外频率余量的情况下利用锁相环频率和预分频电路分频比的匹配,达到了sub-1g全频段无缝覆盖,并且保持比较好的相位噪声性能。

技术特征:

1.一种sub-1g全频覆盖频率综合电路,其特征在于,包括小数锁相环,预分频电路、数字逻辑模块、功率放大器以及正交混频器,其中:

2.根据权利要求1所述的一种sub-1g全频覆盖频率综合电路,其特征在于,所述预分频电路包括分频器1、分频器2、iq分频器1、iq分频器2、mux以及计数器,其中:

3.根据权利要求2所述的一种sub-1g全频覆盖频率综合电路,其特征在于,所述数字逻辑模块的输出信号包括:trx_en信号、divn<2:0>信号以及cnt_time信号,其中:

4.根据权利要求3所述的一种sub-1g全频覆盖频率综合电路,其特征在于,所述数字逻辑模块的输出信号还包括:ccap<7:0>信号和n.k信号,其中:

5.根据权利要求4所述的一种sub-1g全频覆盖频率综合电路,其特征在于,所述计数器输出的cnt<23:0>信号存到寄存器中,用于计算预分频的分频值的设定,以及锁相环的n.k的设定。

6.根据权利要求5所述的一种sub-1g全频覆盖频率综合电路,其特征在于,所述小数锁相环的频率为2.8~4.2ghz,预分频配置为除4分频,除6分频,除8分频,除12分频,除16分频,除20分频,除24分频,除28分频。

7.根据权利要求4所述的一种sub-1g全频覆盖频率综合电路,其特征在于,所述ccap<7:0>信号为小数锁相环的压控振荡器的开关电容控制位,通过设定ccap<7:0>信号的值,可调节压控振荡器的频率。

8.根据权利要求2所述的一种sub-1g全频覆盖频率综合电路,其特征在于,所述预分频电路用于把小数锁相环的信号分频到所需的射频频率上,用于接收的本振混频信号,或pa发射所需的射频信号。

9.根据权利要求8所述的一种sub-1g全频覆盖频率综合电路,其特征在于,所述预分频电路的输入为压控振荡器的高频信号输出vco_n,vco_p和分频比divn<2:0>;输出信号为用于接收正交混频的i路的差分信号ip,in,q路的差分信号qp,qn,以及用于功率放大器pa发射的单端信号tx。

10.根据权利要求9所述的一种sub-1g全频覆盖频率综合电路,其特征在于,所述分频器1用于对压控振荡器输出信号vco_n和vco_p的1~7分频。

技术总结

本发明属于射频通信芯片技术领域,具体涉及一种SUB‑1G全频覆盖频率综合电路,包括小数锁相环,预分频电路、数字逻辑模块、功率放大器以及正交混频器。通过芯片上电时,对锁相环的最大频率和最小频率的测量及相应的算法,从而规避了压控振荡器的电感和电容值的偏差造成频率范围变化的影响,实现了在最小的锁相环压控振荡器的频率范围的情况下,无缝覆盖了120~960MHZ频段,通过自适应的频率配置方式以及灵活的预分频电路,由于锁相环的频率范围减小了,其相位噪声得到了很大程度改善,芯片的抗干扰能力得到了很大的提高,在不需要过大的额外频率余量的情况下利用锁相环频率和预分频电路分频比的匹配,达到了SUB‑1G全频段无缝覆盖。

技术研发人员:邓建元,阮庆瑜

受保护的技术使用者:深圳市华普微电子股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!