可变阈值单比特ADC芯片以及SAR系统

本技术属于数据转换,尤其涉及一种可变阈值单比特adc芯片以及sar系统。

背景技术:

1、合成孔径雷达(synthetic aperture radar,sar)采用主动探测的方式,能够在复杂的环境中进行高精度的远距离勘测。其探测性能不受光照、云雨、雾霾等因素的影响,而且随着无人机、微型机器人等微型化平台的发展以及成熟的探测模式能够依据场景的不同而调整,满足更加丰富多变的现代应用场景,从而能够在城市勘测、公安反恐、灾难救援等众多领域发挥不可替代的作用。

2、随着无人机、微型机器人等微型化平台的发展与成熟,它们能够使sar系统以更加灵活的方式进行探测,但有限的平台体积与载重能力也对sar系统的微型化提出了更高的要求。然而sar系统为了实现高分辨成像,通常需要对具有大时宽带宽的回波信号进行高精度的采集,由此产生的巨大数据量将为后续的存储、传输与处理带来较大的压力。且随着成像分辨率的提高与观测场景的扩大,sar系统需要处理的数据量仍有不断增大的趋势。为了降低sar数据采集、存储、传输、处理等的系统复杂度,达到降低成本、减小系统体积的目的。近年来,单比特采样量化理论在系统架构简化与效率提升方面的优势再次引起信号处理领域的广泛关注。本技术的项目团队通过对单笔比特采样算法进行优化创新形成了本技术自己的单比特量化策略和快速处理算法,在这个算法体系中需要一款能提供单频阈值并对雷达回波信号进行快速实时处理的数据转换器芯片。

技术实现思路

1、为了解决上述技术问题,本技术实施例提供了一种可变阈值单比特adc芯片以及sar系统,旨在提供一种可变阈值单比特adc芯片可以降低雷达回波信号的计算复杂度,提高了数据处理的效率,在保证成像质量的前提下,达到简化系统架构、降低构造成本、提高成像效率的目的,促进雷达成像系统的低成本与微型化。

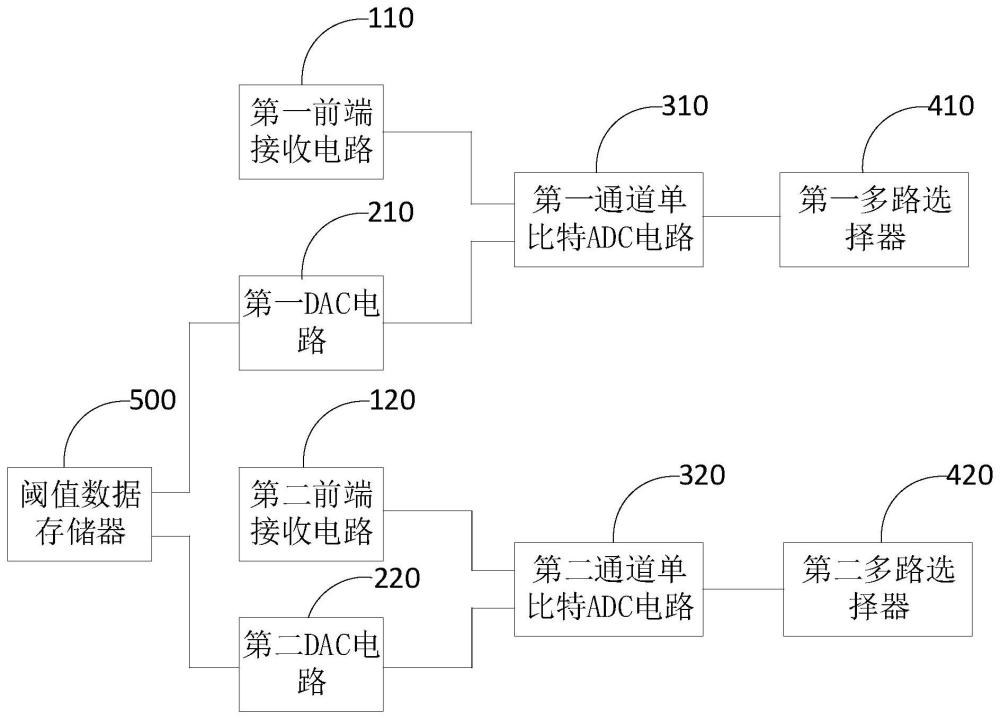

2、本技术实施例第一方面提供了一种可变阈值单比特adc芯片,所述可变阈值单比特adc芯片包括:

3、第一前端接收电路,用于接收第一通道雷达回波信号,并分时输出18路第一采样信号;

4、第二前端接收电路,用于接收第二通道雷达回波信号,并分时输出18路第二采样信号;

5、阈值数据存储器,用于存储第一数字码序列和第二数字码序列;

6、第一dac电路,用于获取所述第一数字码序列,并将所述第一数字码序列转化为18路第一模拟正弦波阈值;其中,相邻的所述第一模拟正弦波阈值的相位差为20度;

7、第二dac电路,用于获取所述第二数字码序列,并将所述第二数字码序列转化为18路第二模拟正弦波阈值;其中,相邻的所述第二模拟正弦波阈值的相位差为20度;

8、第一通道单比特adc电路,用于接收18路所述第一采样信号和18路所述第一模拟正弦波阈值,并根据所述第一模拟正弦波阈值将对应的所述第一采样信号转换为18路第一数字码;

9、第二通道单比特adc电路,用于接收18路所述第二采样信号和18路所述第二模拟正弦波阈值,并根据所述第二模拟正弦波阈值将对应的所述第二采样信号转换为18路第二数字码;

10、第一多路选择器,用于将18路所述第一数字码转换为第一路数字信号;

11、第二多路选择器,用于将18路所述第二数字码转换为第二路数字信号。

12、在一个实施例中,所述第一通道单比特adc电路包括18路第一单比特adc单元,18路所述第一单比特adc单元与18路所述第一采样信号一一对应,18路所述第一单比特adc单元与18路所述第一模拟正弦波阈值一一对应;

13、每路所述第一单比特adc单元用于接收对应的所述第一采样信号和所述第一模拟正弦波阈值,并根据所述第一采样信号和所述第一模拟正弦波阈值生成对应的所述第一数字码。

14、在一个实施例中,所述第二通道单比特adc电路包括18路第二单比特adc单元,18路所述第二单比特adc单元与18路所述第二采样信号一一对应,18路所述第二单比特adc单元与18路所述第二模拟正弦波阈值一一对应;

15、每路所述第二单比特adc单元用于接收对应的所述第二采样信号和所述第二模拟正弦波阈值,并根据所述第二采样信号和所述第二模拟正弦波阈值生成对应的所述第二数字码。

16、在一个实施例中,所述第一数字码序列包括至少4种阈值频率数字码和至少4种初始相位数字码;

17、所述第二数字码序列包括至少4种阈值频率数字码和至少4种初始相位数字码。

18、在一个实施例中,所述可变阈值单比特adc芯片还包括:

19、锁相环电路,用于接收外界的晶振频率,并根据所述晶振频率产生预设时钟频率;

20、时钟分配电路,用于根据所述时钟频率为所述前端接收电路提供采样时钟频率,以及为所述第一dac电路、所述第二dac电路、所述第一通道单比特adc电路、所述第二通道单比特adc电路提供对应的工作时钟频率。

21、在一个实施例中,所述可变阈值单比特adc芯片还包括:

22、误差校正电路,用于对第一dac电路、所述第二dac电路进行静态误差校正。

23、在一个实施例中,所述第一dac电路包括18路第一dac单元;所述误差校正电路用于向对应的所述第一dac单元输入第一预设数字码,以选通所述第一dac单元中对应的电流源;与所述第一dac单元对应的所述第一单比特adc单元根据所述第一dac单元的输出信号生成第一反馈信号;所述误差校正电路还用于根据所述第一反馈信号对所述第一dac单元中对应的电流源进行校正;

24、所述第二dac电路包括18路第二dac单元;所述误差校正电路用于向对应的所述第二dac单元输入第二预设数字码,以选通所述第二dac单元中对应的电流源;与所述第二dac单元对应的所述第二单比特adc单元根据所述第二dac单元的输出信号生成第二反馈信号;所述误差校正电路还用于根据所述第二反馈信号对所述第二dac单元中对应的电流源进行校正。

25、在一个实施例中,所述第一dac单元和所述第二dac单元均为八位dac转换器;所述八位dac转换器包括:输入寄存器、高位温度计译码单元、低位延迟链单元、开关驱动电路、开关阵列电路、第一输出电阻、第二输出电阻、第一反相器z1、第二反相器z2、电压带隙基准源、电压转电流单元、偏置电路以及电流源阵列;

26、所述输入寄存器的输入端用于接收8位数字码,所述输入寄存器的时钟信号端与所述第一反相器z1的输入端共接,并用于接收时钟信号,所述输入寄存器的输出端分别连接高位温度计译码单元和低位延迟链单元,所述高位温度计译码单元用于对所述输入寄存器输出的前四位数字码进行二进制权重处理,所述低位延迟链单元用于对所述输入寄存器输出的后四位数字码进行温度计码处理,所述高位温度计译码单元和所述低位延迟链单元的输出端连接所述开关驱动电路,所述第一反相器z1的输出端连接所述第二反相器z2的输入端,所述第二反相器z2的输出端连接所述开关驱动电路;

27、所述开关驱动电路连接所述开关阵列电路,所述电压带隙基准源连接所述电压转电流单元的输入端,所述电压转电流单元的输出端连接所述偏置电路的输入端,所述偏置电路的输出端连接所述电流源阵列,所述第一输出电阻的第一端连接供电端,所述第二输出电阻的第一端连接供电端,所述第一输出电阻的第二端与所述开关阵列电路的第一端共接作为第一电压信号输出端,所述第二输出电阻的第二端与所述开关阵列电路的第二端共接作为第二电压信号输出端;所述电压带隙基准源用于产生基准电压信号,所述电压转电流单元用于将所述基准电压信号转换为基准电流信号,所述偏置电路用于将所述基准电流信号转换为偏置电压输出至所述电流源阵列;所述开关驱动电路用于控制所述开关阵列电路的开关状态,以控制所述电流源阵列根据所述偏置电压进行电流切换。

28、在一个实施例中,所述锁相环电路包括:鉴频鉴相器、电荷泵、滤波器、压控振荡器、缓冲器以及分频器;

29、所述鉴频鉴相器的输入端与外部晶振连接,所述鉴频鉴相器的输出端连接所述电荷泵的输入端,所述电荷泵的输出端连接所述滤波器的输入端,所述滤波器的输出端连接所述压控振荡器的输入端,所述压控振荡器的输出端连接所述缓冲器的输入端,所述缓冲器的输出端作为所述锁相环电路的输出端,所述缓冲器的输出端还与所述分频器的输入端连接,所述分频器的输出端连接所述鉴频鉴相器的反馈端。

30、本技术实施例第二方面还提供了一种sar系统,所述sar系统包括如上述任一项实施例所述的可变阈值单比特adc芯片。

31、本技术实施例的有益效果:通过前端接收电路将输入的通道雷达回波信号采样保持后同时输入i通道和q通道,并分别进行载波调制,两路载波相互正交。在保持原始信号数据量不变的情况下,对i、q两路的各自18路通道提供20度的相位差的特定频率的正弦波阈值,然后由第一通道单比特adc电路、第二通道单比特adc电路将i、q两路信号各分为18路信号,最终每一路分别采样处理后再组成原始信号,这样成功降低了每路信号的采样率,降低了计算复杂度,提高了数据处理的效率,在保证成像质量的前提下,达到简化系统架构、降低构造成本、提高成像效率的目的,促进雷达成像系统的低成本与微型化。

- 还没有人留言评论。精彩留言会获得点赞!