一种焊盘侧壁全包金的印制电路板的制作方法与流程

本发明属于pcb板,具体涉及一种焊盘侧壁全包金的印制电路板的制作方法。

背景技术:

1、焊盘是指在电子元器件表面安装技术中,用于连接元器件引脚与印刷电路板(pcb)导线的一种金属圆片。焊盘通常由锡铜合金或镀金材料制成,具有良好的导电性和耐腐蚀性。焊盘在元器件安装中起到了至关重要的作用,能够确保元器件与pcb之间的可靠连接,同时也能够提供较好的机械强度和热稳定性。在焊接过程中,焊盘上会涂上一层焊膏,通过加热使其融化并与元器件引脚和pcb导线之间形成牢固的焊接连接。

2、目前很多镀金电路板要求镀金层包住焊盘的侧壁,因此只能在蚀刻图形时,设计工艺导线将镀金焊盘和边框铜皮连接在一起形成导电网络,焊盘镀金完成后再处理工艺导线。其具体工艺如下:在基板上蚀刻出镀金焊盘,设计镀金导线,将边框和焊盘连接;然后整板贴干膜,镀金焊盘位置做成开窗效果,干膜开窗需要比镀金焊盘大,确保抗镀金干膜不会因为对位偏位而盖住镀金焊盘,如此也会造成连接镀金焊盘的导线局部露出;开窗后对焊盘进行镀金处理(通过边框面铜和工艺导线导通镀金焊盘);最后褪去抗镀金干膜,并处理掉工艺导线。该工艺,其制备方法复杂,工艺导线处理后焊盘边缘残留不规则的凸点,影响客户设计的焊盘尺寸精度。具体来说,当工艺导线数量很多时通常会采用化学蚀刻方式去取工艺导线,当工艺导线数量较少且工艺导线较长时通常会采用人工通过刻刀去除工艺导线,或通过钻铣机等设备机械式去除工艺导线。无论按哪种方式处理,焊盘和导线连接位置都会有工艺导线残留,且焊盘间距小于10mil时,在焊盘之间设计的工艺导线无法有效防护,贴干膜时焊盘顶住干膜,工艺导线位置无法有效盖覆,镀金时导致渗金,残留的工艺导线变长。

3、因此,亟需提供一种焊盘全包金的印制电路板的制作方法,不仅能够实现焊盘侧壁全包金,且能够减少或避免工艺导线的残留,提高焊盘尺寸精度。

技术实现思路

1、为了克服现有技术的不足,本发明的目的在于提供一种焊盘侧壁全包金的印制电路板的制作方法。该制作方法不仅能够实现焊盘侧壁全包金,且能够减少或避免工艺导线的残留,提高焊盘尺寸精度。

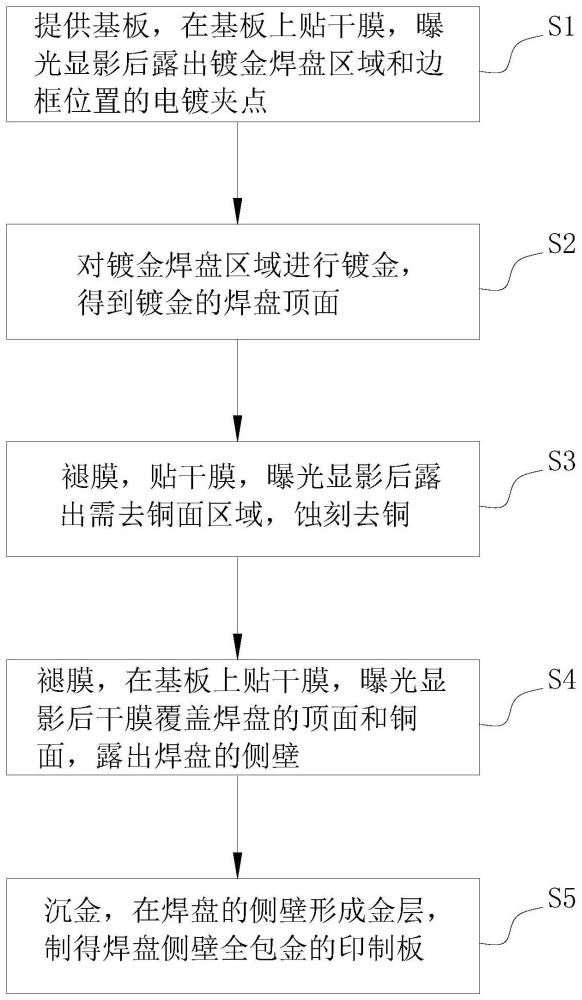

2、本发明提供了一种焊盘侧壁全包金的印制电路板的制作方法,包括以下步骤:

3、s1、提供基板,在基板上贴干膜,曝光显影后露出镀金焊盘区域和边框位置的电镀夹点;

4、s2、对镀金焊盘区域进行镀金,得到镀金的焊盘顶面;

5、s3、褪膜,贴干膜,曝光显影后露出需去铜面区域,蚀刻去铜;

6、s4、褪膜,在基板上贴干膜,曝光显影后所述干膜覆盖焊盘的顶面和铜面,露出焊盘的侧壁;

7、s5、沉金,在焊盘的侧壁形成金层,制得焊盘侧壁全包金的印制板。

8、在上述制作方法的步骤s1中,所述干膜为抗镀金干膜。

9、在上述制作方法的步骤s1中,在贴所述抗镀金干膜的步骤之前,还包括在基板上钻孔加工出光成像的对位孔。

10、在上述制作方法的步骤s4中,所述干膜为抗沉金干膜。

11、在上述制作方法的步骤s5中,所述焊盘设有多个。

12、在上述制作方法的步骤s5中,相邻所述焊盘的间距小于10mil。

13、在上述制作方法的步骤s5中,形成金层后,还包括褪干膜的步骤,即褪去覆盖焊盘的顶面和铜面的抗沉金干膜。

14、在上述制作方法的步骤s5中,所述褪干膜的步骤后还依次包括防焊、文字、成型、osp和包装的步骤。

15、更为具体地,一种焊盘侧壁全包金的印制电路板的制作方法,包括以下步骤:

16、s1、提供基板,在基板上钻孔加工出光成像的对位孔;然后在基板上贴抗镀金干膜,曝光显影后露出镀金焊盘区域和边框位置的电镀夹点;

17、s2、对镀金焊盘区域进行镀金,得到镀金的焊盘顶面;

18、s3、褪去所述抗镀金干膜,贴干膜,曝光显影后露出需去铜面区域,蚀刻去铜;

19、s4、褪去步骤s3中所述干膜,在基板上贴抗沉金干膜,曝光显影后所述抗沉金干膜覆盖焊盘的顶面和铜面,露出焊盘的侧壁;

20、s5、沉金,在焊盘的侧壁形成金层,褪去步骤s4中所述抗沉金干膜;然后经防焊、文字、成型、osp和包装的步骤,制得焊盘侧壁全包金的印制板。

21、相比现有技术,本发明的有益效果在于:

22、(1)本发明提供的焊盘侧壁全包金的印制电路板的制作方法,通过焊盘顶面镀金+侧壁沉金的加工方式,取消了工艺导线,避免了工艺导线残留位置出现的凸点和露铜。其中通过在焊盘的顶面镀金,能够满足键合使用要求;而侧壁沉金,能够有效防止侧壁露铜。本发明提供的制备方法,不仅实现了焊盘侧壁全包金效果,而且还使得镀金电路板在设计时无需考虑工艺导线受焊盘间距的限制,在焊盘间距小于10mil时,仍能制备出无工艺导线残留,焊盘尺寸精度高,焊盘侧壁全包金的印制电路板。

23、(2)本发明提供的制作方法能够实现焊盘侧壁全包金,避免工艺导线的残留,提高焊盘尺寸精度;且使得镀金电路板的设计不受镀金焊盘间距大小的限制,极大提升了镀金电路板的可设计性和可制造性。

24、下面结合附图和具体实施方式对本发明作进一步详细说明。

技术特征:

1.一种焊盘侧壁全包金的印制电路板的制作方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的制作方法,其特征在于,在步骤s1中,所述干膜为抗镀金干膜。

3.根据权利要求2所述的制作方法,其特征在于,在步骤s1中,在贴所述抗镀金干膜的步骤之前,还包括在基板上钻孔加工出光成像的对位孔。

4.根据权利要求1-3中任一项所述的制作方法,其特征在于,在步骤s4中,所述干膜为抗沉金干膜。

5.根据权利要求1-3中任一项所述的制作方法,其特征在于,在步骤s5中,所述焊盘设有多个。

6.根据权利要求5所述的制作方法,其特征在于,在步骤s5中,相邻所述焊盘的间距小于10mil。

7.根据权利要求4所述的制作方法,其特征在于,在步骤s5中,形成金层后,还包括褪抗沉金干膜的步骤。

8.根据权利要求7所述的制作方法,其特征在于,在步骤s5中,所述褪抗沉金干膜的步骤后还依次包括防焊、文字、成型、osp和包装的步骤。

9.根据权利要求8所述的制作方法,其特征在于,包括以下步骤:

技术总结

本发明属于PCB板技术领域,公开了一种焊盘侧壁全包金的印制电路板的制作方法。该制作方法包括:S1、提供基板,在基板上贴干膜,曝光显影后露出镀金焊盘区域和边框位置的电镀夹点;S2、镀金,得到镀金的焊盘顶面;S3、褪膜,贴干膜,曝光显影后露出需去铜面区域,蚀刻去铜;S4、褪膜,在基板上贴干膜,曝光显影后干膜覆盖焊盘的顶面和铜面,露出焊盘的侧壁;S5、沉金,在焊盘的侧壁形成金层,制得焊盘侧壁全包金的印制板。该制作方法能够实现电路板的焊盘侧壁全包金,避免工艺导线的残留,提高焊盘尺寸精度;且使得镀金电路板的设计不受镀金焊盘间距大小的限制,提升了镀金电路板的可设计性和可制造性。

技术研发人员:韩浩,杨恒勃,朱静,唐有军

受保护的技术使用者:珠海杰赛科技有限公司

技术研发日:

技术公布日:2024/3/24

- 还没有人留言评论。精彩留言会获得点赞!