摆率控制电路

本发明涉及电子电路,尤其涉及一种摆率控制电路。

背景技术:

1、芯片的信号输出电路主要负责将芯片内部的信号转换为外界可用的电压或电流信号。该电压或电流信号通过物理连线传输至外界,在传输的过程中,通常电源网络上会产生电压波动(例如,电压的下降和/或电压的增加),该电压波动会降低传输信号的品质(比如,影响传输时间、产生震荡、增加或降低信号的摆率)。若多个信号的摆率范围较大,外界的接收端需要较长的时间才能全部接收完该多个信号。同时,过高的摆率还会引起过冲和下冲,从而增加功耗。另外,当芯片的信号输出电路输出多个信号时,若在任意两个相邻时刻,该多个信号从高电平转换为低电平的信号数基本等于从低电平转换为高电平的信号数,则该多个信号的摆率范围将会较小;若在任意两个相邻时刻,该多个信号从高电平转换为低电平的信号数与从低电平转换为高电平的信号数相差较多时,则该多个信号的摆率范围将会较大,同时也会增加输出电路的功耗。

技术实现思路

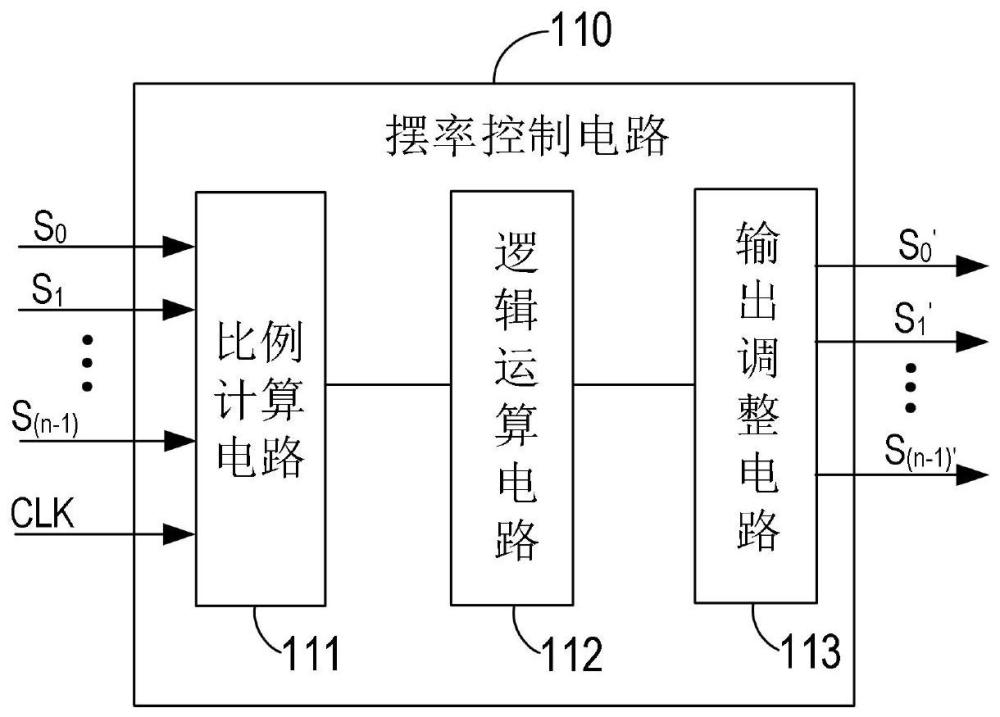

1、本技术提供了一种摆率控制电路。摆率控制电路包括:

2、比例计算电路,被配置为并行接收当前预设周期内的多个第一信号,并基于当前预设周期内的多个第一信号、上一预设周期内的多个调整后的第一信号和针对多个第一信号反相后的多个第二信号生成第一指示电压和第二指示电压,其中,第一指示电压指示由低电平转换为高电平的信号数与由高电平转换为低电平的信号数的大小关系,第二指示电压指示同时处于低电平的信号数与同时处于高电平的信号数的大小关系;

3、逻辑运算电路,与比例计算电路耦合,被配置为接收第一指示电压和第二指示电压,根据第一指示电压与第一参考电压和第二参考电压的大小关系及第二指示电压与第一参考电压和所述第二参考电压的大小关系产生运算结果,其中,第一参考电压大于第二参考电压;以及

4、输出调整电路,与逻辑运算电路耦合,被配置为根据运算结果确定是否对当前预设周期内的多个第一信号进行反相从而对应产生当前预设周期内的多个调整后的第一信号。

5、在一实施例中,第一参考电压为预设摆率范围的终止电压,第二参考电压为预设摆率范围的起始电压。

6、在一实施例中,比例计算电路包括:

7、第一比例计算电路,被配置为并行接收当前预设周期内的多个第一信号,并根据每个调整后的第一信号在上一预设周期所处的电平状态到对应的每个第一信号在当前预设周期所处的电平状态中由低电平转换为高电平的信号数与由高电平转换为低电平的信号数的大小关系产生第一指示电压;以及

8、第二比例计算电路,被配置为对并行接收的当前预设周期内的多个第一信号进行反相以得到多个第二信号,并根据每个调整后的第一信号在上一预设周期所处的电平状态到每个第二信号在当前预设周期所处的电平状态中由低电平转换为高电平的信号数与由高电平转换为低电平的信号数的大小关系产生第二指示电压。

9、在一实施例中,第一比例计算电路包括:

10、多个支路,其中,多个支路并联连接,每个第一信号在当前预设周期内的电压值均输入对应的一个支路;其中,从任一调整后的第一信号在上一预设周期所处的电平状态到对应的第一信号在当前预设周期所处的电平状态,若发生电平转换,对应的支路被导通从而在多个支路的公共端产生第一指示电压。

11、在一实施例中,多个支路中的每个支路包括并联连接的pmos晶体管和nmos晶体管以及电阻,其中,每个并联连接的pmos晶体管和nmos晶体管的第一端连接对应的第一信号在当前预设周期内的电压值,第二端连接电阻;其中,从任一调整后的第一信号在上一预设周期所处的电平状态到对应的第一信号在当前预设周期所处的电平状态,若发生电平转换,对应的nmos晶体管和对应的pmos晶体管被导通。

12、在一实施例中,第二比例计算电路包括:

13、多个支路,其中,多个支路并联连接,每个第二信号在当前预设周期内的电压值均输入对应的一个支路;其中,从任一调整后的第一信号在上一预设周期所处的电平状态到对应的第二信号在当前预设周期所处的电平状态,若发生电平转换,对应的支路被导通从而在多个支路的公共端产生第二指示电压。

14、在一实施例中,多个支路中的每个支路包括并联连接的pmos晶体管和nmos晶体管以及电阻,其中,每个并联连接的pmos晶体管和nmos晶体管的第一端连接对应的第二信号在当前预设周期内的电压值,第二端连接电阻;其中,从任一调整后的第一信号在上一预设周期所处的电平状态到对应的第二信号在当前预设周期所处的电平状态,若发生电平转换,对应的nmos晶体管和对应的pmos晶体管被导通。

15、在一实施例中,逻辑运算电路包括:

16、第一运算电路,与比例计算电路耦合,被配置为根据第一指示电压与第一参考电压和第二参考电压的大小关系产生第一运算结果;

17、第二运算电路,与比例计算电路耦合,被配置为根据第二指示电压与第一参考电压和第二参考电压的大小关系产生第二运算结果;以及

18、第三运算电路,与第一运算电路和第二运算电路耦合,被配置为对第一运算结果和第二运算结果进行逻辑运算并产生指示是否对当前预设周期内的多个第一信号进行反相的运算结果。

19、在一实施例中,当第一指示电压大于第一参考电压或小于第二参考电压时,第一运算结果为第一逻辑;以及

20、当第一指示电压处于第一参考电压和第二参考电压之间时,第一运算结果为第二逻辑,其中,第一逻辑与所述第二逻辑不相同。

21、在一实施例中,当第二指示电压大于第一参考电压或小于第二参考电压时,第二运算结果为第三逻辑;以及

22、当第二指示电压处于第一参考电压和第二参考电压之间时,第二运算结果为第四逻辑,其中第三逻辑与第四逻辑不相同。

23、在一实施例中,第一运算电路包括:

24、第一比较器,其中,第一比较器的同相输入端连接第一指示电压,第一比较器的反相输入端连接第一参考电压,第一比较器的输出端输出第一比较结果;

25、第二比较器,其中,第二比较器的同相输入端连接第二参考电压,第二比较器的反相输入端连接第二指示电压,第二比较器的输出端输出第二比较结果;以及

26、异或门,其中,异或门对第一比较结果和第二比较结果进行异或运算并产生第一运算结果。

27、在一实施例中,第二运算电路包括:

28、第三比较器,其中,第三比较器的同相输入端连接第一参考电压,第三比较器的反相输入端连接第二指示电压,第三比较器的输出端输出第三比较结果;

29、第四比较器,其中,第四比较器的同相输入端连接第二指示电压,第四比较器的反相输入端连接第二参考电压,第四比较器的输出端输出第四比较结果;以及

30、第一与门,其中,第一与门对第三比较结果和第四比较结果进行与运算并产生第二运算结果。

31、在一实施例中,第三运算电路包括:

32、第二与门,与第一运算电路和第二运算电路耦合,被配置为对第一运算结果和第二运算结果进行与运算并产生运算结果。

33、在一实施例中,处于第五逻辑的运算结果指示对当前预设周期内的多个第一信号进行反相;处于第六逻辑的运算结果指示不对当前预设周期内的多个第一信号进行反相,其中,第五逻辑与第六逻辑不相同。

34、在一实施例中,输出调整电路包括:

35、并联的第一pmos晶体管和第一nmos晶体管,以及

36、依次串联的第二pmos晶体管、第三pmos晶体管、第二nmos晶体管、第三nmos晶体管;

37、其中,运算结果连接第一pmos晶体管的控制端和第三nmos晶体管的控制端,多个第一信号连接第三pmos晶体管的控制端、第二nmos晶体管的控制端及并联的第一pmos晶体管和第一nmos晶体管的公共节点,反相后的运算结果连接第一nmos晶体管的控制端和第二pmos晶体管的控制端。

38、本技术通过确定每个调整后的第一信号在上一预设周期所处的电平状态到每个第一信号在当前预设周期所处的电平状态之间的电平关系以及每个调整后的第一信号在上一预设周期所处的电平状态到每个第二信号在当前预设周期所处的电平状态之间的电平关系,从而确定是否需要对当前预设周期内的多个第一信号进行反相以得到当前预设周期内的多个调整后的第一信号,进而使多个调整后的第一信号的摆率范围处于预设摆率范围内,同时也降低了功耗。

- 还没有人留言评论。精彩留言会获得点赞!