宽频带和宽共模的输入接收电路的制作方法

本发明属于集成电路领域,涉及一种输入接收电路,尤其涉及一种宽频带和宽共模的输入接收电路。

背景技术:

1、差分信号相比于普通的单端信号有着抗干扰能力强、能有效抑制emi(电磁干扰)、时序定位精确等优势。标准差分信号如lvds、lvpec以及cml电平等具有低功耗、低误码率、低串扰和低辐射等优点,已被广泛应用于串行高速数据通讯场合中。其中lvds标准规定输入信号的共模电压范围为:0.05~0.235v(100mv输入电压),这对于0~3v电压域是比较宽的共模范围。为扩大接收电路的输入共模范围,现有技术通过将nmos型输入对管放大器与pmos型输入对管放大器相结合形成互补接收结构。一方面,随着输入信号频率的提升,系统带宽不够,需要更大的电流来提高输出信号的质量,造成芯片功耗增加。另一方面,对于宽共模范围接收时,该结构的输出信号占空比较差,需要在后级增加占空比矫正电路或引入共模反馈进行调整,增加了电路复杂度和功耗。

技术实现思路

1、为了解决背景技术中存在的上述技术问题,本发明提供了一种具有宽频带以及宽共模范围且功耗低的输入接收电路。

2、为了实现上述目的,本发明采用如下技术方案:

3、一种宽频带和宽共模的输入接收电路,其特征在于:所述宽频带和宽共模的输入接收电路包括差分信号输入端、信号输出端、时钟接收电路以及电流模逻辑电路;所述差分信号输入端通过时钟接收电路接入电流模逻辑电路;所述电流模逻辑电路接入信号输出端。

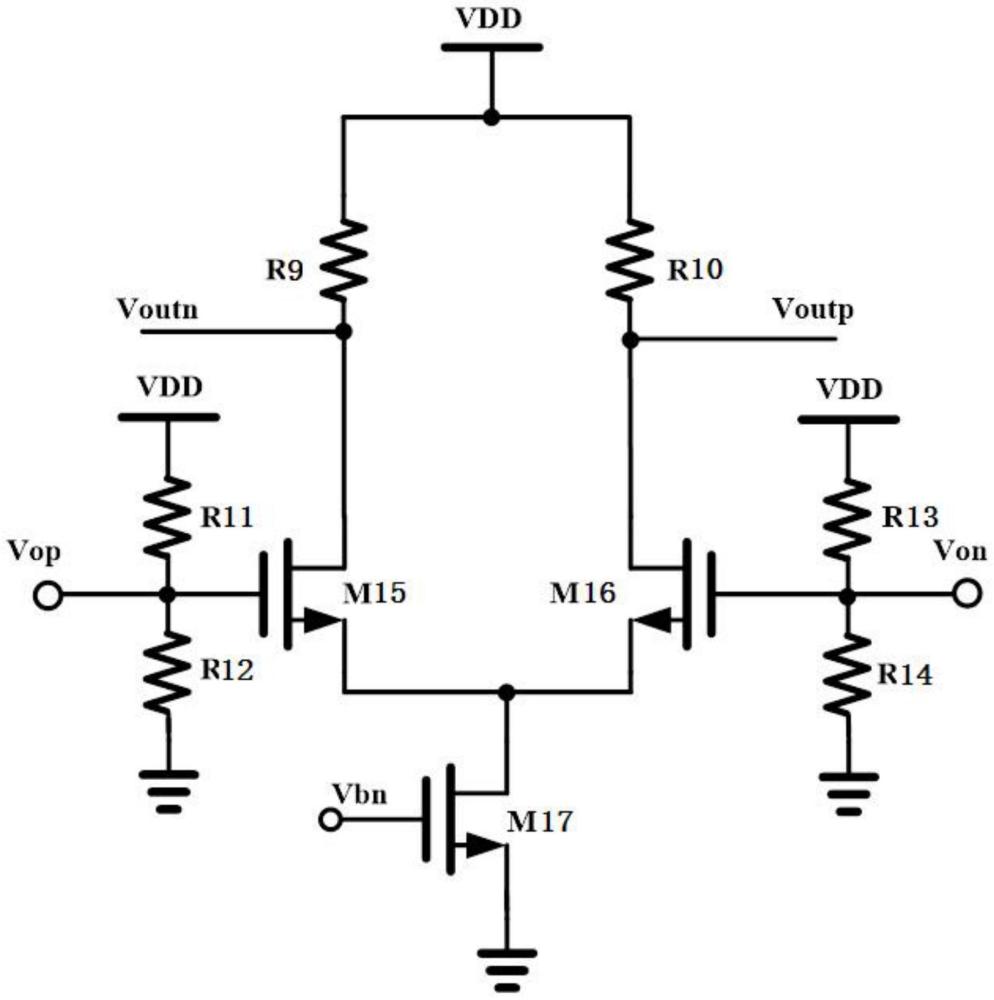

4、上述电流模逻辑电路包括电源vdd、电阻r9、电阻r10、电阻r11、电阻r12、电阻r13、电阻r14、晶体管m15、晶体管m16以及晶体管m17;所述电源vdd通过电阻r9、晶体管m15以及晶体管m17接地;所述电源vdd通过电阻r10、晶体管m16以及晶体管m17接地;所述电源vdd通过电阻r11接入晶体管m15;所述电源vdd通过电阻r11以及电阻r12接地;所述电源vdd通过电阻r13接入晶体管m16;所述电源vdd通过电阻r13以及电阻r14接地;所述差分信号输入端通过时钟接收电路分别接入晶体管m15以及晶体管m16;所述电源vdd通过电阻r9接入信号输出端;所述电源vdd通过电阻r10接入信号输出端。

5、上述电源vdd通过电阻r9接入晶体管m15的漏极;所述晶体管m15的源极接入晶体管m17的漏极;所述晶体管m17的源极接地;所述晶体管m17的栅极接入vbn;所述电源vdd通过电阻r10接入晶体管m16的漏极;所述晶体管m16的源极接入晶体管m17的漏极;所述电源vdd通过电阻r11接入晶体管m15的栅极;所述电源vdd通过电阻r13接入晶体管m16的栅极;所述差分信号输入端通过时钟接收电路分别接入晶体管m15的栅极以及晶体管m16的栅极。

6、上述信号输出端包括信号正向输出端voutp以及信号反向输出端voutn;所述电源vdd通过电阻r9接入信号反向输出端voutn;所述电源vdd通过电阻r10接入正向输出端voutp。

7、上述时钟接收电路包括电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、电阻r6、电阻r7、电阻r8、开关sw1、开关sw2、开关sw3、开关sw4、晶体管m1、晶体管m2、晶体管m3、晶体管m4、晶体管m5、晶体管m6、晶体管m7、晶体管m8、晶体管m9、晶体管m10、晶体管m11、晶体管m12、晶体管m13、晶体管m14、电容c1以及电容c2;所述电源vdd分别与电阻r1、电阻r2、电阻r3、电阻r4以及晶体管m10相连;所述电阻r1与开关sw1并联;所述电阻r2与开关sw2并联;所述电阻r3与开关sw3并联;所述电阻r4开关sw4并联;所述电阻r1通过晶体管m6、晶体管m13以及电阻r5接地;所述电阻r2通过晶体管m4、晶体管m1以及晶体管m3接地;所述晶体管m6分别与晶体管m4以及晶体管m1相连;所述晶体管m1通过电容c1与晶体管m13相连;所述晶体管m10分别与晶体管m8以及晶体管m9相连;所述晶体管m8通过电容c1与晶体管m13相连;所述晶体管m8通过晶体管m11以及电阻r6接地;所述晶体管m13分别与晶体管m11以及晶体管m8相连;所述电阻r4通过晶体管m7、晶体管m14以及电阻r8接地;所述电阻r3通过晶体管m5、晶体管m2以及晶体管m3接地;所述晶体管m7分别与晶体管m5以及晶体管m2相连;所述晶体管m2通过电容c2与晶体管m14相连;所述晶体管m9通过电容c2与晶体管m14相连;所述晶体管m9通过晶体管m12以及电阻r7接地;所述晶体管m14分别与晶体管m12以及晶体管m9相连;所述差分信号输入端分别接入晶体管m8以及晶体管m9;所述晶体管m13接入晶体管m15;所述晶体管m14接入晶体管m16。

8、上述电源vdd与晶体管m10的源极相连;所述电阻r1接入晶体管m6的源极;所述晶体管m6的漏极接入晶体管m13的漏极;所述晶体管m6的栅极分别接入晶体管m4的栅极以及晶体管m1的漏极;所述晶体管m13的源极通过电阻r5接地;所述晶体管m13的栅极分别接入晶体管m11的栅极以及晶体管m8的漏极;所述电阻r2接入晶体管m4的源极;所述晶体管m4的漏极接入晶体管m1的漏极;所述晶体管m8的漏极接入晶体管m11的漏极;所述晶体管m8的栅极通过电容c1接入晶体管m13的漏极;所述晶体管m8的源极接入晶体管m10的漏极;所述晶体管m11的源极通过电阻r6接地;所述输入端vbp接入晶体管m10的栅极;所述晶体管m1的栅极通过电容c1接入晶体管m13的漏极;所述晶体管m1的源极接入晶体管m3的漏极;所述晶体管m3的源极接地;所述晶体管m3的栅极接入输入端vbn;所述电阻r4接入晶体管m7的源极;所述晶体管m7的漏极接入晶体管m14的漏极;所述晶体管m7的栅极分别接入晶体管m5的栅极以及晶体管m2的漏极;所述晶体管m14的源极通过电阻r8接地;所述晶体管m14的栅极分别接入晶体管m12的栅极以及晶体管m9的漏极;所述电阻r3接入晶体管m5的源极;所述晶体管m5的漏极接入晶体管m2的漏极;所述晶体管m9的漏极接入晶体管m12的漏极;所述晶体管m9的栅极通过电容c2接入晶体管m14的漏极;所述晶体管m9的源极接入晶体管m10的漏极;所述晶体管m12的源极通过电阻r7接地;所述晶体管m2的栅极通过电容c2接入晶体管m14的漏极;所述晶体管m2的源极接入晶体管m3的漏极;所述差分信号输入端分别接入晶体管m8的栅极以及晶体管m9的栅极;所述晶体管m13的漏极接入晶体管m15的栅极;所述晶体管m14的漏极接入晶体管m16的栅极。

9、上述差分信号输入端包括差分信号正向输入端vip以及差分信号反向输入端vin;所述差分信号正向输入端vip接入晶体管m8的栅极;所述差分信号反向输入端vin接入晶体管m9的栅极。

10、本发明的优点是:

11、本发明提供了一种宽频带和宽共模的输入接收电路,包括差分信号输入端、信号输出端、时钟接收电路以及电流模逻辑电路;差分信号输入端通过时钟接收电路接入电流模逻辑电路;电流模逻辑电路接入信号输出端。本发明所提供的宽频带和宽共模的输入接收电路采用两级放大思路:第一级采用时钟接收电路,通过直流耦合和交流耦合相结合的方式提高电路接收频带,采用互补差分对接收宽共模范围的差分时钟信号;第二级采用电流模逻辑电路,在内部自建共模,以电流模逻辑(cml)结构提供高增益并增强链路驱动能力。本发明结构简单,无需占空比校正或共模反馈电路进行调整,输出信号占空比可达49%~51%,支持从dc~ghz输入信号接收,输入共模可实现0~vdd全覆盖,功耗低,带宽较高,适用于高速信号收发系统中。

- 还没有人留言评论。精彩留言会获得点赞!