一种TSPC-D触发器及高速电路的制作方法

本申请涉及触发器,特别是涉及一种tspc-d触发器及高速电路。

背景技术:

1、在高速电路中通常会使用到高速触发器,真单相时钟(true single phaseclock,tspc)触发器就是一种典型的高速d触发器(一个具有记忆功能的,具有两个稳定状态的信息存储器件)。

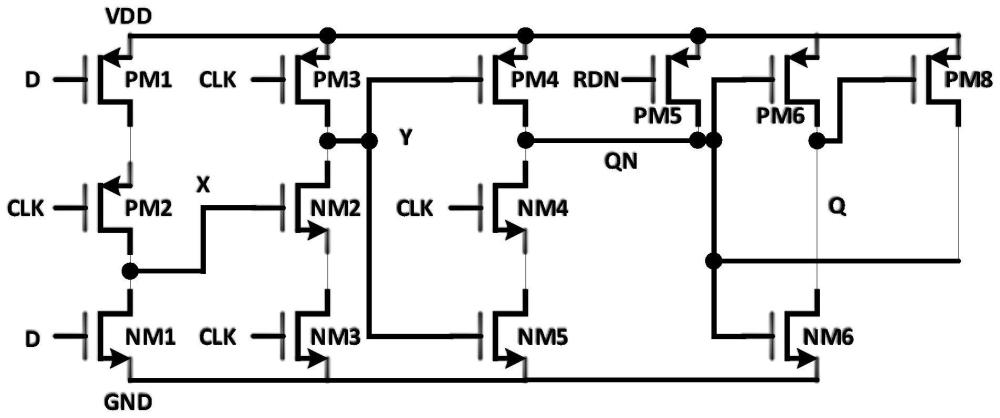

2、一种传统的tspc-d触发器电路如图1所示,包括三级电路、复位mos管和一个反相器,共由6个p型mos管(pmos)和6个n型mos管(nmos)组成。tspc-d触发器在复位状态即将结束进入工作状态时(即输入电平d、时钟信号clk仍保持低电平,复位信号rdn由低电平变为高电平时),虽然触发器此时还没有信号输入,但会因为pmos和nmos的关断电阻相差过大,导致某一级的输出电平发生变化,输出电平由复位阶段的低电平(0)慢慢拉高至高电平(1),进而导致触发器的输出从复位状态下的低电平变为高电平,后续的电路如果不注意则会产生不必要的错误。

3、所以,现在本领域的技术人员亟需要一种tspc-d触发器,解决目前的tspc-d触发器在输入信号发生变化前、将要离开复位状态时,不能保持初始的复位状态的问题。

技术实现思路

1、本申请的目的是提供一种tspc-d触发器及高速电路,以解决目前的tspc-d触发器在输入信号发生变化前、将要离开复位状态时,不能保持初始的复位状态的问题。

2、为解决上述技术问题,本申请提供一种tspc-d触发器,包括三级电路、复位mos管和反相器,其中,多级电路至少为三级;其特征在于,还包括:反相电路;

3、多级电路的输出端与反相器连接,复位mos管设置于多级电路和反相器的公共端处;其中,多级电路的输出端作为反向输出端,反相器的输出端作为正向输出端;

4、反相电路设置于第二级电路或设置于反向输出端,用于反相反向输出端处的输出电平。

5、另一方面,多级电路为三级电路,包括:第一级电路、第二级电路和第三级电路;

6、其中,第一级电路、第二级电路和第三级电路依次连接,且第三级电路的输出端作为多级电路的输出端。

7、另一方面,反相电路设置于第二级电路中,用于通过反向第二级电路的输出电平,以反相反向输出端处的输出电平。

8、另一方面,反向电路设置于反向输出端,用于直接反相反向输出端处的输出电平。

9、另一方面,第一级电路包括:第一pmos管、第二pmos管和第一nmos管;

10、其中,第一pmos管和第一nmos管的栅极作为tspc-d触发器的电平输入端;第二pmos管的栅极作为时钟信号输入端;第一pmos管的源极与电源正极连接;第一pmos管的漏极与第二pmos管的源极连接;第二pmos管的漏极与第一nmos管的漏极连接,并作为第一级电路的输出端与第二级电路连接;第一nmos管的源极接地;

11、第二级电路包括:第三pmos管、第二nmos管和第三nmos管;

12、其中,第三pmos管和第三nmos管的栅极作为时钟信号输入端;第二nmos管的栅极与第一级电路的输出端连接;第三pmos管的源极与电源正极连接;第三pmos管的漏极与第二nmos管的漏极连接,并作为第二级电路的输出端与第三级电路连接;第二nmos管的源极与第三nmos管的漏极连接;第三nmos管的源极接地;

13、反相电路包括:第一反向pmos管;

14、其中,第一反向pmos管设置于第三pmos管的漏极与第二nmos管的漏极之间;第一反向pmos管的栅极与第一级电路的输出端连接,第一反向pmos管的源极与第三pmos管的漏极连接,第一反向pmos管的漏极与第二nmos管的漏极连接,作为第二级电路的输出端与第三级电路连接。

15、另一方面,第三级电路包括:第四pmos管、第四nmos管和第五nmos管;

16、其中,第四pmos管和第五nmos管的栅极与第二级电路的输出端连接;第四nmos管的栅极作为时钟信号输入端;第四pmos管的源极与电源正极连接;第四pmos管的漏极与第四nmos管的漏极连接,作为第三级电路的输出端与反相器连接;第四nmos管的源极与第五nmos管的漏极连接;第五nmos管的源极接地;

17、复位mos管包括:第五pmos管;

18、第五pmos管的栅极作为复位端,第五pmos管的源极与电源正极连接,第五pmos管的漏极与反向输出端连接;

19、反相器包括:第六pmos管和第六nmos管;

20、第六pmos管和第六nmos管的栅极与第三级电路的输出端连接;第六pmos管的源极与电源正极连接;第六pmos管的漏极与第六nmos管的漏极连接,作为tspc-d触发器的输出端;第六nmos管的源极接地;

21、反相电路包括:第二反向pmos管;

22、其中,第二反向pmos管的栅极与tspc-d触发器的输出端连接,第二反向pmos管的源极与电源正极连接,第二反向pmos管的漏极与反向输出端连接。

23、另一方面,第一反向pmos管与第三nmos管的关断电阻之比在10:1~20:1之间。

24、为解决上述技术问题,本申请还提供一种高速电路,包括如上述的tspc-d触发器。

25、本申请提供的一种tspc-d触发器,通过在原有tspc-d触发器电路的基础上,于tspc-d触发器中的第二级电路中或者反向输出端处添加反相电路,以将tspc-d触发器在复位信号结束后的初始阶段出现变化的输出电平反相拉回高电平;从而保证tspc-d触发器反向输出端处的输出电平经反相器后,最终的输出电平仍然保持在低电平;避免初始数据产生不必要的错误,保证后级电路的正常功能实现,有利于维护整个系统的稳定性和可靠性。

26、本申请提供的高速电路,与上述tspc-d触发器对应,效果同上。

技术特征:

1.一种tspc-d触发器,包括多级电路、复位mos管和反相器,其中,所述多级电路至少为三级;其特征在于,还包括:反相电路;

2.根据权利要求1所述的tspc-d触发器,其特征在于,所述多级电路为三级电路,包括:第一级电路、第二级电路和第三级电路;

3.根据权利要求2所述的tspc-d触发器,其特征在于,所述反相电路设置于所述第二级电路中,用于通过反向所述第二级电路的输出电平,以反相所述反向输出端处的输出电平。

4.根据权利要求2所述的tspc-d触发器,其特征在于,所述反向电路设置于反向输出端,用于直接反相所述反向输出端处的输出电平。

5.根据权利要求3所述的tspc-d触发器,其特征在于,所述第一级电路包括:第一pmos管、第二pmos管和第一nmos管;

6.根据权利要求4所述的tspc-d触发器,其特征在于,所述第三级电路包括:第四pmos管、第四nmos管和第五nmos管;

7.根据权利要求5所述的tspc-d触发器,其特征在于,所述第一反向pmos管与所述第三nmos管的关断电阻之比在10:1~20:1之间。

8.一种高速电路,其特征在于,包括如权利要求1至7任意一项所述的tspc-d触发器。

技术总结

本申请公开一种TSPC‑D触发器及高速电路,涉及触发器技术领域,针对目前的TSPC‑D触发器不能在离开复位状态时保持复位状态的问题,提供一种TSPC‑D触发器,通过在原有TSPC‑D触发器电路的基础上,于TSPC‑D触发器中的反向输出端处或者反向输出端的前一级电路中添加反相电路,以将TSPC‑D触发器在复位状态即将结束进入工作状态时出现变化的输出电平反相拉回高电平;从而保证TSPC‑D触发器反向输出端处的输出电平经反相器后,最终的输出电平仍然保持在低电平;避免初始数据产生不必要的错误,保证后级电路的正常功能实现,有利于维护整个系统的稳定性和可靠性。

技术研发人员:黄耀,杨海玲,王润华,王亚宁,连夏梦

受保护的技术使用者:上海集成电路研发中心有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!