一种控制灵活可靠的快跳频率源的制作方法

本发明涉及微波射频电路,特别涉及一种控制灵活可靠的快跳频率源。

背景技术:

1、跳频通信是一种载波频率进行伪随机跳变的通信技术,具有抗干扰性好、抗截获能力强、保密性好等优点,快跳频率源是跳频通信中的关键部分。“乒乓式”跳频源是一种常用的实现快跳的方法,它使用两个锁相环,在一个锁相环工作时,另一个锁相环完成下一个频率的锁定,频率切换时间仅为纳秒级的开关切换时间。为了达到更高的跳速,可以采用更多锁相环进行切换的方法来实现。

2、传统的乒乓式快跳频率源是按照预定的顺序进行锁相环的切换,上级系统无法控制与了解锁相环的使用情况,并且由于多个锁相环的控制时序较为复杂,控制数据与切换信号必须严格按照预定的控制时序,当控制数据或切换时序发生错误后,锁相环的切换将会进入错乱的状态且无法恢复;当某一锁相环发生故障时,顺序切换的方法不能避开故障的锁相环;并且上级系统也不能实时掌握当前正在使用的是哪一个锁相环,以上问题都会影响系统的正常工作。

技术实现思路

1、有鉴于此,本发明提供了一种控制灵活可靠的快跳频率源,采用多个锁相环乒乓切换的方法,实现了较高的跳频速率,并且在控制数据和硬件接口上增加了锁相环的编号信息,根据编号信息对指定的锁相环进行配置与选择,使上级系统可以准确地掌控快跳频率源中多个锁相环的使用情况,提高了快跳频率源使用的灵活性与可靠性。

2、本发明采用的技术方案是:

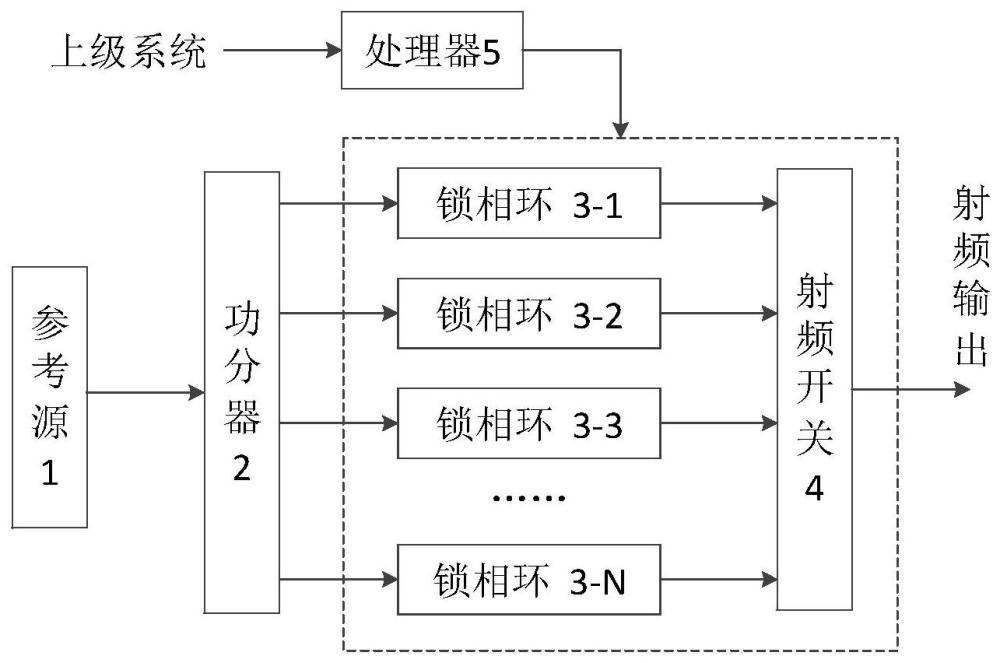

3、一种控制灵活可靠的快跳频率源,包括参考源、功分器、n个锁相环、射频开关和处理器;其中,参考源产生锁相环的参考信号,功分器将参考源产生的参考信号分为n路给n个锁相环,每个锁相环根据处理器的频率配置信息产生相应的射频频率并输出至射频开关,射频开关根据处理器的控制指令从n路射频信号中选择一路输出,处理器接收上级系统的控制信息,并转换为锁相环与射频开关的控制指令,同时将锁相环状态回报上级系统。

4、进一步地,锁相环的个数n是根据系统的最高跳速要求和单个环路锁定时间所决定的,假设系统最高跳速要求为m跳/秒,单个环路锁定时间为串口传数时间t1、处理器解析数据时间t2、处理器配置锁相环时间t3和锁相环频率相位锁定时间t4之和t,则n为大于t×m+1的整数。

5、进一步地,处理器的对外接口包括时钟、数据、使能、切换、回报、编号的控制线,其中,时钟、数据、使能三个控制线用于上级系统向处理器传输控制数据,切换控制线用于触发射频开关的切换,回报控制线用于回报当前工作锁相环的锁定状态,编号控制线由n根线组成,每根线均具有一个编码,每个编码对应一个锁相环的编号。

6、进一步地,上级系统向处理器所传输的控制数据中除频率信息外,还具有锁相环编号信息,处理器解析频率信息并转换为锁相环的控制字,然后对相应编号的锁相环进行配置。

7、进一步地,当跳频源收到切换信号时,处理器判断此时编号控制线的状态,根据编号控制线的编码切换到相应的锁相环。

8、进一步地,在满足跳频速率的情况下,上级系统选择部分锁相环工作,当某一锁相环工作不正常时,跳过此锁相环。

9、本发明与背景技术相比具有以下优点:

10、1、本发明中,当控制数据或切换时序出现错误后,仅影响所对应一个频点的状态,后续控制数据与切换时序正常后跳频频点仍能够正常输出。

11、2、本发明中,上级系统可灵活地控制锁相环的使用,可根据需要改变多个锁相环工作的先后顺序,并且能实时掌握当前在用锁相环的编号。

12、3、本发明中,在满足跳频速率的前提下,上级系统可选择部分锁相环工作,当某一锁相环工作不正常时,可跳过此锁相环。

技术特征:

1.一种控制灵活可靠的快跳频率源,其特征在于,包括参考源(1)、功分器(2)、n个锁相环(3-1、3-2……3-n)、射频开关(4)和处理器(5);其中,参考源(1)产生锁相环的参考信号,功分器(2)将参考源(1)产生的参考信号分为n路给n个锁相环(3-1、3-2……3-n),每个锁相环(3-1、3-2……3-n)根据处理器(5)的频率配置信息产生相应的射频频率并输出至射频开关(4),射频开关(4)根据处理器(5)的控制指令从n路射频信号中选择一路输出,处理器(5)接收上级系统的控制信息,并转换为锁相环与射频开关的控制指令,同时将锁相环状态回报上级系统。

2.根据权利要求1所述的一种控制灵活可靠的快跳频率源,其特征在于,锁相环的个数n是根据系统的最高跳速要求和单个环路锁定时间所决定的,假设系统最高跳速要求为m跳/秒,单个环路锁定时间为串口传数时间t1、处理器解析数据时间t2、处理器配置锁相环时间t3和锁相环频率相位锁定时间t4之和t,则n为大于t×m+1的整数。

3.根据权利要求1所述的一种控制灵活可靠的快跳频率源,其特征在于,处理器的对外接口包括时钟、数据、使能、切换、回报、编号的控制线,其中,时钟、数据、使能三个控制线用于上级系统向处理器传输控制数据,切换控制线用于触发射频开关的切换,回报控制线用于回报当前工作锁相环的锁定状态,编号控制线由n根线组成,每根线均具有一个编码,每个编码对应一个锁相环的编号。

4.根据权利要求3所述的一种控制灵活可靠的快跳频率源,其特征在于,上级系统向处理器所传输的控制数据中除频率信息外,还具有锁相环编号信息,处理器解析频率信息并转换为锁相环的控制字,然后对相应编号的锁相环进行配置。

5.根据权利要求3所述的一种控制灵活可靠的快跳频率源,其特征在于,当跳频源收到切换信号时,处理器判断此时编号控制线的状态,根据编号控制线的编码切换到相应的锁相环。

6.根据权利要求1所述的一种控制灵活可靠的快跳频率源,其特征在于,在满足跳频速率的情况下,上级系统选择部分锁相环工作,当某一锁相环工作不正常时,跳过此锁相环。

技术总结

本发明公开了一种控制灵活可靠的快跳频率源,属于微波射频电路技术领域。它由参考源、功分器、多个锁相环、射频开关、处理器等部分组成,本发明采用多个锁相环乒乓切换的方法,实现了较高的跳频速率,并且在控制数据和硬件接口上增加了锁相环的编号信息,根据编号信息对指定的锁相环进行配置与选择,使上级系统可以准确地掌控快跳频率源中多个锁相环的使用情况,提高了快跳频率源使用的灵活性与可靠性。

技术研发人员:张杰,王帅,王天雄,绳宇洲,吴景宇

受保护的技术使用者:中国电子科技集团公司第五十四研究所

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!