用于数据规格化的电路及方法、芯片、计算设备与流程

本公开涉及电路,具体地,涉及一种用于数据规格化的电路及方法、芯片和计算设备。

背景技术:

1、随着科学技术的不断发展,各领域对诸如处理器的各类装置的高处理性能的需求与日俱增。在这类装置中,常常涉及对数据进行规格化的需求。例如,浮点数具有比定点数精度更高和计算范围更广的优势,因此在项目工程中得到了非常广泛的应用,而在浮点运算过程中,对浮点数进行规格化是其中的一个关键环节,而且往往处在浮点运算的关键路径上。因此,如何更快速地实现数据的规格化对于提升相关装置的处理性能起着非常重要的作用。

技术实现思路

1、有鉴于此,本公开提供了一种用于数据规格化的电路及方法、芯片和计算设备,可以缓解、减轻或甚至消除上述问题。

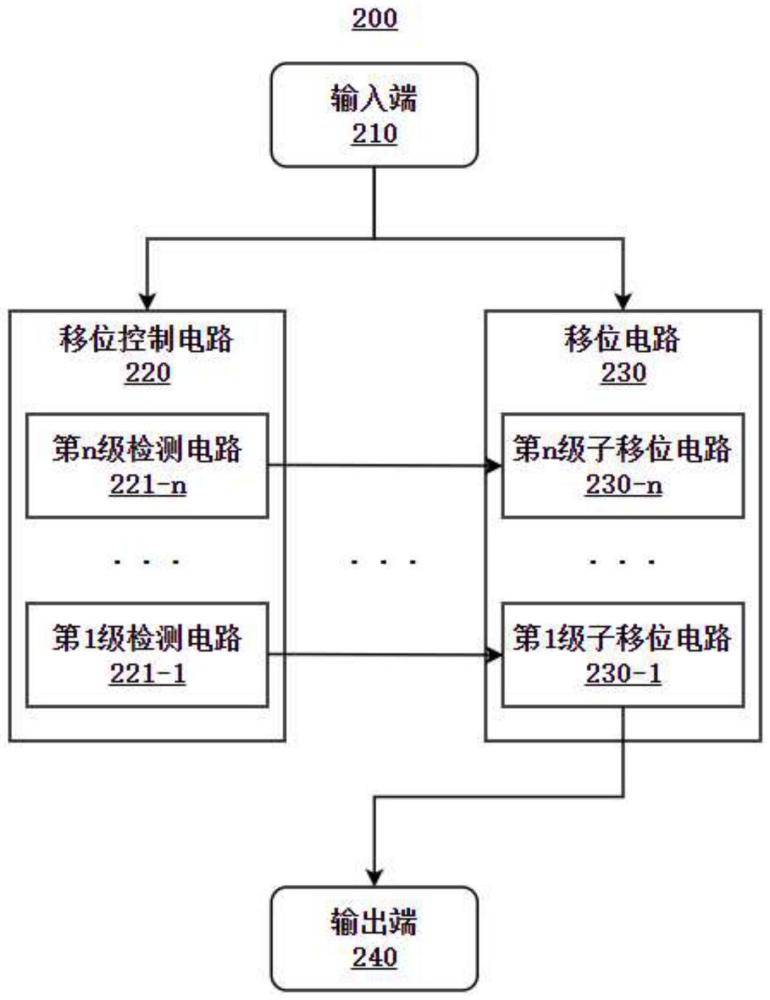

2、根据本公开的一方面,提供了一种用于数据规格化的电路,包括:输入端,被配置为:接收初始数据,初始数据为位宽小于或等于2n的待规格化的数据,其中n为大于0的整数;移位控制电路,包括n级检测电路,其中,n级检测电路中的第i级检测电路被配置为:响应于初始数据的首个非零值不在i级移位的移位范围内,输出第一信号值,或者,响应于初始数据的首个非零值在i级移位的移位范围内,输出第二信号值,其中,i为大于0、小于或等于n的整数;移位电路,包括n级子移位电路,其中,n级子移位电路中的第n级子移位电路接收初始数据作为输入数据,其他第i级子移位电路接收第i+1级子移位电路的输出数据作为输入数据,以及其中,n级子移位电路中的第i级子移位电路被配置为:响应于来自第i级检测电路的第一信号值,对输入数据向首位方向执行i级移位,并输出经移位的数据,或者,响应于来自第i级检测电路的第二信号值,输出输入数据;输出端,被配置为:输出移位电路中的第1级子移位电路的输出数据,作为与初始数据相对应的规格化数据。

3、在一些实施例中,移位控制电路还包括n级编码电路,n级编码电路中的第i级编码电路包括第i级分区电路,第i级分区电路被配置为:基于初始数据,确定至少一个i级编码区,使得至少一个i级编码区恰好覆盖i级移位的移位范围,以及,其中,第i级检测电路被进一步配置为:响应于初始数据的首个非零值不处于至少一个i级编码区中,输出第一信号值,或者,响应于初始数据的首个非零值处于至少一个i级编码区中,输出第二信号值。

4、在一些实施例中,至少一个i级编码区中的各i级编码区以以下各项中的一项为首位:初始数据的首位、相应i+1级编码区的首位、相应i+1级非编码区的首位,并且各i级编码区具有i级预设位宽,以及其中,i级移位的移位宽度等于i级预设位宽。

5、在一些实施例中,i级预设位宽为2i-1。

6、在一些实施例中,第i级分区电路被进一步配置为:从初始数据的首位开始,连续读取2i-1个数据位,作为一个i级编码区,以及,迭代执行以下步骤:响应于初始数据中的剩余位宽大于2i-1,与前一i级编码区间隔2i-1个数据位之后,连续读取2i-1个数据位,作为一个i级编码区,否则,停止读取i级编码区。

7、在一些实施例中,该电路还包括:拼接电路,被配置为将各级检测电路所输出的信号值进行拼接,并输出拼接数据。

8、在一些实施例中,第i级编码电路还包括第i级赋值电路,第i级赋值电路被配置为:针对至少一个i级编码区中的每个i级编码区,响应于该i级编码区包含非零值,将对应于该i级编码区的编码值确定为第一值,或者,响应于该i级编码区不包含非零值,将对应于该i级编码区的编码值确定为第二值;以及其中,第i级检测电路被进一步配置为:响应于i至n级编码区中的至少一个编码区的编码值指示初始数据的首个非零值不处于至少一个i级编码区中,输出第一信号值,或者,响应于i至n级编码区中的至少一个编码区的编码值指示初始数据的首个非零值处于至少一个i级编码区中,输出第二信号值。

9、在一些实施例中,第i级赋值电路包括至少一个或电路,至少一个或电路中的每个或电路与至少一个i级编码区中的一个i级编码区相对应,并被配置为:接收对应i级编码区中各数据位的值,并输出对应于对应i级编码区的编码值。

10、在一些实施例中,第i级检测电路包括:至少一个检测逻辑电路,至少一个检测逻辑电路中的每个检测逻辑电路与至少一个i级编码区中的一个i级编码区相对应,并被配置为:响应于落入从初始数据的首位至对应i级编码区的范围内的编码区的编码值都为第二值,并且,覆盖对应i级编码区之后的相邻i级非编码区、并且不覆盖对应i级编码区之后的相邻i级编码区的编码区的编码值为第一值或不存在,输出第一信号值,否则,输出第二信号值;检测输出电路,被配置为:响应于至少一个检测逻辑电路的输出信号中存在第一信号值,输出第一信号值,否则,输出第二信号值。

11、在一些实施例中,至少一个检测逻辑电路中的每个检测逻辑电路被进一步配置为:响应于恰好覆盖从初始数据的首位至对应i级编码区的范围、并且彼此不重叠的至少一个编码区的编码值都为第二值,并且,覆盖对应i级编码区之后的相邻i级非编码区、并且不覆盖对应i级编码区之后的相邻i级编码区的编码区的编码值为第一值或不存在,输出第一信号值,否则,输出第二信号值。

12、在一些实施例中,至少一个检测逻辑电路中的每个检测逻辑电路包括与电路,与电路的输入端被配置为接收以下两项中的至少一项:恰好覆盖从初始数据的首位至对应i级编码区的范围、并且彼此不重叠的至少一个编码区的编码值的非,覆盖对应i级编码区和在对应i级编码区之后的相邻i级非编码区的一个编码区的编码值。

13、在一些实施例中,初始数据的首个非零值为从初始数据的最高位起的首个非零值,以及,将输入数据向首位方向进行移位包括:将输入数据向最高位方向进行移位。

14、根据本公开的另一方面,提供了一种芯片,包括前述实施例所描述的电路。

15、根据本公开的又一方面,提供了一种计算设备,包括前述实施例所描述的电路。

16、根据本公开的再一方面,提供了一种用于数据规格化的方法,包括:接收初始数据,初始数据为位宽小于或等于2n的待规格化的数据,其中n为大于0的整数;针对初始数据,并行地执行n级检测,其中,第i级检测包括:响应于初始数据的首个非零值不在i级移位的移位范围内,生成i级第一信号值,或者,响应于初始数据的首个非零值在i级移位的移位范围内,生成i级第二信号值,其中,i为大于0、小于或等于n的整数;针对初始数据,执行n级移位处理,并输出经处理的数据,作为与初始数据相对应的规格化数据,其中,n级移位处理中的第i级移位处理包括:接收i级输入数据,其中,当i等于n时,i级输入数据为初始数据,当i大于0、小于n时,i级输入数据为第i+1级移位处理的输出数据;响应于i级第一信号值,对i级输入数据向首位方向执行i级移位,并输出经移位的数据,或者,响应于i级第二信号值,输出i级输入数据。

17、本公开提供的用于数据规格化的电路包括移位控制电路和移位电路,其中,移位控制电路包括n级检测电路,移位电路包括n级子移位电路。第i级子移位电路可以根据来自第i级检测电路所输出的移位控制信号的信号值来操作,而各级检测电路可以并行执行,检测初始数据的首个非零值是否落入该级移位范围内,从而输出相应信号值以指示是否应执行该级移位,同时,较高级子移位电路的操作与较低级检测电路的操作可以并行执行。如此,可以实现各级子移位电路的并行操作,从而有助于实现移位控制电路和移位电路的最大化并行执行,提升数据规格化的速度。

18、根据在下文中所描述的实施例,本公开的这些和其它方面将是清楚明白的,并且将参考在下文中所描述的实施例而被阐明。

- 还没有人留言评论。精彩留言会获得点赞!