具有半导体通道层的半导体元件的制作方法

本公开内容关于一种半导体元件,特别涉及一种具有多个掺杂区的半导体层。

背景技术:

1、随着电子产业的快速发展,集成电路(ic)已经实现高性能及小型化。集成电路在材料及设计方面的技术进步更持续产生新一代的集成电路,每一代都比上一代的电路更小、更复杂。

2、动态随机存取存储器(dram)元件是一种随机存取存储器,它将每一位元数据存储在集成电路内的一个单独的电容器中。通常情况下,dram以每个存储胞(cell)具有一个电容器与晶体管的方形阵列排列。当前,4f2dram存储胞的垂直晶体管已被开发,其中f代表光学光刻最小特征宽度或关键尺寸(cd)。然而,随着字元线间距的不断缩小,dram制造商面临着缩小存储胞面积的巨大挑战。

3、上文的“现有技术”说明仅是提供背景技术,并未承认上文的“现有技术”说明揭示本公开的标的,不构成本公开的现有技术,且上文的“现有技术”的任何说明均不应做为本公开的任一部分。

技术实现思路

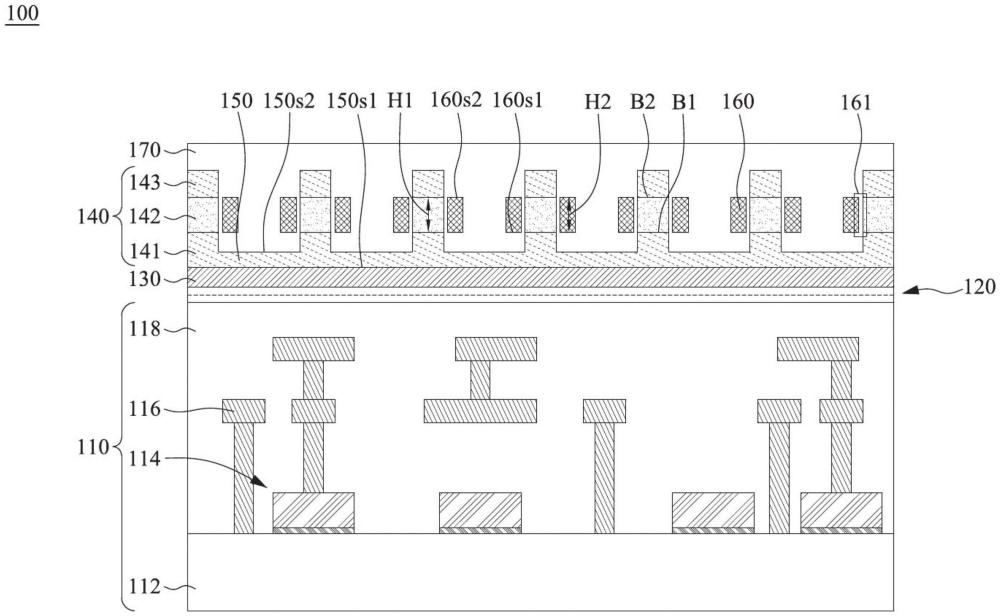

1、本公开的一个实施例提供一种半导体元件。该半导体元件包括一基底、一位元线、一半导体层及一字元线。该位元线设置于该基底上。该半导体层设置于该位元线上。该字元线邻接该半导体层。该字元线具有面向该基底的一下表面及与该下表面相对的一上表面。该半导体层包括具有一第一导电类型的一第一掺杂区,以及具有与该第一导电类型相反的一第二导电类型的一第二掺杂区。该第一掺杂区设置于该第二掺杂区与该位元线之间。该第一掺杂区与该第二掺杂区之间的一第一边界实质上与该字元线的该下表面对齐。该第一掺杂区的一掺杂物与该第三掺杂区的一掺杂物不同。该第二掺杂区与一第三掺杂区之间的一第二边界实质上与该字元线的该上表面对齐。

2、本公开的另一个方面提供一种半导体元件。该半导体元件包括一基底、一位元线、多个半导体层、多个字元线、一半导体连接结构及一掺杂物扩散层。该位元线设置于该基底上。该半导体层设置于该位元线上。该多个半导体层中的至少一者包含具有一第一导电类型的一第一掺杂区。每个字元线围绕该多个半导体层中各自的一个。该半导体连接结构与该多个半导体层连接。掺杂物扩散层邻接该第一掺杂区。

3、本公开的实施例提供一种半导体元件及其制备方法。该半导体元件可包括具有做为源极、漏极及/或通道的掺杂区的半导体层。在该实施例中,通道的长度可由字元线的垂直长度决定,该字元线可被精确控制。此外,半导体层及其中的一些掺杂区可以在一个晶圆中形成,该晶圆将被键合到另一个含有栅极结构或其他对热积存(thermal budget)敏感的元素的晶圆上。在此种情况下,可以在不考虑形成其他晶圆的特征的热积存的情况下,形成各自晶圆中的特征。

4、上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文揭示的概念与特定实施例可做为修改或设计其它结构或过程而实现与本公开相同的目的。本公开所属技术领域中技术人员亦应了解,这类等效建构无法脱离权利要求所界定的本公开的构思和范围。

技术特征:

1.一种半导体元件,包括:

2.如权利要求1所述的半导体元件,其中该半导体层包括具有该第三掺杂区,具有该第一导电类型,且该第二掺杂区设置于该第一掺杂区与该第三掺杂区之间。

3.如权利要求2所述的半导体元件,其中该字元线的一第一垂直长度实质上等于该半导体层的该第二掺杂区的一第二垂直长度。

4.如权利要求2所述的半导体元件,还包括:

5.如权利要求4所述的半导体元件,还包括:

6.如权利要求5所述的半导体元件,其中该半导体连接结构具有该第一导电类型。

7.如权利要求5所述的半导体元件,其中该半导体连接结构连接到该半导体层的该第一掺杂区。

8.如权利要求2所述的半导体元件,还包括:

9.一种半导体元件,包括:

10.如权利要求9所述的半导体元件,其中该多个半导体层中的该至少一者包括具有一第二导电类型的一第二掺杂区,且该第二导电类型不同于该第一导电类型,并且该第一掺杂区与该半导体连接结构接触。

11.如权利要求10所述的半导体元件,其中该多个字元线中的每一个的一第一垂直长度实质上等于该第二掺杂区的一第二垂直长度。

12.如权利要求9所述的半导体元件,其中该半导体连接结构具有该第一导电类型。

13.如权利要求9所述的半导体元件,其中该掺杂物扩散层通过该半导体连接结构与该位元线分开。

14.如权利要求10所述的半导体元件,还包括:

15.如权利要求9所述的半导体元件,其中该字元线通过该掺杂物扩散层与该半导体连接结构间隔开其。

16.如权利要求10所述的半导体元件,其中该多个半导体层中的每一个都包括具有该第一导电类型的一第三掺杂区,并且该第二掺杂区设置于该第一掺杂区与该第三掺杂区之间。

17.如权利要求16所述的半导体元件,其中该第一掺杂区的一掺杂物与该第三掺杂区的一掺杂物不同。

18.如权利要求9所述的半导体元件,其中该半导体连接结构具有与该多个半导体层的该第一掺杂区中的该掺杂物相同的掺杂物。

技术总结

本申请提供一种半导体元件。该半导体元件包括一基底、一位元线、一半导体层及一字元线。该位元线设置于该基底上。该半导体层设置于该位元线上。该字元线邻接该半导体层。该字元线具有面向该基底的一下表面及与该下表面相对的一上表面。该半导体层包括具有一第一导电类型的一第一掺杂区及与该第一导电类型相反的一第二导电类型的一第二掺杂区。该第一掺杂区设置于该第二掺杂区与该位元线之间。该第一掺杂区与该第二掺杂区之间的第一边界实质上与该字元线的该下表面对齐。该第一掺杂区的一掺杂物与该第三掺杂区的一掺杂物不同。该第二掺杂区与一第三掺杂区之间的一第二边界实质上与该字元线的该上表面对齐。

技术研发人员:丘世仰

受保护的技术使用者:南亚科技股份有限公司

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!