延时箝位电路和延时箝位方法与流程

本技术涉及数据传输,具体涉及一种延时箝位电路和延时箝位方法。

背景技术:

1、目前常见的集成电路中通常采用cmos器件进行信号传递,由于mos管的实际导通特性随pvt(工艺角process corner、电压voltage、温度temperature)的变化较大,使得信号传递时的tpd(传输延迟时间,propagation delay time)随pvt变化较大。当pvt波动较大时,信号的传输延迟时间也波动较大,从而信号会过早或过晚到达,导致超出其他子模块的接收、采样范围,从而丢失信号或造成周期错乱、错误控制其他子模块的时序等问题。而为了减小tpd随pvt的波动,可以采用串联电阻的方法,电阻占总导通电阻的比重越大,得到的tpd随pvt的变化越小。但是这种方法对电路的速度牺牲较大,在tpd仍有增大空间时才可采用,使用场景受限。

2、因此目前采用mos管传递信号数据时,信号的传输延迟时间随pvt工艺角变化较大,没有明确的边界,难以把控,信号传输误差大。

技术实现思路

1、为了解决上述技术问题,本技术提供了一种延时箝位电路和延时箝位方法。

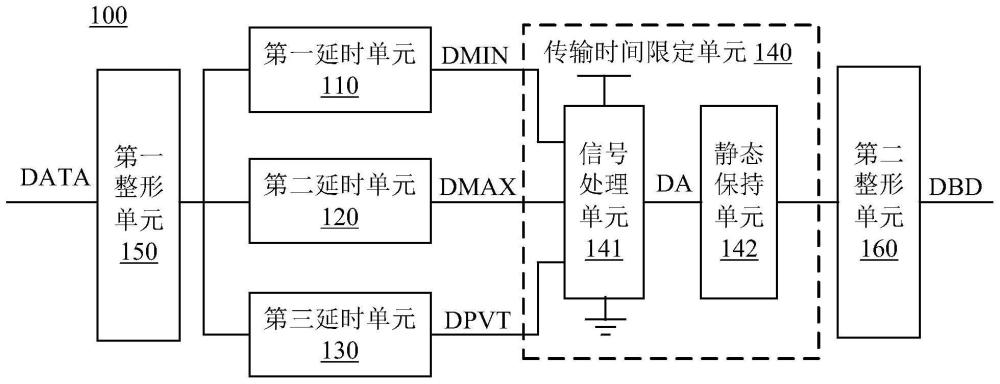

2、根据本发明的一方面,提供一种延时箝位电路,用于对原始数据信号进行延时,其中,所述延时箝位电路包括:第一延时单元,接收所述原始数据信号,将其延时固定的第一时间后输出为第一延时信号;第二延时单元,接收所述原始数据信号,将其延时固定的第二时间后输出为第二延时信号;第三延时单元,接收所述原始数据信号,将其延时自适应变化的第三时间后输出为第三延时信号;以及传输时间限定单元,连接所述第一延时单元、所述第二延时单元和所述第三延时单元,对所述第一延时信号、所述第二延时信号和所述第三延时信号进行信号处理后输出为传输延时信号,其中,所述第二时间大于所述第一时间,所述传输延时信号相较于所述原始数据信号的延时时间处于所述第一时间和所述第二时间之间。

3、可选地,所述第三时间与pvt工艺角相关,且所述第三时间随所述pvt工艺角自适应变化。

4、可选地,所述第三时间小于所述第一时间时,所述延时时间为所述第一时间;所述第三时间大于所述第一时间且小于所述第二时间时,所述延时时间为所述第三时间;所述第三时间大于所述第二时间时,所述延时时间为所述第二时间。

5、可选地,所述传输时间限定单元包括:信号处理单元,连接在供电端和接地端之间,从输入端接收所述第一延时信号、所述第二延时信号和所述第三延时信号,同时对所述第一延时信号、所述第二延时信号和所述第三延时信号的电平状态进行逻辑运算,从输出端输出中间信号;以及静态保持单元,连接所述信号处理单元的输出端,接收所述中间信号并将其电平状态翻转后输出为传输延时信号。

6、可选地,所述信号处理单元包括:并联在所述供电端和所述输出端之间的第一支路和第二支路,所述第一支路接收所述第一延时信号和所述第三延时信号,所述第二支路接收所述第一延时信号和所述第二延时信号;以及并联在所述接地端和所述输出端之间的第三支路和第四支路,所述第三支路接收所述第一延时信号和所述第三延时信号,所述第四支路接收所述第一延时信号和所述第二延时信号,

7、其中,所述供电端和所述输出端之间的支路与所述接地端和所述输出端之间的支路不能同时导通。

8、可选地,所述第一支路和/或所述第二支路导通时,所述传输延时信号的电平状态为低电平;所述第三支路和/或所述第四支路导通时,所述传输延时信号的电平状态为高电平。

9、可选地,所述信号处理单元包括依次串联连接在所述供电端和所述接地端之间的第一晶体管、第二晶体管、第三晶体管和第四晶体管,所述第二晶体管和所述第三晶体管的连接节点为第一节点,所述第一节点连接至所述信号处理单元的输出端,所述信号处理单元还包括第五晶体管和第六晶体管,所述第五晶体管并联在所述第二晶体管两端,所述第六晶体管并联在所述第三晶体管两端。

10、可选地,所述第一晶体管、所述第二晶体管和所述第五晶体管为pmos管,所述第三晶体管、所述第四晶体管和所述第六晶体管为nmos管,且所述第一晶体管和所述第四晶体管接收所述第一延时信号,所述第二晶体管和所述第三晶体管接收所述第三延时信号,所述第五晶体管和所述第六晶体管接收所述第二延时信号。

11、可选地,所述静态保持单元包括首尾相连的第一反相器和第二反相器,所述第一反相器的输入端和所述第二反相器的输出端的公共节点为第二节点,所述第一反相器的输出端和所述第二反相器的输入端的公共节点为第三节点,所述静态保持单元从所述第三节点上输出所述传输延时信号。

12、可选地,还包括:第一整形单元,连接在所述第一延时单元、所述第二延时单元和所述第三延时单元的输入端,接收所述原始数据信号,并将其整形为第一整形信号后输出至所述第一延时单元至所述第三延时单元,其中,所述第一整形信号相较所述原始数据信号的电平状态维持时间增大。

13、可选地,还包括:第二整形单元,连接在所述传输时间限定单元的输出端,接收所述传输延时信号,并将其整形为第二整形信号后输出,其中,所述第二整形信号相较所述传输延时信号的电平状态维持时间减小。

14、根据本发明的另一方面,提供一种延时箝位方法,应用在上述所述的延时箝位电路中,用于对原始数据信号进行延时,其中,所述延时箝位方法包括:将所述原始数据信号分别延时第一时间、第二时间和第三时间后输出为第一延时信号、第二延时信号和第三延时信号;以及对所述第一延时信号、所述第二延时信号和所述第三延时信号的电平状态同时进行逻辑处理后输出为传输延时信号,其中,所述第一时间和所述第二时间均为固定时间,所述第三时间为自适应变化的时间,所述第二时间大于所述第一时间,所述传输延时信号相较于所述原始数据信号的延时时间处于所述第一时间和所述第二时间之间。

15、本发明提供的延时箝位电路和延时箝位方法,设置了三个延时单元分别对原始数据信号进行不同时间的延时,再经由传输时间限定单元处理后输出为传输延时信号,该传输延时信号相对原始数据信号的传输延迟时间处于第一时间和第二时间之间。即延时箝位电路为数据的传输延时设置了边界,对延时的上界和下界进行了钳位,使延时时间有最大值和最小值,这样基本可以避免数据传输偏差,提升数据的传输精度。

16、进一步地,第三时间与pvt工艺角相关,随pvt工艺角变化,而当第三时间小于第一时间时,传输延迟时间最小为第一时间,此时延时箝位电路仅有延时下界的箝位功能;当第三时间大于第一时间且小于第二时间时,传输延迟时间随第三时间自适应变化,此时延时箝位电路同时具有延时下界与上界的箝位功能;当第三时间大于第二时间时,传输延时时间最大为第二时间,此时延时箝位电路仅有延时上界的箝位功能。那么,传输延迟时间随pvt变化的波动幅度也被限制在第一时间和第二时间之间。并且,在第一时间和第二时间形成的时间段之内,传输延迟时间随pvt变化显著,在这个时间段之外,传输延迟时间几乎不受pvt影响。保证了数据传输在不同pvt下的精度和准确性。

17、进一步地,设置了第一整形单元和第二整形单元,在原始传输数据经过处理前将其电平状态维持时间增大,以适应数据处理的时间,而在数据处理结束之后,又将传输延时信号的电平状态维持时间减小,使其恢复为原来的维持时间,适应后续电路需求。更进一步避免传输中的数据误差,保证数据传输精度。

18、应当说明的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本发明。

- 还没有人留言评论。精彩留言会获得点赞!