基于亚采样的宽调谐范围低参考杂散整数分频频率合成器

本发明属于电子,具体涉及一种基于亚采样的宽调谐范围低参考杂散整数分频频率合成器。

背景技术:

1、现代无线通讯收发系统需支持多频段通讯协议,软件定义无线电(sdr)通过软件编程重新配置硬件以同时满足多种无线通讯标准。频率综合器作为sdr无线收发系统中最为重要的模块,它直接决定着系统的功耗、相位噪声和误码率等性能指标。基于锁相环(pll)的频率综合器由于具有结构简单、输出频谱纯度高、相位噪声低和参考杂散小等优点,是无线收发机中常用来产生所需载波信号的技术。近年来,随着毫米波无线通讯的发展,研究超低抖动(<100fs)的高频时钟已成为热点。

2、到目前为止,已经开发了多种锁相环架构。基于电荷泵的ii型pll是现在的主流架构,其相位噪声主要分为两部分:带内主导的环路噪声和带外主导的压控振荡器(vco)噪声。在经典pll中,由于反馈路径中分频比n的存在,电荷泵和分频器的噪声转换到pll输出端时被乘以n2,使其成为限制pll实现低相位噪声的瓶颈,这在高分频比的情况下尤为突出。基于电压采样的无分频亚采样pll(sspll)架构消除了反馈分频器的噪声,同时利用高鉴相增益(kpd)抑制电荷泵和相位检测器的噪声,实现低抖动的同时降低功耗,更适用于产生高频和宽工作范围的低抖动时钟。然而,在sspll中,低频参考时钟(ref)直接采样vco的输出电压,周期性的电容扰动、时钟馈通以及电荷注入均会引入参考杂散。此外,由于锁定范围较窄并且需要锁频环路辅助,sspll的锁定速度相比于经典pll较慢。

3、近十年来,国内外的研究人员提出了诸多抑制参考杂散和加快锁定的方法。其中xiang gao等人在文献“spur reduction techniques for phase-locked loopsexploiting a sub-sampling phase detector”中系统分析了参考杂散产生的机理,对于二进制移频键控(bfsk)效应引起的参考杂散,利用dummy采样模块来使vco的输出负载保持恒定,并使用延迟电路调节占空比,使得bfsk效应被抑制。然而,此技术无法完全消除由于工艺失配带来的电容容值误差,小的采样电容可以抑制bfsk效应,但会增加采样器的噪声,恶化抖动性能。对于由电荷注入和电荷分享效应引起的参考杂散,采用亚采样延时锁相环(ssdll)调节非采样沿与vco输出信号过零点保持一致,可以达到抑制的效果。但是,ssdll中的环路滤波器将占用较大的芯片面积。zunsong yang等人在文献“a25.4-to-29.5ghz10.2mw isolated sub-sampling pll achieving-252.9db jitter-power fom and-63dbcreference spur”中提出了栅隔离采样技术,以增加vco和sspd之间的隔离,从而抑制参考杂散。然而,较低的相位噪声需要较大的晶体管尺寸,栅电容的变化仍会周期性地调制vco的负载,同时较大的栅电容还会加剧时钟馈通和电荷注入的影响。

4、为了减少环路锁定时间,目前使用的fll通过比较传递频率信息的两个脉冲宽度,避免生成不准确的死区控制信号,从而加速锁定。但是,该方法增加了电路的复杂性,且改进效果不明显。另一种基于正交亚采样鉴相器的死区自动控制技术,减少传统fll死区导致的锁定时间。然而,该方法需要vco产生四相信号,对lc-vco的设计提出了新的要求。

技术实现思路

1、本发明所要解决的技术问题在于针对上述现有技术中的不足,提供一种基于亚采样的宽调谐范围低参考杂散整数分频频率合成器,用于解决亚采样锁相环参考杂散大及锁定时间长的技术问题。

2、本发明采用以下技术方案:

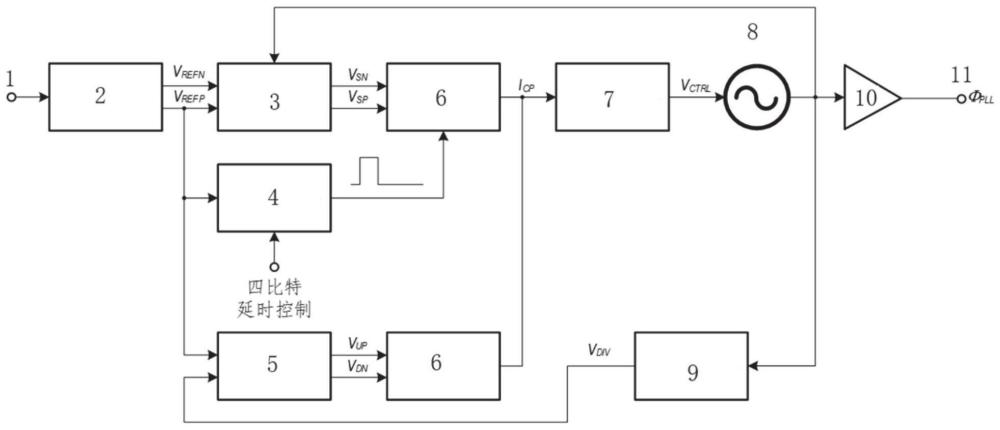

3、一种基于亚采样的宽调谐范围低参考杂散整数分频频率合成器,包括参考时钟缓冲器,参考时钟缓冲器的输入端连接晶振信号输入端,输出端分别连接随机采样鉴相器、脉冲产生器和鉴频鉴相器与死区控制模块的输入端,随机采样鉴相器、脉冲产生器和鉴频鉴相器与死区控制模块的输出端经电压电流转换模块和低通滤波器连接宽调谐压控振荡器的输入端,宽调谐压控振荡器的输出端分三路,第一路连接随机采样鉴相器,第二路经多模分频器连接至鉴频鉴相器与死区控制模块的输入端,第三路经输出缓冲器连接载波信号输出端;脉冲产生器连接延时控制端。

4、优选地,随机采样鉴相器对vco的差分输出信号vcop和vcon连接采样开关管的漏端进行差分采样,每个采样部分均包含主采样支路和辅助采样支路,主采样支路由ref信号作为采样开关管的栅端控制信号,辅助采样支路由信号作为采样开关管的栅端控制信号;在差分采样和辅助支路采样的基础上,将采样电容拆分成多个电容阵列,通过随机数生成模块产生的信号控制电容的随机接入。

5、更优选地,随机采样鉴相器中,采样开关管源端分别与输出信号端及采样电容阵列相连,采样电容c1-40分别与开关管m1-40漏端相连,采样开关管m1-40的源端接地;

6、信号分别连接到d触发器dfq1、dfq2、……dfq20的时钟输入端,d触发器dfq1~dfq19的正向时钟输出端信号q1~q19分别连接到后续的d触发器dfq2~dfq20的数据输入端,第二十d触发器dfq20的数据输出端和同或门xnor1的一个输入端相连,第十四d触发器dfq14的数据输出端和同或门xnor1的另一个输入端相连,同或门xnor1的输出端与异或门xor1的一个输入端相连,第七d触发器dfq7的数据输出端和异或门xor1的另一个输入端相连,异或门的输出端与第一d触发器dfq1的数据输入端相连。d触发器dfq1~dfq20的数据输出端信号q1~q20分别与开关管m1-10和m21-30的栅端相连,d触发器dfq1~dfq20的反向数据输出端信号分别与开关管m11-20和m31-40的栅端相连;

7、随机采样鉴相器在工作时,在参考时钟的下降沿处为线性反馈移位寄存器输入时钟信号,线性反馈移位寄存器由20个d触发器和一个异或门和同或门级联组成,在参考时钟的下降沿,线性反馈移位寄存器产生伪随机信号q1~q20,随机序列的周期数为219。

8、更优选地,当参考时钟上升沿来临时,压控振荡器的差分输出信号vcop和vcon分别由主支路的采样管进行采样,采样电容上极板保存上升沿瞬间的电压信息vsp并传递给电压-电流转换模块,辅助支路的采样管闭合,压控振荡器的输出接到辅助支路的电容阵列上;

9、当参考时钟的下降沿来临时,主支路的采样管进入跟踪状态,压控振荡器的输出接到主支路的电容阵列上,辅助支路将电压信息vsp_d传递给辅助的电压电流转换模块。

10、优选地,多模分频器包括2个基于etspc结构的2/3预分频器、2个采样静态cmos逻辑结构的2/3预分频器、1个二输入多路选择器、1个缓冲器和5个d触发器,单相时钟输入端ck与第一除2/3预分频器ediv1的第一输入端相连接,第一d触发器dff1的输出端与第一除2/3预分频器ediv1的第二输入端相连接,第一除2/3预分频器ediv1的第一输出端与第二除2/3预分频器ediv2的第一输入端相连接,第一除2/3预分频器ediv1的第二输出端处于开路状态;

11、第二d触发器dff2的输出端与第二除2/3预分频器ediv2的第二输入端相连接,第二除2/3预分频器ediv2的第一输出端与第一静态除2/3分频器div1的第一输入端相连接,第二除2/3预分频器ediv2的第二输出端与第一除2/3预分频器ediv1的第三输入端相连接;

12、第三d触发器dff3的输出端与第一静态除2/3分频器div1的第二输入端相连接,第一静态除2/3分频器div1的第一输出端与第二静态除2/3分频器div2的第一输入端相连接,第一静态除2/3分频器div1的第二输出端处于开路状态,第一静态除2/3分频器div1的第三输出端分别与第二除2/3预分频器ediv2的第三输入端,第一缓冲器buf1的输入端及第五d触发器dff5的第一输入端相连接;

13、第四d触发器dff4的输出端与第二静态除2/3分频器div2的第二输入端相连接,第二静态除2/3分频器div2的第一输出端与处于开路状态,使能信号en与第二静态除2/3分频器div2的第二输出端及第一多路选择器mux1的第二输入端相连接,第二静态除2/3分频器div2的第三输出端与第一多路选择器mux1的第三输入端相连接;

14、电源电压信号vdd与第一多路选择器mux1的第一输入端相连接,第一多路选择器mux1的输出端与第一除2/3预分频器ediv1的第三输入端相连接;第一缓冲器buf1的输出端分别与第一d触发器dff1、第二d触发器dff2、第三d触发器dff3和第四d触发器dff4的第二输入端相连接;第一d触发器dff1、第二d触发器dff2、第三d触发器dff3、第四d触发器dff4的第一输入端分别与分频比控制信号div0-3相连接;单相时钟输入端ck与第五d触发器dff5的第二输入端相连接,第五d触发器dff5的第一输出端与单相时钟输出端cko相连接。

15、更优选地,2/3预分频器结构包括3个d触发器、2个与门和一个或非门,前两级预分频器的d触发器采用etspc结构,时钟输入端cki与下降沿有效的触发器dln1的时钟输入端、第六d触发器dff6的时钟输入端及第七d触发器dff7的时钟输入端相连接,下降沿有效的触发器dln1的输出端与控制输出端mo及第一与门and1的一个输入端相连接,第一与门and1的另一个输入端与第一控制输入端mc相连接,第一与门and1的输出端与第六d触发器dff6的数据输入端相连接,第六d触发器dff6的输出端与或非门nor1的一个输入端相连接,或非门nor1的输出端与第七d触发器dff7的数据输入端相连接,第七d触发器dff7的输出端与时钟输出端cko、或非门nor1的另一个输入端及第二与门and2的一个输入端相连接,第二与门and2的另一个输入端与第二控制输入端mi相连接,第二与门and2的输出端与下降沿有效的触发器dln1的数据输入端相连接。

16、更优选地,控制输入端mi和mc共同控制2/3分频器的除2和除3状态;当mi为低电平时,电路始终进行2分频;当mi为高电平、mc为低电平时,电路进行2分频;当mi和mc均为高电平时,电路进行3分频。

17、优选地,鉴频鉴相器与死区控制模块包括4个dff、2个与门、1个与非门和4个延时单元,参考时钟信号与分频信号分别作为时钟输入dff1和dff2中,同时将对应的延迟信号输入dff3和dff4中;

18、若ref信号和div信号的相位差小于del1和del2,则当dff3和dff4的时钟信号上升沿到来前,dff1与dff2的输出信号q全部复位而置零,此时输出信号up和dn全部为0,鉴频鉴相器处于死区之内,锁频环路被关闭,不对低通滤波器输出电流。

19、更优选地,当ref信号相位超前div信号大于del3,则dff3的时钟信号上升沿到来时,dff1的输出信号为高电平,dff3的输出信号为高电平,与del3的信号做与逻辑后输出为up信号。

20、更优选地,鉴频鉴相器与死区控制模块的的死区宽度由del1和del2决定,实现[-π,π]内可调,死区持续时间与ref和div的相位差以及del3和del4有关。

21、与现有技术相比,本发明至少具有以下有益效果:

22、一种基于亚采样的宽调谐范围低参考杂散整数分频频率合成器,主环路中,外部晶振信号通过参考时钟缓冲器被整形成差分方波信号vrefn和vrefp,vrefn和vrefp进入随机采样鉴相器中采样宽调谐压控振荡器的输出信号并生成电压信号vsn和vsp,vsn和vsp进入电压-电流转换模块分别控制电荷泵的充电尾管和放电尾管,产生输出电流icp接入低通滤波器中转换为平稳的电压信号vctrl,vctrl再控制压控振荡器的振荡频率,最终通过输出缓冲器输出到载波信号输出端;脉冲产生器产生窄脉冲信号用于调节电路的环路参数;在辅环路中,压控振荡器的输出信号经过多模分频器产生与参考信号vrefp频率相近的信号vdiv,然后与vrefp在鉴频鉴相器与死区控制中鉴别相位差,产生电荷泵控制信号vup和vdn,转换为电流后输入低通滤波器,能够降低参考杂散,并且缩短锁定时间。

23、进一步的,本发明采用的随机采样鉴相器在差分采样和辅助支路采样的基础上,将采样电容拆分成多个电容阵列,通过随机数生成模块产生的信号控制电容的随机接入,在保持同时接入电路的电容数量一定的情况下,显著降低由工艺误差引起的参考杂散。同时,由于采样点容容值并没有过大或过小,鉴相器的面积在足够小的同时能够保持较低的相位噪声。

24、进一步的,本发明采用的线性反馈移位寄存器结构简单,能够有效地产生较长序列的伪随机数信号,异或门和同或门的反馈信号能保证电路不处于全“0”或全“1”的锁死状态,同时,该结构全由数字电路组成,可靠性强,工艺可移植性强,功耗很低。

25、进一步的,本发明中的参考时钟上升沿和下降沿控制采样管在一个时钟周期内交替轮流导通,保证了压控振荡器(vco)的输出负载始终与一个采样电容相连接,减小了由于输出负载切换而引起的参考杂散。

26、进一步的,基于2/3预分频器的多模分频器,使其分频范围不再局限于2n-1~2n-1,同时消除了由于多级级联而累积的相位噪声以及控制信号不同步而造成分频错误。此外,本发明改进了前两级预分频器的内部结构,使其能处理较高频率的时钟信号,并在各个工艺角下均能正常工作。

27、进一步的,本发明中的鉴频鉴相器与死区控制模块能够辅助亚采样锁相环锁定在正确的频率,帮助亚采样锁相环的快速锁定,在锁定后能够实时监测频率情况,同时关闭对环路的电流输入,使其对亚采样锁相环的相位噪声及功耗无影。

28、进一步的,本发明改进了鉴频鉴相器的死区控制逻辑,使其对分频信号的占空比不再有严格的要求。通过对死区的范围进行调节,使其相位误差信息的延迟减小,并产生较为线性的增益响应,减少亚采样锁相环的锁定时间。

29、综上所述,本发明对传统的亚采样锁相环结构和模块进行一定的改进,在不牺牲功耗和面积的前提下减小了由于采样电容工艺失配引起的参考杂散,同时加快了环路的锁定速度。

30、下面通过附图和实施例,对本发明的技术方案做进一步的详细描述。

- 还没有人留言评论。精彩留言会获得点赞!