一种防串口抖动干扰电路及控制方法与流程

本发明涉及串口,尤其涉及一种防串口抖动干扰电路及控制方法。

背景技术:

1、本部分的陈述仅仅是提供了与本发明相关的背景技术信息,不必然构成在先技术。

2、串口数据一般是由起始位、数据位、校验位和停止位构成。串口起始位是指在串口通信中,数据传输的起始标志位。在串口通信中,数据是以二进制的形式传输的,因此需要一个特殊的标志位来表示数据的起始位置。串口起始位必须是持续一个bit时间的逻辑0电平,它标志传输一个字符的开始。而实际使用中,当串口设备接入的时候,会发生物理抖动。从而导致在默认的高电平状态中,会出现短小的干扰低电平,这个干扰电平会被误认为串口数据的起始位。这也就是串口抖动干扰,如图1所示。

技术实现思路

1、为了解决上述背景技术中存在的技术问题,本发明提供一种防串口抖动干扰电路及控制方法,本发明通过对信号的延迟输出,规避干扰信号,实现了对串口抖动的消抖功能。

2、为了实现上述目的,本发明采用如下技术方案:

3、本发明的第一个方面提供一种防串口抖动干扰电路。

4、一种防串口抖动干扰电路,包括:延时模块、快速充电模块和快速放电模块,所述延时模块分别连接快速充电模块和快速放电模块;

5、当设备串口起始位出现时,输入信号跳变为低电平,延迟模块中的电容放电,当放电电压小于设定值时,使输出信号延迟变为低电平,识别起始位信号,同时低电平的输出信号启动快速放电模块,对电容进行快速放电至完全放电完成;

6、当设备输入信号由低电平再次跳变为高电平时,电容开始充电,充电过程中输出信号维持低电平,当充电电流满足设定条件时,使输出信号变为高电平,同时高电平的输出信号启动快速充电模块,对电容进行快速充电。

7、进一步地,当设备上电时,输入信号一直处于高电平,输出信号也保持高电平,当出现干扰信号时,输入信号跳变为低电平,电容开始放电,使输出信号一直维持在高电平;其中,干扰信号低电平持续时间远小于电容放电时间。

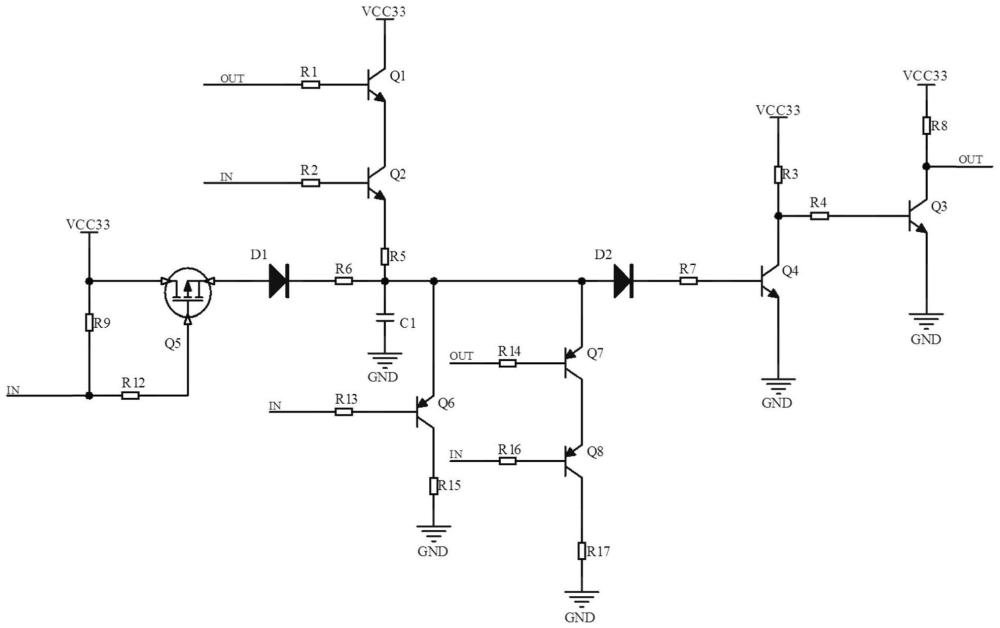

8、进一步地,所述快速充电模块包括第一三极管和第二三极管,所述第一三极管的基极通过第一电阻连接out端口,所述第一三极管的集电极连接电源端,所述第一三极管的发射极连接第二三极管的集电极,所述第二三极管的基极通过第二电阻连接in端口,所述第二三极管的发射极连接第五电阻的一端,第五电阻的另一端分别连接延时模块和电容的正极,电容的负极接地。

9、进一步地,所述延时模块包括mos管、第一二极管、第二二极管、第三三极管和第四三极管,所述mos管的栅极分别连接in端口和漏极,所述漏极连接电源端,所述mos管的源极连接第一二极管的正极,所述第一二极管的负极连接第六电阻的一端,第六电阻的另一端连接第二二极管的正极,第二二极管的负极连接第七电阻的一端,第七电阻的另一端连接第四三极管的基极,第四三极管的发射极接地,第四三极管的集电极分别连接电源端和第三三极管的基极,第三三极管的集电极分别连接电源端和out端口,第三三极管的发射极接地。

10、更进一步地,所述mos管的栅极连接第十二电阻的一端,第十二电阻的另一端分别连接in端口和第九电阻的一端,第九电阻的另一端分别接电源端和漏极。

11、更进一步地,所述第四三极管的集电极分别连接第三电阻的一端和第四电阻的一端,第三电阻的另一端连接电源端,第四电阻的另一端连接第三三极管的基极,第三三极管的集电极分别连接out端口和第八电阻的一端,第八电阻的另一端连接电源端。

12、进一步地,所述快速放电模块包括mos管、第六三极管、第七三极管和第八三极管,所述mos管的栅极连接第十二电阻的一端,第十二电阻的另一端分别连接in端口和第九电阻的一端,第九电阻的另一端分别接电源端和漏极,所述mos管的源极连接第一二极管的正极,所述第一二极管的负极连接第六电阻的一端,第六电阻的另一端分别连接第六三极管的发射极和第七三极管的发射极,第六电阻的基极通过第十三电阻连接in端口,第六三极管的集电极通过第十五电阻接地;第七三极管的基极通过第十四电阻连接out端口,第七三极管的集电极连接第八三极管的发射极,第八三极管的基极通过第十六电阻连接in端口,第八三极管的集电极通过第十七电阻接地。

13、更进一步地,第六电阻的另一端分别连接第五电阻的另一端和电容的正极。

14、本发明的第二个方面提供一种防串口抖动干扰电路控制方法。

15、一种防串口抖动干扰电路控制方法,采用第一个方面所述的防串口抖动干扰电路,包括:

16、当设备串口起始位信号出现时,输入信号跳变为低电平,电容起先进行缓慢放电,缓慢放电时长t1,当放电电压低于第四三极管的开启电压后,第四三极管截止,第三三极管导通,输出信号延迟变为低电平,识别起始位信号;同时,低电平的输出信号启动快速放电模块,对电容进行快速放电至完全放电完成;

17、当设备输入信号由低电平再次跳变为高电平时,电容开始充电,充电时长为t2,这期间输出信号维持低电平;当充电电流使第四三极管导通后,第三三极管截止,输出信号变为高电平;同时,高电平的输出信号启动快速充电模块,对电容进行快速充电,时长为t4。

18、进一步地,所述控制方法还包括:

19、当设备上电后,输入信号一直处于高电平,输出信号也保持高电平;当出现干扰信号时,输入信号跳变为低电平,电容开始缓慢放电,缓慢放电时长t1,这段时间内,放电电流保证第四三极管导通,第三三极管截止,输出信号一直维持在高电平,干扰信号低电平持续时间为t0,t0<<t1。

20、与现有技术相比,本发明的有益效果是:

21、本发明通过对信号的延迟输出,规避干扰信号,实现了对串口抖动的消抖功能。

22、本发明中的快速充电模块和快速放电模块工作时,在每次串口信号高电平向低电平跳变时,控制电容c1为满电,而信号在低电平向高电平跳变时,控制电容c1完全放电完成。即每次电平转换都是从满到0或从0到满,从而保证延迟后信号的准确性和稳定性。

技术特征:

1.一种防串口抖动干扰电路,其特征在于,包括:延时模块、快速充电模块和快速放电模块,所述延时模块分别连接快速充电模块和快速放电模块;

2.根据权利要求1所述的防串口抖动干扰电路,其特征在于,当设备上电时,输入信号一直处于高电平,输出信号也保持高电平,当出现干扰信号时,输入信号跳变为低电平,电容开始放电,使输出信号一直维持在高电平;其中,干扰信号低电平持续时间远小于电容放电时间。

3.根据权利要求1所述的防串口抖动干扰电路,其特征在于,所述快速充电模块包括第一三极管和第二三极管,所述第一三极管的基极通过第一电阻连接out端口,所述第一三极管的集电极连接电源端,所述第一三极管的发射极连接第二三极管的集电极,所述第二三极管的基极通过第二电阻连接in端口,所述第二三极管的发射极连接第五电阻的一端,第五电阻的另一端分别连接延时模块和电容的正极,电容的负极接地。

4.根据权利要求1所述的防串口抖动干扰电路,其特征在于,所述延时模块包括mos管、第一二极管、第二二极管、第三三极管和第四三极管,所述mos管的栅极分别连接in端口和漏极,所述漏极连接电源端,所述mos管的源极连接第一二极管的正极,所述第一二极管的负极连接第六电阻的一端,第六电阻的另一端连接第二二极管的正极,第二二极管的负极连接第七电阻的一端,第七电阻的另一端连接第四三极管的基极,第四三极管的发射极接地,第四三极管的集电极分别连接电源端和第三三极管的基极,第三三极管的集电极分别连接电源端和out端口,第三三极管的发射极接地。

5.根据权利要求4所述的防串口抖动干扰电路,其特征在于,所述mos管的栅极连接第十二电阻的一端,第十二电阻的另一端分别连接in端口和第九电阻的一端,第九电阻的另一端分别接电源端和漏极。

6.根据权利要求4所述的防串口抖动干扰电路,其特征在于,所述第四三极管的集电极分别连接第三电阻的一端和第四电阻的一端,第三电阻的另一端连接电源端,第四电阻的另一端连接第三三极管的基极,第三三极管的集电极分别连接out端口和第八电阻的一端,第八电阻的另一端连接电源端。

7.根据权利要求1所述的防串口抖动干扰电路,其特征在于,所述快速放电模块包括mos管、第六三极管、第七三极管和第八三极管,所述mos管的栅极连接第十二电阻的一端,第十二电阻的另一端分别连接in端口和第九电阻的一端,第九电阻的另一端分别接电源端和漏极,所述mos管的源极连接第一二极管的正极,所述第一二极管的负极连接第六电阻的一端,第六电阻的另一端分别连接第六三极管的发射极和第七三极管的发射极,第六电阻的基极通过第十三电阻连接in端口,第六三极管的集电极通过第十五电阻接地;第七三极管的基极通过第十四电阻连接out端口,第七三极管的集电极连接第八三极管的发射极,第八三极管的基极通过第十六电阻连接in端口,第八三极管的集电极通过第十七电阻接地。

8.根据权利要求7所述的防串口抖动干扰电路,其特征在于,第六电阻的另一端分别连接第五电阻的另一端和电容的正极。

9.一种防串口抖动干扰电路控制方法,其特征在于,采用权利要求1-8任一项所述的防串口抖动干扰电路,包括:

10.根据权利要求9所述的防串口抖动干扰电路控制方法,其特征在于,所述控制方法还包括:

技术总结

本发明涉及串口技术领域,提供一种防串口抖动干扰电路及控制方法。所述电路,包括:延时模块、快速充电模块和快速放电模块,延时模块分别连接快速充电模块和快速放电模块;当设备串口起始位出现时,输入信号跳变为低电平,延迟模块中的电容放电,当放电电压小于设定值时,使输出信号延迟变为低电平,识别起始位信号,同时低电平的输出信号启动快速放电模块,对电容进行快速放电至完全放电完成;当设备输入信号由低电平再次跳变为高电平时,电容开始充电,充电过程中输出信号维持低电平,当充电电流满足设定条件时,使输出信号变为高电平,同时高电平的输出信号启动快速充电模块,对电容进行快速充电。

技术研发人员:王芳怡,马海涛,刘晓燕,马文英,吴修燕

受保护的技术使用者:神思电子技术股份有限公司

技术研发日:

技术公布日:2024/3/27

- 还没有人留言评论。精彩留言会获得点赞!