锁相装置的压控方法、锁相装置及芯片与流程

本发明涉及电子设备的,更具体地,涉及一种锁相装置的压控方法、锁相装置及芯片。

背景技术:

1、压控晶振是指在石英晶体谐振器的振荡回路中引入一个可调的变容二极管,通过压控电压改变回路中变容二极管的负载电容,从而谐振回路的谐振频率随之变化的目的。压控晶振广泛应用于通信,服务器等领域,在音视频领域控制接收端与发送端的同源也有涉及。在实际使用过程中,由于压控晶振外围器件性能参差不齐,在特定的滤波电路与反相器的组合下可以正常使用,但是在更为广泛灵活的应用场景中,通过快速改变压控电压,甚至出现停振输出的现象。虽然进一步调节滤波电路参数,可以避免停振的出现,但过度调节滞后超前滤波参数,会导致针对不同距离的同源过程出现同步死区,一直处于振荡的同源过程,无法稳定输出。

技术实现思路

1、本发明为克服上述在特定压控晶体使用过程中导致停振及无法稳定输出的的缺陷,提供一种锁相装置的压控方法、锁相装置及芯片,本发明采用的技术方案如下。

2、第一方面,本发明提供一种锁相装置的压控方法,包括:

3、接收鉴相器输出的表示相位差的相位差信号;

4、接收控制信号;

5、根据所述控制信号,生成激励调节信号;其中,所述激励调节信号用于输出给环路滤波器,让环路滤波器根据所述激励调节信号输出对应的压控电压,所述压控电压作用在压控振荡器,所述压控振荡器在不同的压控电压下,会处于不同的状态,所述压控振荡器的状态包括:正偏状态、负偏状态和跟随状态;

6、输出所述激励调节信号;

7、其中,所述根据所述控制信号,生成激励调节信号的过程,包括:

8、根据所述控制信号判断所述压控振荡器是否需要由正偏切换到其他状态或由负偏切换到其他状态;

9、在所述压控振荡器需要由正偏切换到其他状态或由负偏切换到其他状态时,生成要切换到的目标状态相对应的激励调节信号,并从状态切换节点开始,在对应的预设时长内,间歇性地生成所述要切换到的目标状态相对应的激励调节信号,其中,由正偏切换到其他状态对应的预设时长为第一时长,由负偏切换到其他状态对应的预设时长为第二时长;

10、所述根据所述控制信号,生成激励调节信号的过程,还包括:

11、根据所述控制信号判断所述压控振荡器是否处于跟随状态;

12、在所述压控振荡器处于跟随状态时,基于所述相位差信号生成所述激励调节信号。

13、在一种实施方式中,所述间歇性地生成所述要切换到的目标状态相对应的激励调节信号的过程,包括:

14、周期性输出所述要切换到的目标状态相对应的激励调节信号。

15、在一种实施方式中,所述间歇性地生成所述要切换到的目标状态相对应的激励调节信号的过程,包括:

16、在压控振荡器要由正偏切换到其他状态时,所述要切换到的目标状态相对应的激励调节信号为代表负偏的逻辑信号;

17、在压控振荡器要由负偏切换到其他状态时,所述要切换到的目标状态相对应的激励调节信号为代表正偏的逻辑信号。

18、在一种实施方式中,所述基于所述相位差信号生成所述激励调节信号的过程,包括:

19、在所述相位差信号为上升高电平时,在预设的第三时长内,减少高电平的输出时间,使电平上升过程中的高电平输出实际时长小于相位差信号的高电平应输出时长;

20、在所述相位差信号为下降低电平时,在预设的第四时长内,减少低电平的输出时间,使电平下降过程中的低电平输出实际时长小于相位差信号的低电平应输出时长。

21、在一种实施方式中,所述减少高电平的输出时间,使电平上升过程中的高电平输出实际时长小于相位差信号的高电平应输出时长的过程,包括:

22、控制各个周期内上升高电平输出的个数,其中,所述预设的第三时长包含若干个周期;

23、所述减少低电平的输出时间,使电平下降过程中的低电平输出实际时长小于相位差信号的低电平应输出时长的过程,包括:

24、控制各个周期内下降低电平输出的个数,其中,所述预设的第四时长包含若干个周期。

25、在一种实施方式中,所述减少高电平的输出时间,使电平上升过程中的高电平输出实际时长小于相位差信号的高电平应输出时长的过程,包括:

26、控制高电平上升过程中的电平输出脉冲的宽度;

27、所述减少低电平的输出时间,使电平下降过程中的低电平输出实际时长小于相位差信号的低电平应输出时长的过程,包括:

28、控制低电平下降过程中的电平输出脉冲的宽度。

29、第二方面,本发明提供一种锁相装置的压控方法,包括:

30、接收鉴相器输出的表示相位差的相位差信号;

31、接收控制信号;

32、根据所述控制信号,生成激励调节信号;其中,所述激励调节信号用于输出给环路滤波器,让环路滤波器根据所述激励调节信号输出对应的压控电压,所述压控电压作用于压控振荡器;

33、输出所述激励调节信号;

34、其中,所述根据所述控制信号,生成激励调节信号的过程,包括:

35、在所述相位差信号为上升高电平时,在预设的第五时长内,减少高电平的输出时间,使电平上升过程中的高电平输出实际时长小于相位差信号的高电平应输出时长;

36、在所述相位差信号为下降低电平时,在预设的第六时长内,减少低电平的输出时间,使电平下降过程中的低电平输出实际时长小于相位差信号的低电平应输出时长。

37、在一种实施方式中,所述减少高电平的输出时间,使电平上升过程中的高电平输出实际时长小于相位差信号的高电平应输出时长的过程,包括:

38、控制各个周期内上升高电平输出的个数,其中,所述预设的第五时长包含若干个周期;

39、所述减少低电平的输出时间,使电平下降过程中的低电平输出实际时长小于相位差信号的低电平应输出时长的过程,包括:

40、控制各个周期内下降低电平输出的个数,其中,所述预设的第六时长包含若干个周期。

41、在一种实施方式中,所述减少高电平的输出时间,使电平上升过程中的高电平输出实际时长小于相位差信号的高电平应输出时长的过程,包括:

42、控制高电平上升过程中的电平输出脉冲的宽度;

43、所述减少低电平的输出时间,使电平下降过程中的低电平输出实际时长小于相位差信号的低电平应输出时长的过程,包括:

44、控制低电平下降过程中的电平输出脉冲的宽度。

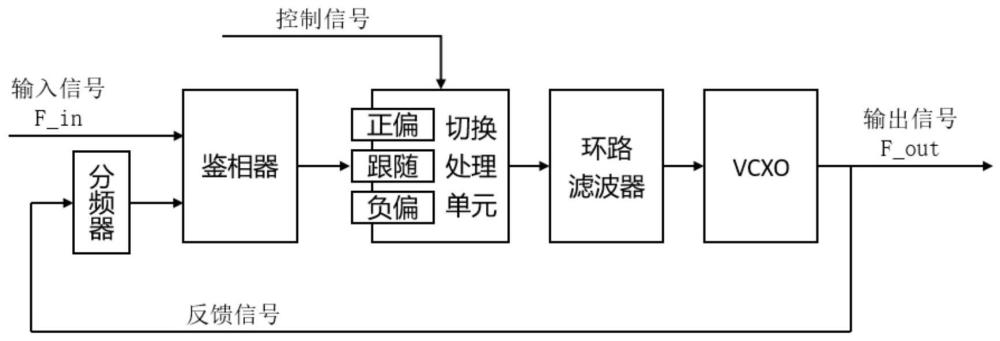

45、第三方面,本发明提供一种锁相装置,其特征在于,包括:

46、分频器,用于接收反馈信号,并对接收到的反馈信号进行分频,以形成与输入信号同频的分频后的反馈信号;

47、鉴相器,用于接收输入信号和所述分频后的反馈信号,比较二者之间的相位差,并输出一个表示相位差的相位差信号;

48、切换处理单元,连接于所述鉴相器,用于接收控制信号和鉴相器输出的相位差信号,并根据所述控制信号,生成激励调节信号;

49、环路滤波器,连接于所述切换处理单元,用于对所述激励调节信号进行滤波,输出压控电压;

50、压控振荡器,连接于所述环路滤波器,用于基于所述环路滤波器输出的所述压控电压生成输出信号和所述反馈信号;

51、其中,所述切换处理单元被配置为实施第一方面中的任一实施方式所述的锁相装置的压控方法。

52、第四方面,本发明提供一种锁相装置,其特征在于,包括:

53、分频器,用于接收反馈信号,并对接收到的反馈信号进行分频,以形成与输入信号同频的分频后的反馈信号;

54、鉴相器,用于接收输入信号和所述分频后的反馈信号,比较二者之间的相位差,并输出一个表示相位差的相位差信号;

55、切换处理单元,连接于所述鉴相器,用于接收鉴相器输出的相位差信号,并根据所述相位差信号,生成激励调节信号;

56、环路滤波器,连接于所述切换处理单元,用于对所述激励调节信号进行滤波,输出压控电压;

57、压控振荡器,连接于所述环路滤波器,用于基于所述环路滤波器输出的所述压控电压生成输出信号和所述反馈信号;

58、其中,所述切换处理单元被配置为实施第二方面中的任一实施方式所述的锁相装置的压控方法

59、第五方面,本发明提供一种芯片,包括处理器,所述处理器被调用用于执行前述任一实施方式所述的锁相装置的压控方法。

60、第六方面,本发明提供一种芯片,包括前述任一实施方式所述的锁相装置。

61、本发明中,在传统的锁相电路的基础上,对鉴相器输出的相位差信号进行调整干预,然后才将该经过调整的相位差信号送入环路滤波器,以使得经环路滤波器输出的压控电压能够平缓地上升或下降,从而避免了因快速改变压控电压造成压控振荡器出现停振输出等现象,解决了特定压控晶体使用过程中产生停振或无法稳定输出的问题。

- 还没有人留言评论。精彩留言会获得点赞!