延迟校准方法、发送端及源同步通信系统与流程

本发明涉及集成电路中的高速通信接口,尤其涉及一种延迟校准方法、发送端及源同步通信系统。

背景技术:

1、现有技术中,并行接口通过多个通道传输数据,接收侧采样数据,要求多个接收通道的到达时间在一个有效窗口,否则会出现采样错误。由于电路印制板互连线等差异,会出现各个到达时间不一致的情况,从而产生通道不对齐等情况。这时需要引入延迟对齐机制,来使通道对齐,保证传输正确。

2、现有的技术方案,主要是在环路中引入数控延迟单元来进行通道对齐,实现的过程也主要集中在接收侧进行。例如,第一种实现通道对齐的方案是通过预先定义的同步字实现,该方案主要在接收侧引入数控延迟单元,先实现位校正,然后通过发送预先定义好的同步字,调整接收侧的数控延迟单元的延迟值,来实现各通道的数据对齐功能。

3、第二种实现通道对齐的方案是基于读写训练延迟的闭环校准方法,具体为在时钟或者数据端添加可控延迟电路,通过读写反馈来搜索数据有效窗口的低值和高值,来调整时钟和数据的延迟。具体的工作过程:首先,数控延迟单元的延迟值设置为最小值,发送端发送一组数据到接收端,然后接收端再将发送的数据回传到发送端,回传的数据和原始数据进行比较,直到出现先数据差异和后数据一致的突变时,说明搜索到了数据有效窗口的左边界,记录此时的数控延迟单元的延迟控制值;然后,继续增加数控延迟单元的延迟值,直到出现先数据一致和数据差异的突变时,说明搜索到了数据有效窗口的右边界,记录此时的延迟值,然后左边界记录的延迟值和右边界记录的延迟值求平均,就是数控延迟单元的控制值。该方案的特点是调节过程周期较长,且需要双方都在同一个pad上包含收发电路,以保证数据的回传验证。

4、第三种实现通道对齐的方案是基于特定延迟的开环校准方法,具体为在数据或者时钟端添加一个固定延迟单元,固定延迟设置值通过预先的计算得到,特点是实现简单,但延迟确定后就难以再调节。

5、针对上述现有技术中的几种方案,其中第一种实现方案主要解决数控延迟单元在接收侧的情况,但数控延迟单元在发送侧时就无能为力,无法再进行通道的对齐过程;第二种实现方案的数控延迟单元主要在发送侧,可以解决数控延迟单元在发送侧的问题,但只能单工通信,无法双向同时通信来交换数据;第二种实现方案中,基于开环的数控延迟单元来实现通道对齐,需要预先设定延迟值,无后续校准功能,而该方案仅适合在低速,变化不大的场景使用。

6、因此,针对数控延迟单元在发送侧为主的校准流程中,尤其是双工通信时,现有技术中的方案缺乏有效的反馈机制以反映误码信息实现校准电路的校准。因此,如何能够解决数控延迟单元位于发送侧时的延迟校准成为本领域技术人员亟待解决的技术问题。

技术实现思路

1、本发明提供了一种延迟校准方法、发送端及源同步通信系统,解决相关技术中存在的数控延迟单元位于发送端时缺乏相应的延迟校准的问题。

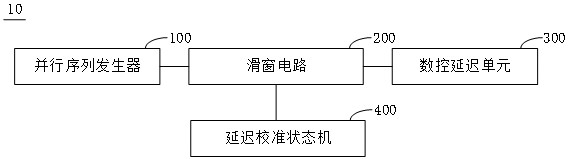

2、作为本发明的第一个方面,提供一种发送端,其中,包括:

3、并行序列发生器,用于在延迟校准状态机工作于位定时状态时产生第一校准码,以及在延迟校准状态机工作于字定时状态时产生第二校准码;

4、滑窗电路,用于对并行序列发生器产生的第二校准码产生可调延迟值;

5、数控延迟单元,用于对并行序列发生器产生的第一校准码产生可调延迟值;

6、延迟校准状态机,包括位定时状态和字定时状态,用于执行延时校准方法,其中,所述延时校准方法,包括:

7、在启动时,设置滑窗电路的初始延迟值和数控延迟单元的初始延迟值;

8、保持所述滑窗电路的初始延迟值不变,在确定并行序列检测器处于第一检测模式时,控制所述延迟校准状态机进入位定时状态,在所述位定时状态下,当所述延迟校准状态机根据并行序列检测器针对第一校准码产生的误码信息确定第一校准码与第一匹配码不匹配时,调整数控延迟单元的延迟值,直至根据并行序列检测器针对所述第一校准码产生的误码信息确定第一校准码与第一匹配码匹配且匹配结果保持稳定预设周期,将此时数控延迟单元对应的延迟值确定为第一匹配延迟值;所述并行序列检测器能够根据接收到的第一校准码产生第一匹配码;

9、保持所述数控延迟单元的延迟值维持在所述第一匹配延迟值,控制所述延迟校准状态机进入字定时状态,在确定所述并行序列检测器处于第二检测模式时,位于字定时状态下的延迟校准状态机根据并行序列检测器针对第二校准码产生的误码信息确定第二校准码与第二匹配码不匹配时,调整滑窗电路的延迟值,直至根据并行序列检测器针对第二校准码产生的误码信息确定第二校准码与第二匹配码匹配且匹配结果保持稳定预设周期,将此时滑窗电路的延迟值确定为第二匹配延迟值;所述并行序列检测器能够根据接收到的第二校准码产生第二匹配码;

10、控制源同步通信系统以发送端的数控延迟单元的可调延迟值为第一匹配延迟值,以及滑窗电路的可调延迟值为第二匹配延迟值工作,并控制所述延迟校准状态机退出位定时状态及字定时状态。

11、进一步地,所述滑窗电路包括多级级联连接的滑窗延迟单元,

12、每级滑窗延迟单元均包括d触发器和第一数据选择器,从第二级滑窗延迟单元开始,每级滑窗延迟单元的d触发器的输入端连接前一级滑窗延迟单元的d触发器的输出端,每级滑窗延迟单元的d触发器的输出端与同级的第一数据选择器的第一输入端连接,每级滑窗延迟单元的d触发器的时钟信号端用于输入时钟信号,

13、每级滑窗延迟单元的第一数据选择器的第二输入端连接前一级滑窗延迟单元的第一数据选择器的输出端,每级滑窗延迟单元的选择控制端用于输入延迟控制字信号,

14、其中,第一级滑窗延迟单元的d触发器的输入端和第一级滑窗延迟单元的第一数据选择器的第二输入端均用于输入序列发生器的输出信号,最后一级滑窗延迟单元的第一数据选择器的输出端用于输出滑窗电路的可调延迟值。

15、进一步地,所述数控延迟单元包括粗调电路和精调电路,所述粗调电路的输出端与所述精调电路的输入端连接,所述粗调电路的输入端为所述数控延迟单元的输入端,所述精调电路的输出端为所述数控延迟单元的输出端,

16、所述粗调电路用于在位定时状态时对初始延迟值进行第一延迟粒度计算,以获得第一粒度延迟值,其中所述第一粒度延迟值的计算公式为:

17、,

18、其中,表示第一粒度延迟值,表示粗调电路的固有延迟值,表示粗调电路的延迟控制码,表示粗调电路的延迟步进值;

19、所述精调电路用于在位定时状态时对所述第一粒度延迟值进行第二延迟粒度计算,以获得第二粒度延迟值,所述第一粒度延迟值的延迟粒度大于第二粒度延迟值的延迟粒度,其中所述第二粒度延迟值的计算公式为:

20、,

21、其中,表示第一粒度延迟值,表示精调电路的固有延迟值,表示精调电路的延迟控制字,表示精调电路的延迟步进值;

22、所述第一粒度延迟值和第二粒度延迟值之和为所述数控延迟单元的延迟值。

23、进一步地,所述粗调电路包括多级级联的粗调单元,每级粗调单元均包括第二数据选择器和延迟单元,每级延迟单元的输入端均连接前一级延迟单元的输出端,每级第二数据选择器的第一输入端均连接前一级第二数据选择器的输出端,每级第二数据选择器的第二输入端均连接同级的延迟单元的输出端;

24、第一级延迟单元的输入端和第一级第二数据选择器的第一输入端连接,且均为所述粗调电路的输入端;最后一级第二数据选择器的输出端为所述粗调电路的输出端;

25、所述精调电路包括多级级联的三态门阵列,从第二级三态门阵列开始,每级三态门阵列的输入端均连接前一级三态门阵列的输出端,第一级三态门阵列的输入端为所述精调电路的输入端,最后一级三态门阵列的输出端为所述精调电路的输出端;每级三态门阵列均包括多个输入端相连接以及输出端相连接的三态门。

26、进一步地,所述并行序列发生器包括n个级联的d触发器,用于生成prbs码;

27、当n为7时,所述prbs码为prbs7码,且prbs7码的生成多项式为x7 + x6+ 1,所述并行序列发生器包括7个级联的d触发器,该生成多项式表征:第六d触发器的输出端和第七d触发器的输出端进行异或运算后反馈至第一d触发器进行循环,直至第七d触发器输出所述prbs7码;

28、当n为9时,所述prbs码为prbs9码,且prbs9码的生成多项式为x9+ x5+ 1,所述并行序列发生器包括9个级联的d触发器,该生成多项式表征:第五d触发器的输出端和第九d触发器的输出端进行异或运算后反馈至第一d触发器进行循环,直至第九触发器输出所述prbs9码;

29、当n为15时,所述prbs码为prbs15码,且prbs15码的生成多项式为x15+ x14+ 1,所述并行序列发生器包括15个级联的d触发器,该生成多项式表征:第十四d触发器的输出端和第十五d触发器的输出端进行异或运算后反馈至第一d触发器进行循环,直至第十五d触发器输出所述prbs15码;

30、当n为23时,所述prbs码为prbs23码,且prbs23码的生成多项式为x23+ x18+ 1,所述并行序列发生器包括23个级联的d触发器,该生成多项式表征:第十八d触发器的输出端和第二十三d触发器的输出端进行异或运算后反馈至第一d触发器进行循环,直至第二十三d触发器输出所述prbs23码;

31、当n为31时,所述prbs码为prbs31码,且prbs31码的生成多项式为x31+ x28+ 1,所述并行序列发生器包括31个级联的d触发器,该生成多项式表征:第二十八d触发器的输出端和第三十一d触发器的输出端进行异或运算后反馈至第一d触发器进行循环,直至第三十一d触发器输出所述prbs31码。

32、作为本发明的另一个方面,提供一种源同步通信系统,其中,包括接收端和前文所述的发送端,所述发送端和接收端通信连接,

33、所述接收端至少包括并行序列检测器,所述并行序列检测器的码型配置与所述发送端的并行序列发生器的码型配置相同;

34、所述并行序列检测器能够检测所述发送端发出的第一校准码及第二校准码,并根据检测到的第一校准码或第二校准码生成误码信息。

35、进一步地,所述并行序列检测器包括多个级联的d触发器;

36、当并行序列发生器生成的prbs码为prbs7码时,所述并行序列检测器包括7个级联的d触发器,第六d触发器的输出端和第七d触发器的输出端进行异或运算后获得第一异或运算结果;

37、当并行序列发生器生成的prbs码为prbs9码时,所述并行序列检测器包括9个级联的d触发器,第五d触发器的输出端和第九d触发器的输出端进行异或运算后获得第一异或运算结果;

38、当并行序列发生器生成的prbs码为prbs15码时,所述并行序列检测器包括15个级联的d触发器,第十四d触发器的输出端和第十五d触发器的输出端进行异或运算后获得第一异或运算结果;

39、当并行序列发生器生成的prbs码为prbs23码时,所述并行序列检测器包括23个级联的d触发器,第十八d触发器的输出端和第二十三d触发器的输出端进行异或运算后获得第一异或运算结果;

40、当并行序列发生器生成的prbs码为prbs31码时,所述并行序列检测器包括31个级联的d触发器,第二十八d触发器的输出端和第三十一d触发器的输出端进行异或运算后获得第一异或运算结果;

41、当所述并行序列检测器处于第一检测模式时,所述并行序列检测器的第一异或运算结果为根据接收到的第一校准码生成的第一校准码预测值,且所述并行序列检测器能够根据所述第一校准码与第一校准码预测值进行异或运算后获得第一误码信息;

42、当所述并行序列检测器处于第二检测模式时,所述并行序列检测器的第一异或运算结果反馈至第一d触发器的输入端进行循环,最后一个d触发器的输出结果与接收到的第二校准码进行异或运算后获得第二误码信息。

43、作为本发明的另一个方面,提供一种延迟校准方法,其中,应用于前文所述的源同步通信系统中,所述延迟校准方法包括:

44、启动延迟校准状态机,并设置滑窗电路的初始延迟值和数控延迟单元的初始延迟值;

45、保持所述滑窗电路的初始延迟值不变,在确定并行序列检测器处于第一检测模式时,控制所述延迟校准状态机进入位定时状态,在所述位定时状态下,当所述延迟校准状态机根据并行序列检测器针对第一校准码产生的误码信息确定第一校准码与第一匹配码不匹配时,调整数控延迟单元的延迟值,直至根据并行序列检测器针对所述第一校准码产生的误码信息确定第一校准码与第一匹配码匹配且匹配结果保持稳定预设周期,将此时数控延迟单元对应的延迟值确定为第一匹配延迟值;所述并行序列检测器能够根据接收到的第一校准码产生第一匹配码,并行序列发生器能够在所述位定时状态下产生第一校准码;

46、保持所述数控延迟单元的延迟值维持在所述第一匹配延迟值,控制所述延迟校准状态机进入字定时状态,在确定所述并行序列检测器处于第二检测模式时,位于字定时状态下的延迟校准状态机根据并行序列检测器针对第二校准码产生的误码信息确定第二校准码与第二匹配码不匹配时,调整滑窗电路的延迟值,直至根据并行序列检测器针对第二校准码产生的误码信息确定第二校准码与第二匹配码匹配且匹配结果保持稳定预设周期,将此时滑窗电路的延迟值确定为第二匹配延迟值;所述并行序列检测器能够根据接收到的第二校准码产生第二匹配码,所述并行序列发生器能够在所述字定时状态下产生第二校准码;

47、控制所述源同步通信系统以发送端的数控延迟单元的延迟值为第一匹配延迟值,以及滑窗电路的延迟值为第二匹配延迟值工作,并控制所述延迟校准状态机退出位定时状态及字定时状态。

48、进一步地,当所述延迟校准状态机根据并行序列检测器针对第一校准码产生的误码信息确定第一校准码与第一匹配码不匹配时,调整数控延迟单元的延迟值,直至根据并行序列检测器针对所述第一校准码产生的误码信息确定第一校准码与第一匹配码匹配且匹配结果保持稳定预设周期,将此时数控延迟单元对应的延迟值确定为第一匹配延迟值,包括:

49、接收所述并行序列检测器返回的第一误码信息,其中,所述第一校准码依次经过所述滑窗电路和所述数控延迟单元输出至所述并行序列检测器,所述并行序列检测器能够在第一检测模式下产生针对第一校准码的第一匹配码,并根据所述第一校准码与第一匹配码的匹配结果生成第一误码信息;

50、判断所述第一误码信息的电平状态;

51、若所述第一误码信息为高电平,则对所述数控延迟单元的当前延迟值进行调整,并重复执行接收并行序列检测器返回的第一误码信息的步骤,直至获得的所述第一误码信息为低电平;

52、当连续预设周期接收到的所述第一误码信息的电平状态均为低电平时,确定所述数控延迟单元所对应的当前延迟值为数控延迟单元的第一匹配延迟值。

53、进一步地,位于字定时状态下的延迟校准状态机根据并行序列检测器针对第二校准码产生的误码信息确定第二校准码与第二匹配码不匹配时,调整滑窗电路的延迟值,直至根据并行序列检测器针对第二校准码产生的误码信息确定第二校准码与第二匹配码匹配且匹配结果保持稳定预设周期,将此时滑窗电路的延迟值确定为第二匹配延迟值,包括:

54、接收所述并行序列检测器返回的第二误码信息,其中,所述第二校准码依次经过所述滑窗电路和所述数控延迟单元输出至所述并行序列检测器,所述并行序列检测器能够在第二检测模式下产生针对第二校准码的第二匹配码,并根据所述第二校准码与第二匹配码的匹配结果生成第二误码信息;

55、判断所述第二误码信息的电平状态;

56、若所述第二误码信息为高电平,则对所述滑窗电路的当前延迟值进行调整,并重复执行接收并行序列检测器返回的第二误码信息的步骤;

57、当连续预设周期接收到的所述第二误码信息的电平状态均为低电平时,确定所述滑窗电路所对应的当前延迟值为滑窗电路的第二匹配延迟值。

58、本发明提供的发送端,通过延迟校准状态机根据接收端的序列检测器的第一检测模式进入位定时状态以及根据接收端的序列检测器的第二检测模式进入字定时状态,以及在位定时状态下根据接收端的序列检测器输出的第一误码信息对所述数控延迟单元的延迟值进行调整,在字定时状态下根据接收端的序列检测器输出的第二误码信息对所述滑窗电路的延迟值进行调整,因此该发送端通过延迟校准状态机先进行位定时控制,然后进行字定时控制,解决了现有方案中数控延迟单元在发送端时无法进行位定时和字定时的问题,最终应用在源同步通信系统中时能够实现源同步通信系统的通道对齐。

- 还没有人留言评论。精彩留言会获得点赞!