产生死区时间的输入输出电路的制作方法

本技术涉及半导体集成电路,特别涉及一种产生死区时间的输入输出电路。

背景技术:

1、io(in/out,输入输出)电路广泛的应用在每个芯片上,因此io的设计需要考虑esd(electro-static discharge,静电阻抗器或静电释放)能力,所以在输出端通常有尺寸很大的esd mos,并且通常该类mos管会作为pad的输出驱动管。

2、由尺寸很大的pmos管和nmos管组成了一个反相器,所述反相器即为驱动pad的输出电路。为了降低io的动态功耗,必须尽可能的消除反相器正常工作中直接通路电流引起的功耗,即通过错开控制pmos与nmos导通时间,确保一个晶体管关断后再去打开另一个晶体管,这样微小的错开时间称为死区时间(dead time)。

3、图1是现有技术中产生死区时间的输入输出电路的示意图,如图1所示,所述输入输出电路包括电平转换模块(level shift)11、使能电路模块(enable circuit)12、p前级驱动器(pre p driver)13、p驱动器(p driver)14、pmos晶体管15,n前级驱动器(pre ndriver)16、n驱动器(n driver)17以及nmos晶体管18,通过p前级驱动器13与p驱动器14以及n前级驱动器16与n驱动器17产生死区时间。图2是控制pmos晶体管与nmos晶体管导通的信号波形图,如图2所示,当输入pmos晶体管15的epg信号变为高电平(所述pmos晶体管15断开)之后,输入nmos晶体管18的eng信号才变为高电平(所述noms晶体管18导通),当eng信号变为低电平(所述noms晶体管18断开)之后,epg信号才变为低电平(所述pmos晶体管15导通)。所述pmos晶体管15断开与所述noms晶体管18导通之间具有一微小的错开时间。

4、然而,采用上述的输入输出电路产生死区时间需要手动调整两个晶体管错开的时间,手动调整的速度慢,仿真量比较大,效率低,并且调整效果比较差。

技术实现思路

1、本实用新型的目的在于提供一种产生死区时间的输入输出电路,无需手动调整,使用灵活,减小了仿真量,并且能够准确产生死区时间时序,从而降低输入输出电路的动态功耗。

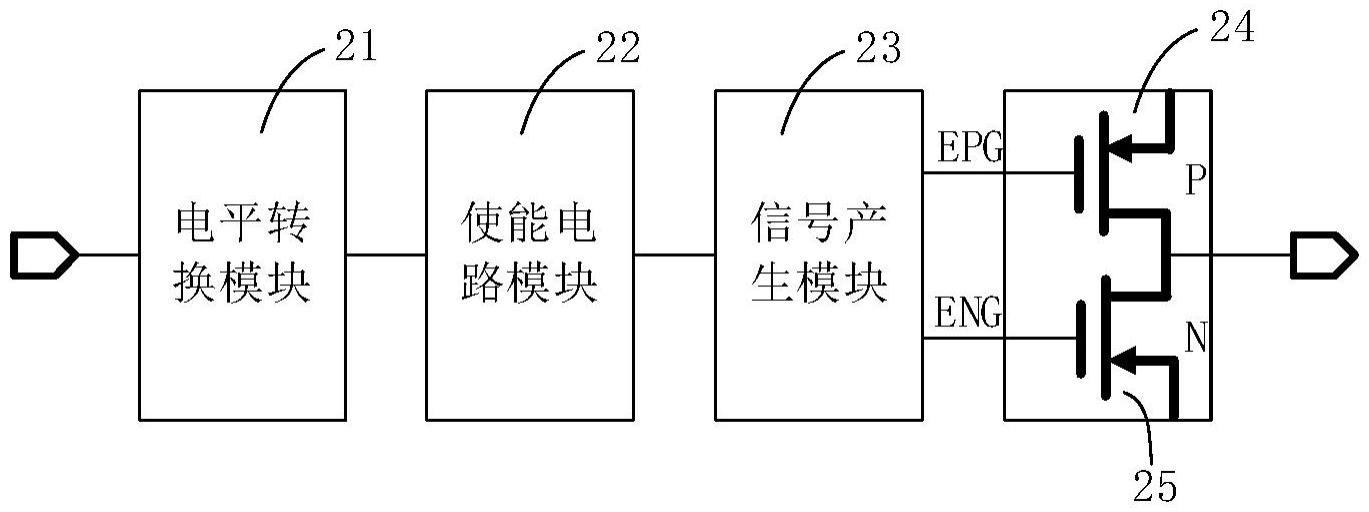

2、为解决上述技术问题,本实用新型提供一种产生死区时间的输入输出电路,包括:信号产生模块以及分别与所述信号产生模块连接的两个驱动晶体管,其中,所述信号产生模块包括多个逻辑门,所述信号产生模块通过数字电路本征延迟产生死区时间时序以错开两个所述驱动晶体管的导通时间。

3、可选的,所述信号产生模块包括两个非门与两个与非门,第一非门的输入端连接输入端口,所述第一非门的输出端连接第一与非门的一输入端,所述第一与非门的另一输入端连接第二与非门的输出端,所述第一与非门的输出端连接所述第二与非门的一输入端,所述第二与非门的另一输入端连接所述输入端口,所述第一与非门的输出端还连接一驱动晶体管,所述第二与非门的输出端还连接第二非门的输入端,所述第二非门的输出端连接另一驱动晶体管。

4、可选的,所述信号产生模块还包括一个同相门,所述同相门的输入端连接所述输入端口,所述同相门的输出端连接所述第二与非门的另一输入端。

5、可选的,两个所述驱动晶体管为pmos晶体管与nmos晶体管,所述第一与非门的输出端连接所述pmos晶体管,所述第二非门的输出端连接所述nmos晶体管。

6、可选的,所述pmos晶体管的栅极连接所述第一与非门的输出端,所述nmos晶体管的栅极连接所述第二非门的输出端,所述pmos晶体管的漏极与所述nmos晶体管的漏极相连接并连接输出端口。

7、可选的,所述pmos晶体管的源极连接一电流源,所述nmos晶体管的源极接地。

8、可选的,所述pmos晶体管断开后所述nmos晶体管导通,所述nmos晶体管断开后所述pmos晶体管导通。

9、可选的,所述输入输出电路还包括使能电路模块,所述使能电路模块的输出端连接所述信号产生模块的输入端,所述使能电路模块用于控制所述输入输出电路的工作状态。

10、可选的,所述输入输出电路还包括电平转换模块,所述电平转换模块的输出端连接所述使能电路模块的输入端,所述电平转换模块用于进行电平转换。

11、综上所述,在本实用新型提供的产生死区时间的输入输出电路中,包括信号产生模块以及分别与所述信号产生模块连接的两个驱动晶体管,信号产生模块包括多个逻辑门,所述信号产生模块通过数字电路本征延迟产生死区时间时序以错开两个所述驱动晶体管的导通时间,无需对电路进行手动调整,其使用灵活,减小了仿真量,并且时序调整效果明显,能够准确产生死区时间时序,从而降低输入输出电路的动态功耗。

12、进一步的,所述信号产生模块包括两个非门与两个与非门,第一非门的输入端连接输入端口,所述第一非门的输出端连接第一与非门的一输入端,所述第一与非门的另一输入端连接第二与非门的输出端,所述第一与非门的输出端连接所述第二与非门的一输入端,所述第二与非门的另一输入端连接所述输入端口,所述第一与非门的输出端还连接一驱动晶体管,所述第二与非门的输出端还连接第二非门的输入端,所述第二非门的输出端连接另一驱动晶体管。所述信号产生模块结构简单通用,缩短了设计时间。

技术特征:

1.一种产生死区时间的输入输出电路,其特征在于,包括:信号产生模块以及分别与所述信号产生模块连接的两个驱动晶体管,其中,所述信号产生模块包括多个逻辑门,所述信号产生模块通过数字电路本征延迟产生死区时间时序以错开两个所述驱动晶体管的导通时间。

2.根据权利要求1所述的产生死区时间的输入输出电路,其特征在于,所述信号产生模块包括两个非门与两个与非门,第一非门的输入端连接输入端口,所述第一非门的输出端连接第一与非门的一输入端,所述第一与非门的另一输入端连接第二与非门的输出端,所述第一与非门的输出端连接所述第二与非门的一输入端,所述第二与非门的另一输入端连接所述输入端口,所述第一与非门的输出端还连接一驱动晶体管,所述第二与非门的输出端还连接第二非门的输入端,所述第二非门的输出端连接另一驱动晶体管。

3.根据权利要求2所述的产生死区时间的输入输出电路,其特征在于,所述信号产生模块还包括一个同相门,所述同相门的输入端连接所述输入端口,所述同相门的输出端连接所述第二与非门的另一输入端。

4.根据权利要求3所述的产生死区时间的输入输出电路,其特征在于,两个所述驱动晶体管为pmos晶体管与nmos晶体管,所述第一与非门的输出端连接所述pmos晶体管,所述第二非门的输出端连接所述nmos晶体管。

5.根据权利要求4所述的产生死区时间的输入输出电路,其特征在于,所述pmos晶体管的栅极连接所述第一与非门的输出端,所述nmos晶体管的栅极连接所述第二非门的输出端,所述pmos晶体管的漏极与所述nmos晶体管的漏极相连接并连接输出端口。

6.根据权利要求5所述的产生死区时间的输入输出电路,其特征在于,所述pmos晶体管的源极连接一电流源,所述nmos晶体管的源极接地。

7.根据权利要求4所述的产生死区时间的输入输出电路,其特征在于,所述pmos晶体管断开后所述nmos晶体管导通,所述nmos晶体管断开后所述pmos晶体管导通。

8.根据权利要求1所述的产生死区时间的输入输出电路,其特征在于,所述输入输出电路还包括使能电路模块,所述使能电路模块的输出端连接所述信号产生模块的输入端,所述使能电路模块用于控制所述输入输出电路的工作状态。

9.根据权利要求8所述的产生死区时间的输入输出电路,其特征在于,所述输入输出电路还包括电平转换模块,所述电平转换模块的输出端连接所述使能电路模块的输入端,所述电平转换模块用于进行电平转换。

技术总结

本技术提供一种产生死区时间的输入输出电路,所述电路包括:信号产生模块以及分别与所述信号产生模块连接的两个驱动晶体管,所述信号产生模块包括多个逻辑门,所述信号产生模块通过数字电路本征延迟产生死区时间时序以错开两个所述驱动晶体管的导通时间。本技术无需对电路进行手动调整,其使用灵活,减小了仿真量,并且时序调整效果明显,能够准确产生死区时间时序,从而降低输入输出电路的动态功耗。

技术研发人员:曹亚历

受保护的技术使用者:绍兴中芯集成电路制造股份有限公司

技术研发日:20230418

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!