用于前后级时序控制的开漏输出电路的制作方法

本技术涉及开漏输出电路,具体涉及一种用于前后级时序控制的开漏输出电路。

背景技术:

1、随着电路系统功能的增加,电路控制越来越复杂,同时,多个子系统之间经常需要一定的时序控制,比如,被供电电路需要在供电电路完成输出电压的建立之后再工作。此时,经常前级器件会用开漏输出控制后级器件的使能或复位信号,达到控制时序的目的。

2、开漏输出也叫漏极开路输出,其使用场效应三极管或金属氧化物场效应管(mosfet),或称mos管。当使用mos管时,mos管的栅极和输入连接,源极接公共端,漏极悬空,且需要接一个适当阻值的电阻到电源。mos管导通时,将漏极拉低;mos管关断时,漏极被上拉电阻拉高。

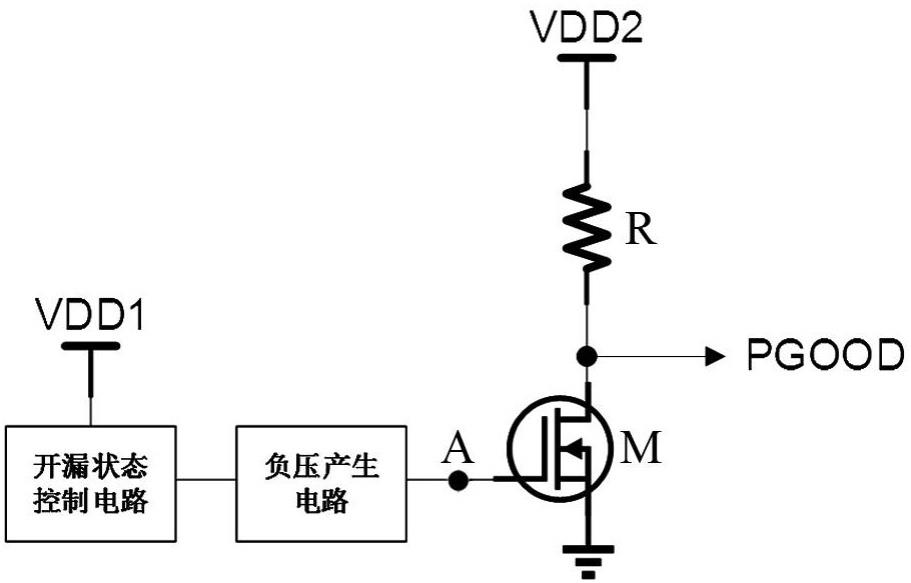

3、图1示出了一种现有的前后级控制系统的电路图。开漏输出器件一般用增强型nmos或三极管来实现。在图1的方案中,前级电路的开漏输出器件采用增强型mosfet实现,即mos管m。开漏状态控制电路(开漏输出器件m的栅极控制电路)由第一电源电压vdd1供电,开漏输出器件m的栅极电压由开漏状态控制电路决定。mos管m漏极接一上拉电阻r,上拉电阻r接第二电源电压vdd2。同时作为开漏输出器件的mos管m的漏极接到后级被控制器件的复位引脚nreset。当出现错误情况时,比如电源电压过低、器件过温、输出电压未建立等情况时,开漏状态控制电路将mos管m的栅极电压(栅极节点a)被升高,从而将mos管m的漏极拉低,对后级电路进行复位。当错误解除时,mos管m的栅极电压变低,mos管m的漏极被上拉电阻r拉高,后级电路正常工作。

4、然而,在该方案中,作为开漏输出器件m的三极管或增强型nmos的栅极都需要一个开启电压才能导通,从而将漏极拉低,比如,三极管的开启电压一般在0.7v左右,nmos的开启电压一般在1v或以上。

5、图2示出了上述电路中的信号时序图。结合图1和图2可看出,mos管m的栅极控制电路由第一电源电压vdd1供电,当第一电源电压vdd1没有电或电压低于mos管m的开启电压时,mos管m不能导通,无法将漏极拉低,因此漏极信号pgood会有一个毛刺,该毛刺会使后级被控制器件认为前级已经达到正常工作状态,从而错误开始工作。这导致系统的工作时序不能得到有效控制。

技术实现思路

1、(一)要解决的技术问题

2、本实用新型旨在解决开漏输出器件的开启电压导致的漏级信号毛刺带来的后级错误控制的问题。本实用新型的另一目的是使开漏输出器件在没有控制电压的情况下也能对后级进行有效的控制同时不影响正常工作。

3、(二)技术方案

4、为了解决上述技术问题,一种用于前后级时序控制的开漏输出电路,所述开漏输出电路包括开漏状态控制电路、开漏输出器件和上拉电阻;所述开漏输出器件采用耗尽型mosfet,其栅极由所述开漏状态控制电路控制;所述开漏状态控制电路由第一电源电压供电;所述开漏输出器件的漏级经由所述上拉电阻连接至第二电源电压。

5、根据本实用新型的优选实施例,所述开漏输出电路还包括负压产生电路,所述开漏输出器件的栅极经由所述负压产生电路连接至所述开漏状态控制电路;

6、根据本实用新型的优选实施例,所述负压产生电路用于在所述开漏状态控制电路输出关断信号时将该关断信号转换为负电压信号,从而将所述开漏输出器件关断。

7、根据本实用新型的优选实施例,所述负压产生电路具有负压输出端,其输出的负电压信号与所述第一电源电压绝对值相等。

8、根据本实用新型的优选实施例,所述负压产生电路包括第一开关、第二开关、第三开关、第四开关、飞跨电容和输出电容;所述第一开关的一端连接第一电源电压,另一端连接至所述飞跨电容的第一端;所述第二开关的一端接地,另一端也连接至所述飞跨电容的第一端;所述第三开关和第四开关的一端均连接至所述飞跨电容的第二端,该第三开关的另一端接地,该第四开关的另一端连接至所述输出电容的第一端,该第一端也作为负压输出端,该输出电容的第二端接地;所述第一开关和第三开关由第一时钟信号进行通断控制,所述第二开关和第四开关由第二时钟信号进行通断控制,所述第一时钟信号和第二时钟信号为互补的非交叠时钟信号。

9、(三)有益效果

10、本实用新型能够解决开漏输出器件的开启电压导致的漏级信号毛刺带来的后级错误控制的问题。

11、本实用新型还能够在开漏状态控制电路断电时将开漏输出器件的漏极电压有效拉低,从而实现可靠的系统前后级时序控制。

技术特征:

1.一种用于前后级时序控制的开漏输出电路,其特征在于:

2.根据权利要求1所述的用于前后级时序控制的开漏输出电路,其特征在于:

3.根据权利要求2所述的用于前后级时序控制的开漏输出电路,其特征在于:

4.根据权利要求3所述的用于前后级时序控制的开漏输出电路,其特征在于:所述负压产生电路具有负压输出端(vneg),其输出的负电压信号与所述第一电源电压(vdd1)绝对值相等。

5.根据权利要求4所述的用于前后级时序控制的开漏输出电路,其特征在于:

技术总结

本技术公开了一种用于前后级时序控制的开漏输出电路,其包括开漏状态控制电路、负压产生电路、开漏输出器件(M)和上拉电阻(R),所述开漏输出器件(M)采用耗尽型MOSFET,其栅极经由负压产生电路连接至开漏状态控制电路。开漏状态控制电路由第一电源电压(VDD1)供电,开漏输出器件(M)的漏级经由上拉电阻(R)连接至第二电源电压(VDD2)。本技术在没有开漏状态控制电压的情况下也能对后级进行有效的控制同时不影响正常工作。

技术研发人员:董贤辉,张家川,李晓明

受保护的技术使用者:北京升宇科技有限公司

技术研发日:20230619

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!