四通道信号调节器的制作方法

本技术涉及信号调节器,尤其涉及一种四通道信号调节器。

背景技术:

1、信号调节器是串联于信号源与采集设备之间的设备,用于对信号源输出的信号进行补偿,以消除信号偏差量的电子器件。对于数据采集系统和自动化控制系统而言,信号调节器是确保数据精确的关键环节,受到广泛的重视。

2、现有技术中,根据传感器的类型、输入信号源的幅值与范围,使信号调节器在电路中工作时只能适配于接线方式与出线方式相匹配的传感器,现有的信号调节器不能同时与多种传感器配套使用,且存在通用性、采样/测量精度低以及系统抗干扰性差的问题。

技术实现思路

1、本实用新型提供一种四通道信号调节器,以克服上述技术问题。

2、为了实现上述目的,本实用新型的技术方案是:

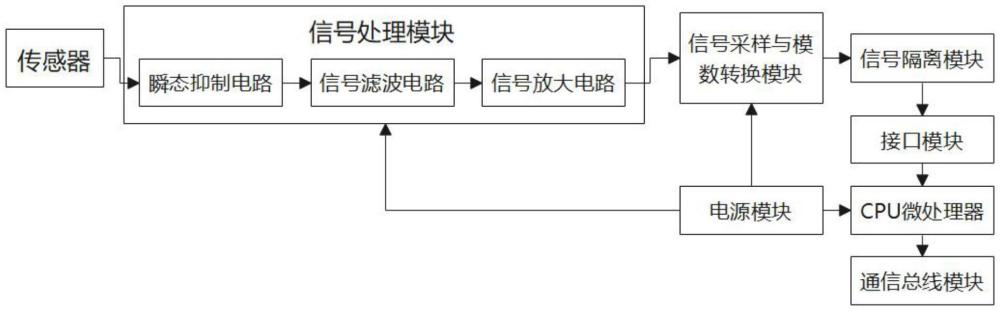

3、一种四通道信号调节器,包括信号采样与模数转换模块、信号隔离模块、电源模块、接口模块、通信总线模块以及若干信号处理模块;且所述若干信号处理模块分别与所述信号采集模块的输入端连接;

4、所述信号处理模块用于对通过设备传感器获取的传感器模拟信号进行滤波放大处理,并将所述滤波放大处理后的传感器模拟信号传输至所述信号采样与模数转换模块;所述设备传感器包括icp传感器、-24vdc供电三线制传感器、涡流前置器、无源磁电传感器以及有源霍尔传感器;

5、所述信号采样与模数转换模块的输出端与信号隔离模块的输入端连接,所述信号采样与模数转换模块用于对各所述信号处理模块滤波放大处理后的传感器模拟信号,进行同步采样并将所述传感器模拟信号转换为传感器数字信号;

6、所述信号隔离模块的输出端通过接口模块与cpu微处理器连接,所述信号隔离模块用于对所述信号采样与模数转换模块后的传感器数字信号进行隔离,并将隔离后的传感器数字信号输入至所述cpu微处理器;

7、所述cpu微处理器与通信总线模块连接,所述cpu微处理器用于根据所述信号隔离模块隔离后的传感器数字信号,通过所述通信总线模块发送设备控制信号;

8、所述电源模块与所述信号采样与模数转换模块、信号隔离模块、电源模块以及若干信号处理模块连接,用于提供电源。

9、进一步的,所述信号处理模块包括瞬态抑制电路、信号滤波电路以及信号放大电路;

10、所述瞬态抑制电路包括传感器接线端子q、第一二极管d8、第二二极管d9、第三二极管d13、第四二极管d14、第五二极管d41以及第六二极管d40;所述第一二极管d8的一端、第二二极管d9的一端、所述第三二极管d13的一端、第四二极管d14的一端、第一熔断保险丝f2的一端、第一电阻r80的一端以及第二电阻r79的一端连接;所述第一电阻r80的另一端与第二电阻r79的另一端以及所述传感器接线端子q的tp12接口连接,所述第三二极管d13的另一端与第四二极管d14的另一端接地,所述第一二极管d8的另一端、第二二极管d9的另一端以及传感器接线端子q的tp14接地,第三电阻r76的一端、第四电阻r75的一端、所述第五二极管d41的一端、第六二极管d40的一端以及第二熔断保险丝f7的一端链接,且第三电阻r76的另一端与第四电阻r75的另一端以及传感器接线端子q的tp16接口连接,所述第五二极管d41的另一端与第六二极管d40的另一端接地,所述第二熔断保险丝f7的另一端与pwr-24v_out2’接线端连接。

11、进一步的,所述信号滤波电路包括第一电磁干扰滤波器e3、第二电磁干扰滤波器e4、第七二极管d6、第八二极管d12、第一稳压芯片u10、第二稳压芯片u9以及信号继电器芯片u12;所述第二电磁干扰滤波器e4的接线端1、第八二极管d12的一端以及第一熔断保险丝f2的另一端连接,所述第二电磁干扰滤波器e4的接线端2、第九电阻r44的一端以及所述信号继电器芯片u12的引脚3连接,所述第二电磁干扰滤波器e4的接线端3接地;

12、所述信号继电器芯片u12的引脚1与第五电阻r39的一端连接,所述第五电阻r39的另一端与第一微型滑动开关s3的接线端2连接,所述信号继电器芯片u12的引脚2与第八电阻r42的一端连接,所述第八电阻r42的另一端接地,所述信号继电器芯片u12的引脚4与第七二极管d6的一端连接,所述第七二极管d6的另一端与第七电阻r33的一端以及所述第一稳压芯片u10的引脚4连接,且所述第七电阻r33的另一端与所述第一稳压芯片u10的引脚2、引脚3、引脚6以及引脚7连接,所述第一稳压芯片u10的引脚1与pwr_+24v接线端连接;所述第一稳压芯片u10的引脚6与pwr-24v_out2’接线端连接,所述第一稳压芯片u10的引脚7与第一电磁干扰滤波器e3的接线端2连接,所述第一电磁干扰滤波器e3的接线端3接地;所述第一电磁干扰滤波器e3的接线端1与所述第二稳压芯片u9的引脚1连接,所述第二稳压芯片u9的引脚4与第十电阻r25的一端以及pwr_-24v接线端连接,且所述第二稳压芯片u9的引脚2、引脚3、引脚6、引脚7以及第十电阻r25的另一端连接;所述信号继电器芯片u12的引脚8与第六电阻r38的一端连接,所述第六电阻r38的另一端与第二微型滑动开关s3的接线端2连接。

13、进一步的,所述信号放大电路包括第一信号放大器u13b、第二信号放大器u13a、第三信号放大器u11b以及第四信号放大器u11a;所述第二信号放大器u13a的引脚3、所述第一信号放大器u13b的引脚5以及第九电阻r44的另一端连接,所述第一信号放大器u13b的引脚6与第一信号放大器u13b的引脚7连接;所述第二信号放大器u13a的引脚2、第十一电阻r37的一端以及第一电容c1的一端连接,所述第二信号放大器u13a的引脚1、第十一电阻r37的另一端、第一电容c1的另一端以及第十二电阻r41的一端连接,且所述第二信号放大器u13a的引脚4与pwr_-24v接线端连接,所述第二信号放大器u13a的引脚8与pwr_+24v接线端连接;

14、所述第十二电阻r41的另一端、第十三电阻r72的一端、第二电容c2的一端以及所述第三信号放大器u11b的引脚6连接,且所述第十三电阻r72的另一端、第二电容c2的另一端、所述第三信号放大器u11b的引脚7、第十六电阻r35的一端以及第二十电阻r36的一端连接;所述第三信号放大器u11b的引脚5、第十四电阻r70的一端、第十五电阻r71的一端以及第三电容c3的一端连接,所述第十四电阻r70的另一端与电源模块的vref接线端连接,且所述第十五电阻r71的另一端与第三电容c3的另一端接地;所述第十六电阻r35的另一端、第六电容c33的一端以及第十九电阻r29的一端连接,所述第六电容c33的另一端与第十九电阻r29的另一端、第四信号放大器u11a的引脚1以及第二十一电阻r34的一端连接,所述第四信号放大器u11a的引脚3、第十七电阻r27的一端、第十八电阻r30的一端以及第四电容c34的一端连接,且所述第十七电阻r27的另一端与电源模块的vref接线端连接,所述第十八电阻r30的另一端与第四电容c34的另一端以及所述第四信号放大器u11a的引脚4接地,所述第四信号放大器u11a的引脚8与第五电容c76的一端连接,且所述第五电容c76的另一端接地;

15、所述第二十电阻r36的另一端、第九电容c42的一端以及第八电容c36的一端连接,且所述第九电容c42的另一端接地,所述第八电容c36的另一端、第二十一电阻r34的另一端以及第七电容c35的一端连接,所述第七电容c35的另一端接地。

16、进一步的,所述信号采样与模数转换模块的电路包括采样/转换芯片u8与硅晶振z1;所述采样/转换芯片u8的引脚64与第九电容c42的一端连接,所述采样/转换芯片u8的引脚63与第七电容c35的一端连接;所述采样/转换芯片u8的引脚59与第二十二电阻r22的一端以及第二十三电阻r24的一端连接,所述第二十二电阻r22的另一端与第二十三电阻r24的另一端以及第十电容c10的一端连接,所述第十电容c10的另一端接地,所述采样/转换芯片u8的引脚6与引脚43以及电源模块的vref接线端连接,且所述采样/转换芯片u8的引脚5、引脚44、引脚58以及引脚31接地,所述采样/转换芯片u8的引脚32与所述硅晶振z1的引脚3连接,所述硅晶振z1的引脚2接地,所述硅晶振z1的引脚1与adc_3v3d接线端连接,所述硅晶振z1的引脚4与第十一电容c18的一端以及adc_3v3d接线端连接,且所述第十一电容c18的另一端接地,所述采样/转换芯片u8的引脚61与第十二电容c32的一端以及第十三电容c28的一端连接,且所述第十二电容c32的另一端与第十三电容c28的另一端接地;所述采样/转换芯片u8的引脚52与第十四电容c23的一端以及第十五电容c27的一端连接,且所述第十四电容c23的另一端与第十五电容c27的另一端接地;所述采样/转换芯片u8的引脚34与第十六电容c22的一端以及第十七电容c17的一端连接,且所述第十六电容c22的另一端与第十七电容c17的另一端接地;所述采样/转换芯片u8的引脚21与第二十四电阻r26的一端连接,所述采样/转换芯片u8的引脚20与第二十五电阻r28的一端连接,且所述第二十四电阻r26的另一端与第二十五电阻r28的另一端接地;

17、所述采样/转换芯片u8的引脚56与第二十六电阻r23的一端连接,所述第二十六电阻r23的另一端与adc_3v3d接线端连接,所述采样/转换芯片u8的引脚37与第二十八电阻r8的一端连接,所述采样/转换芯片u8的引脚36、引脚38与第二十九电阻r9的一端连接,且所述第二十八电阻r8的另一端与第二十九电阻r9的另一端以及adc_3v3d接线端连接,所述采样/转换芯片u8的引脚30与第二十七电阻r27的一端连接,且所述第二十七电阻r27的另一端与adc_3v3d接线端连接,所述采样/转换芯片u8的引脚29、引脚28、引脚27以及引脚30分别与所述信号隔离模块连接。

18、进一步的,所述信号隔离模块的电路包括第一光电耦合器u16、第二光电耦合器u17、第三光电耦合器u15、第四光电耦合器u18、第一三极管q1、第二三极管q2、第三三极管q3以及第四三极管q4;所述第一光电耦合器u16的接线端1与第三十四电阻r87的一端连接,所述第三十四电阻r87的另一端与adc_3v3d接线端连接,所述第一光电耦合器u16的接线端3与第三十五电阻r90的一端连接,所述第三十五电阻r90的另一端与vcc_3v3d接线端连接,所述第一光电耦合器u16的接线端2与所述第一三极管q1的源极连接,所述第一三极管q1的发射极接地,且所述第一三极管q1的基极与第三十电阻r83的一端连接,所述第三十电阻r83的另一端与所述采样/转换芯片u8的引脚29连接,所述第一光电耦合器u16的接线端4与第三十六电阻r94的一端以及第三十七电阻r96的一端连接,所述第三十六电阻r94的另一端接地;

19、所述第二光电耦合器u17的接线端1与第三十八电阻r88的一端连接,所述第三十八电阻r88的另一端与adc_3v3d接线端连接,所述第二光电耦合器u17的接线端3与第三十九电阻r93的一端连接,所述第三十九电阻r93的另一端与vcc_3v3d接线端连接,所述第二光电耦合器u17的接线端2与所述第二三极管q2的源极连接,所述第二三极管q2的发射极接地,且所述第二三极管q2的基极与第三十一电阻r84的一端连接,所述第三十一电阻r84的另一端与所述采样/转换芯片u8的引脚28连接,所述第二光电耦合器u17的接线端4与第四十电阻r95的一端以及第四十一电阻r98的一端连接,所述第四十电阻r95的另一端接地;

20、所述第三光电耦合器u15的接线端1与第四十二电阻r89的一端连接,所述第四十二电阻r89的另一端与adc_3v3d接线端连接,第三光电耦合器u15的接线端3与第四十三电阻r91的一端连接,所述第四十三电阻r91的另一端与vcc_3v3d接线端连接,所述第三光电耦合器u15的接线端2与所述第三三极管q3的源极连接,所述第三三极管q3的发射极接地,且所述第三三极管q3的基极与第三十二电阻r85的一端连接,所述第三十二电阻r85的另一端与所述采样/转换芯片u8的引脚27连接,所述第三光电耦合器u15的接线端4与第四十四电阻r92的一端以及第四十五电阻r97的一端连接,所述第四十四电阻r92的另一端接地;

21、所述第四光电耦合器u18的接线端4与第四十六电阻r81的一端连接,所述第四十六电阻r81的另一端与adc_3v3d接线端连接,第四光电耦合器u18的接线端2与第四十七电阻r51的一端连接,所述第四十七电阻r51的另一端与vcc_3v3d接线端连接,所述第四光电耦合器u18的接线端1与所述第四三极管q4的源极连接,所述第四三极管q4的发射极接地,且所述第四三极管q4的基极与第四十九电阻r54的一端连接,所述第四光电耦合器u18的接线端3与第三十三电阻r82的一端以及第四十八电阻r86的一端连接,且所述第三十三电阻r82的另一端与所述采样/转换芯片u8的引脚30连接,所述第四十八电阻r86的另一端接地。

22、进一步的,所述接口模块的电路包括接口芯片u22、接线端子j1以及第五十电阻r99;所述接线端子j1的引脚14与第三十七电阻r96的另一端连接,所述接线端子j1的引脚12与第四十一电阻r98的另一端连接,所述接线端子j1的引脚10与第四十五电阻r97的另一端连接,所述接线端子j1的引脚8与第四十九电阻r49的另一端连接,所述接线端子j1的引脚13与所述第五十电阻r99的一端连接,所述第五十电阻r99的另一端与vcc_3v3d接线端连接,且所述接线端子j1的引脚2、引脚4与所述电源模块连接。

23、进一步的,所述通信总线模块包括但不仅限于rs485通信总线电路、tcp/ip协议通讯端口以及rj-45接口的10base-t/100base-tx以太网电缆的任意一种,与所述cpu微处理器连接。

24、有益效果:本实用新型提供了一种四通道信号调节器,通过高精度的信号采样与模数转换模块提高了四通道信号调节器采样与测量精度,且本实施例可与多种传感器配套使用且通用性强,能为不同传感器提供匹配的电源,同时采用信号隔离模块保证了信号传输过程中的稳定性,提高了系统的抗干扰性。

- 还没有人留言评论。精彩留言会获得点赞!