一种栅压自举开关电路

本发明涉及一种电路,具体的,属于一种栅压自举开关电路。

背景技术:

1、模数转换器(adc)一般要经过采样、量化、编码几个过程。其中,对于时域连续的输入信号进行采样是adc的第一步,因此任何高速高精度的adc都离不开高性能的采样保持电路。而作为采样保持电路重要的组成部分,采样开关的性能决定着整个采样保持电路的性能。

2、目前的栅压自举开关电路中,虽然可以基于控制时钟,实现对输入信号的采样与保持,但是依然存在如下问题:1.自举回路不充分的问题,往往在高速电路中,时钟周期较短,自举回路在此过程中不能建立完全,主开关管的导通电阻不能建立到理想值,进而影响带宽,而这一问题的深层成因,在于电路中存在寄生电容。2.开关管关断后的输出电压波动问题,在栅压自举电路中,主开关管关断后,会将输入信号通过小电容cds耦合到输出端,使得采样电容上的电压在保持阶段呈现出一定波动。

3、目前针对如上问题,开发出了一定的解决方案,如专利cn104052444b中,公开了通过增加一个副自举电容,对主自举回路上的副开关管栅极电容充电,提高响应速度。但是这种方法并不能完全解决问题,因此有必要采用其他方法进一步解决问题。

技术实现思路

1、为解决现有技术中栅压自举开关电路的回路建立时间较长和开关管关断后输出电压波动问题,本发明提供一种栅压自举开关电路,具体如下:

2、一种栅压自举开关电路,包括:

3、控制时钟电路、主自举开关电路、副自举开关电路和虚拟开关电路,其中:

4、所述控制时钟电路获取控制信号,将所述控制信号转变为控制时钟信号,由所述控制时钟电路的输出端输出;

5、所述控制时钟电路的输出端同时和主自举开关电路、副自举开关电路连接,所述控制时钟电路的输出端和所述主自举开关电路的mos管m9栅极连接,所述控制时钟信号电路的输出端和所述副自举开关电路的mos管m16栅极连接;

6、所述主自举开关电路和副自举开关电路连接,所述主自举开关电路的主自举电容cboost下极板和所述副自举开关电路的副自举电容caux连接,所述主自举开关电路的mos管m10栅极、mos管m5栅极和衬底、mos管m7衬底、mos管m10栅极均与所述副自举开关电路的mos管m14漏极连接;

7、所述虚拟开关电路和所述主自举开关电路连接,用于在所述主开关电路中mos管m12关断时,由mos管m17提供与之大小相同的电容。

8、可选的,控制时钟电路包括:

9、电源vdd、mos管m1、mos管m2和控制时钟clk;

10、所述电源vdd和所述mos管m1的源极连接;

11、所述mos管m1的漏极和所述mos管m2的漏极连接;

12、所述控制时钟clk同时和所述mos管m1的栅极和所述mos管m2的栅极连接;

13、所述mos管m1的漏极和所述mos管m2的漏极连接线设置引出点,用以输出所述控制时钟信号。

14、可选的,控制时钟信号还包括接地点,所述接地点与所述mos管m2的源极连接。

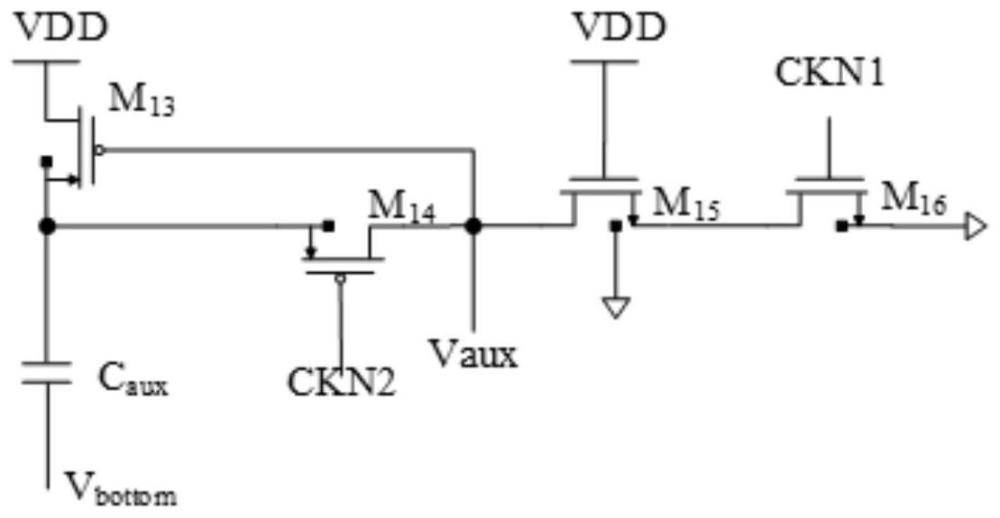

15、可选的,副自举开关电路包括电源vdd、mos管m13、mos管m14、mos管m15、mos管m16和副自举电容caux,其中:

16、所述电源vdd和所述mos管m13的漏极连接;

17、所述mos管m13源极同时和所述mos管m14的源极和所述副自举电容caux的上极板连接;

18、所述mos管m14的漏极和所述mos管m15的漏极连接并形成节点,所述mos管m13栅极和所述节点连接,所述节点还用于输出副自举信号电平vaux;

19、所述mos管m15的源极和所述mos管m16的漏极连接。

20、可选的,还包括充电电路,包括电源、mos管m5和mos管m6、主自举电容cboost;

21、所述电源与所述mos管m5的漏极连接;

22、所述mos管m5的源极和所述主自举电容cboost上极板连接;

23、所述主自举电容cboost下极板与所述mos管m6连接;

24、所述mos管m6源极接地;

25、所述mos管m5栅极接收所述副自举信号电平vaux;

26、所述mos管m6栅极接收所述控制时钟信号。

27、可选的,主自举开关电路包括mos管m7、mos管m10、mos管m11、mos管m12、主自举电容cboost和采样负载电容chold,其中:

28、所述mos管m7的源极和所述充电电路中的所述mos管m5源极连接;

29、所述mos管m7的栅极同时和所述控制时钟电路输出端和所述mos管m10漏极连接;

30、所述mos管m10的源极和所述mos管m11的漏极连接;

31、所述主自举电容cboost的下极板、所述副自举电容caux下极板连接;

32、所述mos管m11的源极和所述mos管m12的漏极连接;

33、所述mos管m12的源极和所述虚拟开关电路输出端连接,同时与所述采样负载电容chold的上极板连接;

34、所述采样负载电容chold的下极板接地。

35、可选的,所述mos管m12的栅极接收高电平vog。

36、可选的,所述虚拟开关电路包括电源、mos管m17、mos管m18、mos管m19和mos管m20;

37、所述电源同时和所述mos管m19和所述mos管m20的栅极连接;

38、所述mos管m19的漏极同时和所述mos管m17和所述mos管m18的栅极连接;

39、所述mos管m19的源极和所述mos管m20的漏极连接;

40、所述mos管m18的源极和所述mos管m17的漏极连接,接线上设置有输入点,所述输入点用于接入差分输入vip。

41、可选的,所述mos管m17源极和所述采样负载电容chold上极板连接。

42、本发明所达到的有益效果:

43、1、提高回路建立速度。传统栅压自举开关电路中,回路建立速度较慢的原因是其中存在寄生电容,在本申请中寄生电容进行了处理。同时增设的副自举电容,对回路中的栅极电容充电,从而让整个回路的建立速度提高。

44、2、消除输出信号波动。在栅压自举开关电路的输出端,设置同样大小的cds,另一端接到差分信号的另一个输入端,则两个差分输入在输出端产生等幅反向的纹波电压(ripple),实现相互抵消。

技术特征:

1.一种栅压自举开关电路,其特征在于,包括:

2.根据权利要求1所述的栅压自举开关电路,其特征在于,所述控制时钟电路包括:

3.根据权利要求2所述的栅压自举开关电路,其特征在于,所述控制时钟信号还包括接地点,所述接地点与所述mos管m2的源极连接。

4.根据权利要求1所述的栅压自举开关电路,其特征在于,所述副自举开关电路包括电源vdd、mos管m13、mos管m14、mos管m15、mos管m16和副自举电容caux,其中:

5.根据权利要求1所述的栅压自举开关电路,其特征在于,还包括充电电路,包括电源、mos管m5和mos管m6、主自举电容cboost;

6.根据权利要求1所述的栅压自举开关电路,其特征在于,所述主自举开关电路包括mos管m3、mos管m4、mos管m7、mos管m10、mos管m11、mos管m12、主自举电容cboost和采样负载电容chold,其中:

7.根据权利要求6所述的栅压自举开关电路,其特征在于,所述mos管m12的栅极接收高电平vog。

8.根据权利要求1所述的栅压自举开关电路,其特征在于,所述虚拟开关电路包括电源、mos管m17、mos管m18、mos管m19和mos管m20;

9.根据权利要求1或8所述的栅压自举开关电路,其特征在于,所述mos管m17源极和所述采样负载电容chold上极板连接。

技术总结

本发明公开了一种栅压自举开关电路,包括:控制时钟电路、主自举开关电路、虚拟开关电路和副自举开关电路,控制时钟电路同时和主自举开关电路和副自举开关电路连接,同时主自举开关电路和副自举开关电路连接,副自举开关电路输出副自举信号电平,为主自举开关电路中的寄生电容供电,同时在电路输出端接入一个同样大小的虚拟开关电路。本发明通过对寄生电容的充电,使得回路的建立时间大幅缩短,同时接入的同样大小虚拟开关电路,可以生成与输出端等幅相反的纹波电压,消除主开关管关断后,采样电容上存在的具有一定大小波动的电压。

技术研发人员:林军,张梦莹

受保护的技术使用者:南京大学

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!