一种小面积T触发器电路

本发明属于集成电路领域,涉及传统t触发器的结构优化,具体为一种小面积t触发器电路结构的实现。

背景技术:

1、上个世纪60年代,intel创始人之一的摩尔提出了“集成电路芯片上集成的晶体管数目约在18个月至24个月后增加一倍”的预测,集成电路也按照这一预测逐渐向更小的尺寸和更高的集成度发展。随着集成电路芯片的集成功能越来越丰富,芯片的制作不能再局限于数字和模拟电路分立的状态,数字电路模块的设计往往基于工艺厂提供的标准数字单元实现,其电路模型的面积完全取决于工艺尺寸,难以提高集成电路面积利用率。为了满足电路同时适配模拟和数字信号处理的能力,数字模拟混合的应用活跃在当今的集成电路领域,数模混合的设计具备模拟电路处理时序上连续信号的能力,同时兼具数字电路可编程、抗干扰能力强的特点。t触发器作为数字电路中不可或缺的电路单元,既可级联用作数字加减法计数器,也可添加相关组合逻辑实现信号频率的分频处理,广泛应用于诸如锁相环和存储器中的数字运算模块,传统的t触发器结构使用到的晶体管数目较多且结构相对固定,大规模的t触发器阵列占用了相当大的电路面积,在保证t触发器正常时序功能以及数据载入、导出的基础上对t触发器结构进行优化设计,能够极大的缩小基于t触发器的数字时序模块电路面积,从而对整体电路的面积性能和版图布局起到一定的积极作用。

技术实现思路

1、本发明的目的在于,提供一种小面积t触发器电路实现方法,兼具t触发器的数据载入、导出和时序逻辑功能,以优化传统t触发器的面积和速度性能。

2、为实现上述目的,本发明采用如下技术方案:

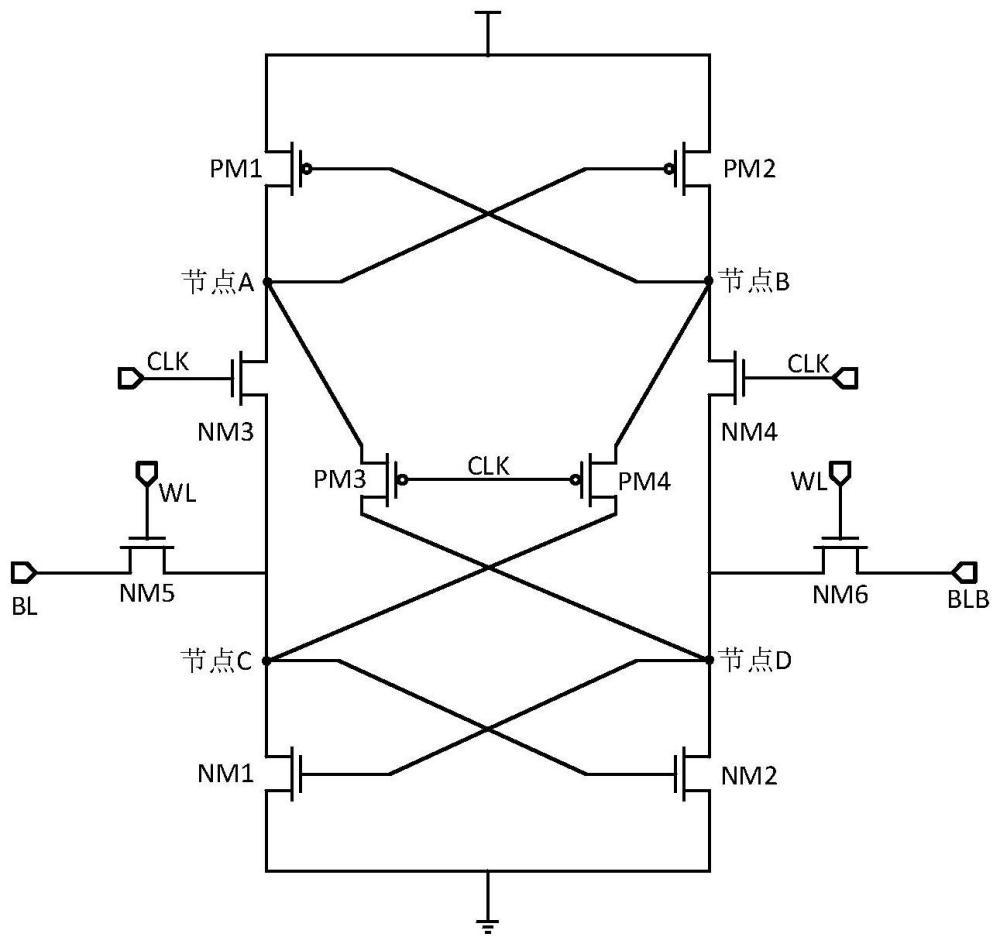

3、一种小面积t触发器电路,包括:6个nmos管nm1、nm2、nm3、nm4、nm5、n m6,4个pmos管pm1、pm2、pm3、pm4。端口包括时钟信号输入端口clk;数据载入、读取使能信号端口wl;数据载入、读取端口bl、blb。电路节点包括节点a、节点b、节点c、节点d,当前存储状态分别以反相的电平信息存储在四个节点处,节点a、节点b互为一对存储状态节点,节点c、节点d互为一对存储状态节点。

4、电路整体连接情况如下:nm1源极接地,漏极接节点c,栅极接节点d;nm2源极接地,漏极接节点d,栅极接节点c;nm3源极接节点c,漏极接节点a,栅极接clk端口;nm4源极接节点d,漏极接节点b,栅极接clk端口;nm5源极接节点c,漏极接bl端口,栅极接wl端口;nm6源极接节点d,漏极接blb端口,栅极接wl端口;pm1源极接电源,漏极接节点a,栅极接节点b;pm2源极接电源,漏极接节点b,栅极接节点a;pm3源极接节点a,漏极接节点d,栅极接clk端口;pm4源极接节点b,漏极接节点c,栅极接c lk端口。

5、1.t触发器的数据载入

6、t触发器的数据载入是基于6t sram的写入电路实现的,包含两个反相器,分别由pm1、nm1组成的inv1和pm2、nm2组成的inv2,两个传输管nm5和nm6。写入时首先将wl端口输入高电平,然后根据需要写入的数据进行操作,如果要写入1,bl端口输入1,blb端口输入0;如果写入0,bl端口输入0,blb端口输入1,此时传输管nm5和nm6导通,由于bl和blb上的信号较强,锁存器中的存储的状态将被bl和blb的信号覆盖,完成写入过程。wl拉低后,由于两个反相器处于正反馈状态,节点c和d的电压将保持不变,维持写入后的状态,t触发器数据载入的原理图如图1。

7、2.t触发器的数据导出

8、预充电模块将两条位线bl和blb预充电至vdd;然后将字线wl拉高,如果节点c为1,节点d为0,bl的电压不变,blb的电压将降低;如果节点c为0,节点d为1,bl的电压将降低,blb的电压保持不变。通过读取bl和blb的差分电压即可得到sram中存储的数据,t触发器数据导出的原理图如图1。

9、3.t触发器的时序逻辑

10、t触发器的实现功能为当输入时钟边沿(上升沿或者下降沿)来临时,当前存储状态反相,其他时刻当前存储状态保持不变。本发明的t触发器结构如图2所示,整体结构由6t结构的sram存储单元外加一对nmos开关nm3、nm4和一对pmos开关pm3、pm4构成存储单元就是指节点c、节点d或者节点a、节点b上存储的数字逻辑,两对开关的导通情况相反,nm3、nm4开关导通时pm3、pm4开关关断;反之,pm3、pm4开关导通时nm3、nm4开关关断。开关导通时由nm1和nm2组成的锁存器下半部分和由pm1和pm2组成的锁存器上半部分会发生电压的变化,变化的情况视具体的开关类型而定,

11、本发明的有益效果如下:

12、1、本发明的新型t触发器电路结构最大的优势在于使用更少的晶体管数量和更小的电路面积来实现相同的t触发器功能,相较传统基于d触发器结构实现的t触发器需要22个mo s管,本发明的新型t触发器仅需要10个mos管,面积利用率上提高了两倍之多。

13、2、本发明的新型t触发器在工作时仅涉及两条支路的充放电,动态功耗相较传统基于d触发器结构的t触发器更小。

技术特征:

1.一种小面积t触发器电路,其特征在于,所述电路的电路元件包括6个nmos管nm1、nm2、nm3、nm4、nm5、nm6,4个pmos管pm1、pm2、pm3、pm4;端口包括时钟信号输入端口clk;数据载入、读取使能信号端口wl;数据载入、读取端口bl、blb;电路节点包括节点a、节点b、节点c、节点d,当前存储状态分别以反相的电平信息存储在四个节点处,节点a、节点b互为一对存储状态节点,节点c、节点d互为一对存储状态节点;

2.根据权利要求1所述的一种小面积t触发器电路,其特征在于,所述电路能够实现数据载入、数据导出、时序功能。

技术总结

本发明公开了一种小面积T触发器电路,属于集成电路领域。该电路基于6T SRAM锁存器结构,具备正常SRAM单元的读写和存储功能,还能通过4个额外的开关完成T触发器的逻辑功能,SRAM单元的读写对应T触发器的数据载入和数据导出。该结构使用更少数目的晶体管来实现传统T触发器的功能,主要从电路面积和功能集成度等方面对电路进行优化。

技术研发人员:王俊杰,鄢士钦,刘祎鹤,刘爽,潘瑞城,刘洋

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!