流水线模数转换器的制作方法

本发明涉及集成电路,特别是涉及一种流水线模数转换器。

背景技术:

1、模数转换器(adc)是实现模拟信号与数字信号转换的关键器件。随着电子技术的发展,对模数转换器的要求也在不断提高,特别是在高分辨率、高速转换以及低功耗等方面。传统的模数转换器设计由于功耗较高,限制了其在实际应用中的使用。因此,开发一种低功耗的高分辨率模数转换器,是当前技术的一个迫切需求。

2、流水线模数转换器是一种常见的结构,能够实现高分辨率和高速转换。然而,传统的流水线模数转换器每个子模数转换器都需要一个独立的运放,这会增加电路的功耗和面积。同时,由于相邻两级复位的放大器一直处于偏执状态,进一步加大了电路的功耗。

3、基于此,现有技术提出了一种动态放大器,在放大器处于复位相时将其关断,以减少静态功耗,但是,该方法仍然存在弊端,运放的个数并没有减少,占据了芯片较大的面积。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种流水线模数转换器技术方案,基于分时复用,使每两个流水级共用一个乘法数模转换器,而不再是每个流水级单独配置使用一个乘法数模转换器,以减少乘法数模转换器的数量,减小流水线模数转换器的面积尺寸,降低流水线模数转换器的功耗。

2、为实现上述目的及其他相关目的,本发明提供的技术方案如下。

3、一种流水线模数转换器,包括n级流水级及数字校准单元,n级所述流水级依次级联,基于分时复用,第i级所述流水级与第i+1级所述流水级共用乘法数模转换器;在每个周期的前半段,所述乘法数模转换器同时用于第i级所述流水级的采样、第i+1级所述流水级的残差放大,得到第i+1级所述流水级的增益残差;在每个周期的后半段,所述乘法数模转换器同时用于第i+1级所述流水级的采样、第i级所述流水级的残差放大,得到第i级所述流水级的增益残差;其中,n为大于或者等于2的整数,i为1~n-1范围内的奇数。

4、可选地,所述乘法数模转换器包括运算放大器和开关电容阵列,所述开关电容阵列包括采样电容和反馈电容,在每个周期的前半段,通过所述采样电容对第i级所述流水级的模拟输入信号进行采样,通过所述反馈电容引入第i+1级所述流水级的量化模拟信号并计算得到第i+1级所述流水级的残差,再通过所述运算放大器对第i+1级所述流水级的残差进行放大,得到第i+1级所述流水级的增益残差;在每个周期的后半段,通过所述采样电容引入第i级所述流水级的量化模拟信号并计算得到第i级所述流水级的残差,再通过所述运算放大器对第i级所述流水级的残差进行放大,得到第i级所述流水级的增益残差,并通过所述反馈电容对第i级所述流水级的增益残差进行采样。

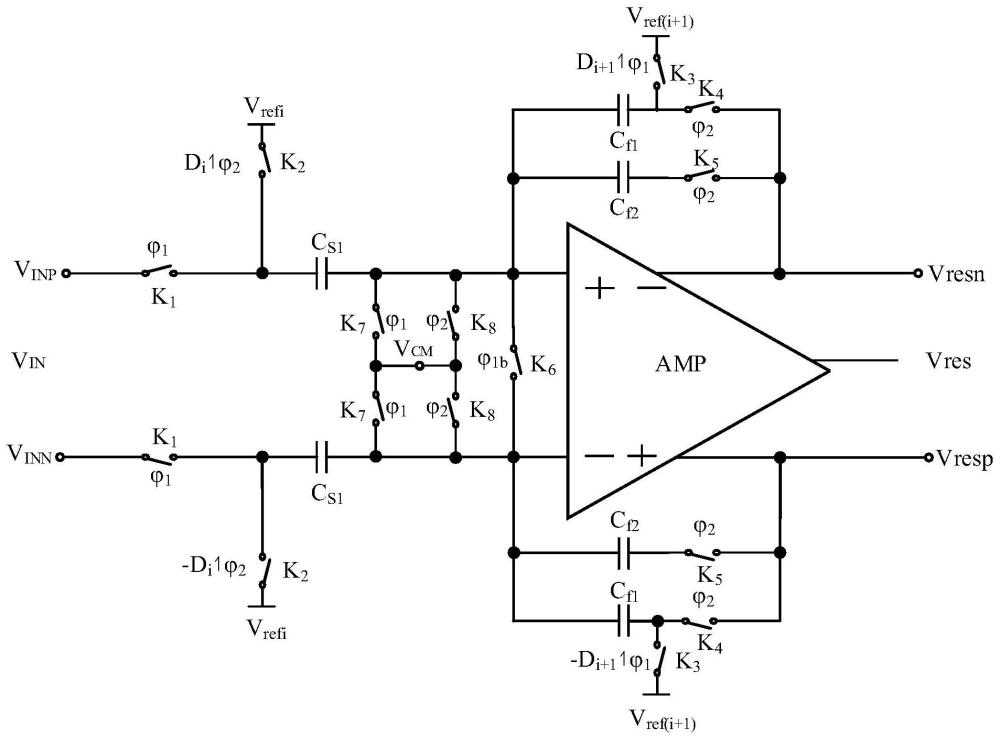

5、可选地,所述反馈电容包括第一反馈电容和第二反馈电容,所述开关电容阵列包括两个所述采样电容、两个所述第一反馈电容、两个所述第二反馈电容、两个第一开关、两个第二开关、两个第三开关、两个第四开关、两个第五开关及一个第六开关,

6、第一个所述采样电容的第一端接串接的第一个所述第一开关后接所述模拟输入信号的差分正端,第一个所述采样电容的第一端还经串接的第一个所述第二开关后接第一参考信号,第一个所述采样电容的第二端接所述运算放大器的同相输入端,第一个所述第一反馈电容的第一端接第一个所述采样电容的第二端,第一个所述第一反馈电容的第二端经串接的第一个所述第三开关后接第二参考信号,第一个所述第一反馈电容的第二端还经串接的第一个所述第四开关后接所述运算放大器的反相输出端,第一个所述第二反馈电容的第一端接第一个所述采样电容的第二端,第一个所述第二反馈电容的第二端经串接的第一个所述第五开关后接所述运算放大器的反相输出端,

7、第二个所述采样电容的第一端接串接的第二个所述第一开关后接所述模拟输入信号的差分负端,第二个所述采样电容的第一端还经串接的第二个所述第二开关后接所述第一参考信号,第二个所述采样电容的第二端接所述运算放大器的反相输入端,第二个所述第一反馈电容的第一端接第二个所述采样电容的第二端,第二个所述第一反馈电容的第二端经串接的第二个所述第三开关后接所述第二参考信号,第二个所述第一反馈电容的第二端还经串接的第二个所述第四开关后接所述运算放大器的同相输出端,第二个所述第二反馈电容的第一端接第二个所述采样电容的第二端,第二个所述第二反馈电容的第二端经串接的第二个所述第五开关后接所述运算放大器的同相输出端,

8、所述第六开关的第一端接所述运算放大器的同相输入端,所述第六开关的第二端接所述运算放大器的反相输入端,所述运算放大器的反相输出端作为差分输出负端,所述运算放大器的同相输出端作为差分输出正端,配合输出第i级所述流水级的增益残差或者第i+1级所述流水级的增益残差,

9、两个所述第一开关的控制端分别接第一控制信号,第一个所述第二开关的控制端接第二控制信号,第二个所述第二开关的控制端接第三控制信号,第一个所述第三开关的控制端接第四控制信号,第二个所述第三开关的控制端接第五控制信号,两个所述第四开关的控制端分别接第六控制信号,两个所述第五开关的控制端分别接所述第六控制信号,所述第六开关的控制端接第七控制信号。

10、可选地,所述第一控制信号与所述第六控制信号互补,所述第二控制信号与所述第三控制信号互补,所述第四控制信号与所述第五控制信号互补,所述第二控制信号由第i级所述流水级的量化数字码与所述第六控制信号与运算得到,所述第四控制信号由第i+1级所述流水级的量化数字码与所述第一控制信号与运算得到。

11、可选地,所述开关电容阵列还包括两个第七开关及两个第八开关,第一个所述第七开关的输入端接第一个所述采样电容的第二端,第一个所述第七开关的输出端接共模电压,第一个所述第七开关的输出端还接第二个所述第七开关的输入端,第二个所述第七开关的输出端接第二个所述采样电容的第二端,两个所述第七开关的控制端接所述第一控制信号,第一个所述第八开关的输入端接第一个所述采样电容的第二端,第一个所述第八开关的输出端接所述共模电压,第一个所述第八开关的输出端还接第二个所述第八开关的输入端,第二个所述第八开关的输出端接第二个所述采样电容的第二端,两个所述第八开关的控制端接所述第四控制信号。

12、可选地,在每个周期的前半段,导通两个所述第一开关及两个所述第七开关,通过两个所述采样电容对第i级所述流水级的模拟输入信号进行采样,同时,导通两个所述第三开关及两个所述第五开关,通过两个所述第一反馈电容引入第i+1级所述流水级的量化模拟信号并计算得到第i+1级所述流水级的残差,再通过所述运算放大器对第i+1级所述流水级的残差进行放大,得到第i+1级所述流水级的增益残差。

13、可选地,在每个周期的后半段,导通两个所述第二开关、两个所述第四开关及两个所述第五开关,通过两个所述采样电容引入第i级所述流水级的量化模拟信号并计算得到第i级所述流水级的残差,再通过所述运算放大器对第i级所述流水级的残差进行放大,得到第i级所述流水级的增益残差,同时,导通两个所述第八开关,通过两个所述第一反馈电容对第i级所述流水级的增益残差进行采样。

14、可选地,在通过两个所述采样电容对第i级所述流水级的模拟输入信号进行采样时,以及在通过两个所述第一反馈电容对第i级所述流水级的增益残差进行采样时,分别引入所述共模电压,通过所述共模电压对所述运算放大器输入端的寄生电容以及共用的两个所述第一反馈电容进行复位,以消除上一相位的残留电荷对下一相位的非线性影响。

15、可选地,所述流水线模数转换器还包括异步时钟单元,所述异步时钟单元对输入时钟进行延迟处理,得到采样时钟,再在两个所述采样时钟的采样脉宽之间,产生多个可控的异步时钟,多个所述异步时钟用于生成所述第一控制信号、所述第四控制信号及其他控制信号,以降低各级所述流水级的内部时钟频率要求。

16、可选地,所述异步时钟单元包括延迟触发单元及环形振荡单元,所述延迟触发单元对所述输入时钟进行延迟处理,得到所述采样时钟,所述环形振荡单元与所述延迟触发单元连接,形成环路,所述环形振荡单元产生多个所述异步时钟。

17、可选地,所述延迟触发单元包括rs触发器、同或门、第一缓冲器、锁存器、第一pmos管、第二pmos管、第一nmos管、第二nmos管及第三nmso管,

18、所述第一pmos管的源极接所述输入时钟,所述第一pmos管的栅极接所述第一缓冲器的输出端,所述第一pnmos管的漏极接所述第一nmos管的漏极,所述第一nmos管的栅极接所述第一缓冲器的输入端,所述第一nmos管的源极接所述第一pmos管的源极,

19、所述第二pmos管的源极接电源电压,所述第二pmos管的栅极接所述第一pmos管的漏极,所述第二pmos管的漏极接所述第二nmos管的漏极,所述第二nmos管的栅极接所述rs触发器的第一输入端,所述第二nmos管的源极接地,所述第三nmos管的漏极接所述第二nmos管的漏极,所述第三nmos管的栅极接所述同或门的第三输入端,所述第三nmos管的源极接地,

20、所述锁存器的输入端接所述第三nmos管的漏极,所述锁存器的输出端接所述rs触发器的第二输入端,所述rs触发器的输出端接所述同或门的第二输入端,所述同或门的第一输入端接所述rs触发器的第一输入端,所述同或门的第四输入端接所述第一pmos管的源极,所述同或门的输出端接所述第一缓冲器的输入端,

21、所述锁存器的输出端输出所述采样时钟。

22、可选地,所述环形振荡单元包括六个与非门、五个电容、七个第二缓冲器,

23、第一个所述与非门的两个输入端分别接所述rs触发器的输出端,第一个所述与非门的第一输出端经串接的第一个所述第二缓冲器后接第二个所述与非门的第一输入端,第一个所述与非门的第二输出端接第一个所述电容的第一端,第一个所述电容的第二端接地,

24、第二个所述与非门的第二输入端接所述rs触发器的输出端,第二个所述与非门的第一输出端经串接的第二个所述第二缓冲器后接第三个所述与非门的第一输入端,第二个所述与非门的第二输出端接第二个所述电容的第一端,第二个所述电容的第二端接地,

25、第三个所述与非门的第二输入端接所述rs触发器的输出端,第三个所述与非门的第一输出端经串接的第三个所述第二缓冲器后接第四个所述与非门的第一输入端,第三个所述与非门的第二输出端接第三个所述电容的第一端,第三个所述电容的第二端接地,

26、第四个所述与非门的第一输入端还接所述第三nmos管的栅极,第四个所述与非门的第二输入端接所述rs触发器的输出端,第四个所述与非门的第一输出端经串接的第四个所述第二缓冲器后接第五个所述与非门的第一输入端,第四个所述与非门的第二输出端接第四个所述电容的第一端,第四个所述电容的第二端接地,

27、第五个所述与非门的第二输入端接所述rs触发器的输出端,第五个所述与非门的第一输出端经依次串接的第五个所述第二缓冲器、第六个所述第二缓冲器后接第六个所述与非门的第一输入端,第五个所述与非门的第二输出端接第五个所述电容的第一端,第五个所述电容的第二端接地,

28、第七个所述第二缓冲器的输入端接所述rs触发器的输出端,第七个所述第二缓冲器的输出端接第六个所述与非门的第二输入端,第六个所述与非门的输出端接所述rs触发器的第一输入端,

29、第一个所述与非门、第二个所述与非门、第三个所述与非门、第四个所述与非门及第五个所述与非门一一对应输出五个所述异步时钟。

30、如上所述,本发明提供的流水线模数转换器,至少具有以下有益效果:

31、基于分时复用,第i级流水级与第i+1级流水级共用乘法数模转换器,每两个流水级共用一个乘法数模转换器,而不再是每个流水级单独配置使用一个乘法数模转换器,有效减少了乘法数模转换器的数量,减小了流水线模数转换器的面积尺寸,并降低了流水线模数转换器的功耗。

- 还没有人留言评论。精彩留言会获得点赞!