一种芯片输出驱动电路的制作方法

本发明属于输出电路,具体涉及一种芯片输出驱动电路。

背景技术:

1、芯片输出驱动电路是连接芯片内部和外部设备的接口,负责将芯片内部产生的信号电平转换为适合与外部设备通信的信号。芯片输出驱动电路的设计需要综合考虑多个方面,主要包括以下几点:

2、1)信号电平的兼容性。不同的应用场景和协议有不同的信号电平标准,例如lvds(low voltage differential signal,低分差动信号)电平标准、slvs(serial linkvoltage standard,串行链路电压标准)电平标准等。这些标准定义了不同的共模电平(common-mode voltage,vcm)和差模电平(output differential voltage,vod)的范围。如果芯片输出驱动电路能够支持多种信号电平标准,将增加芯片的应用范围和灵活性。

3、2)灵活性和可扩展性。灵活性和可扩展性是提高芯片输出驱动电路适应不同工作条件和需求的重要因素。灵活性主要指芯片输出驱动电路能否根据不同的工作条件进行调节和优化,可扩展性主要指芯片输出驱动电路能否支持更多的信号通道和更高的信号速度。为了提高灵活性和可扩展性,可以采用一些技术手段,如增加可调节的偏置电压、使用可编程的逻辑门、使用高速的差分放大器等。

4、3)信号的速度和带宽。信号的速度和带宽决定了芯片输出驱动电路的性能和效率。影响信号速度和带宽的主要因素是容性负载,包括芯片内部电路自身的寄生电容负载和芯片外部封装、走线等引入的额外负载。为了提高信号速度和带宽,需要优化芯片内部电路的工艺和面积,以及选择合适的封装和走线方式。

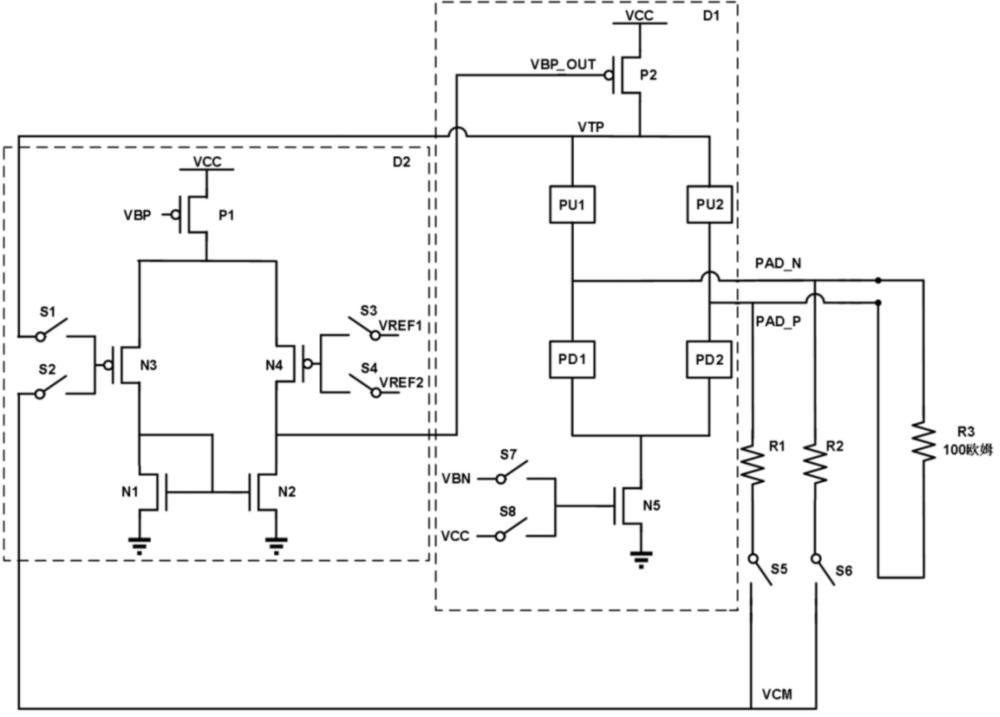

5、在传统的多兼容芯片方案中,通常会针对不同的电平标准设计不同的电路。图1为传统的针对多兼容需求设计的芯片输出驱动电路的结构示意图,in_p和in_n表示芯片内部信号,pad_p和pad_n表示输出信号,与芯片引脚相连接,i1和i2分别代表两种电平对应的驱动电路,在实施过程中,通过控制i1驱动电路和i2驱动电路这两个电路的开启和关闭,进而实现多种电平的输出。

6、具体地,作为图1中i1驱动电路和i2驱动电路的举例,图2和图3分别示意出了传统技术中支持lvds电平标准的lvds驱动电路和支持slvs电平标准的slvs驱动电路,其中,lvds驱动电路是电流模式结构,其从电源输入端接入供电电压vtp,再通过输出固定电流到芯片外100欧姆电阻负载上得到差模电平vod,而共模电平vcm则通过额外的共模反馈电路实现。slvs驱动电路为电压模式结构,通过驱动电路开关管与芯片外100欧姆组成的分压网络,pad_p脚和pad_n脚的输出电平将为基准电压vreg(reference voltage)的分压值,从而输出对应的差模电平vod值和共模电平vcm值。

7、但是,在使用现有技术过程中,发明人发现现有技术中至少存在如下问题:

8、兼容性和速度通常是一对矛盾的需求,兼容更多电平标准意味着需要设计多种驱动电路,这会增加芯片的面积和负载,从而降低输出信号能达到的速度。如图1中传统的芯片输出驱动电路,会遇到兼容性与带宽折中的问题,即难以同时兼顾兼容性与带宽,多个驱动电路的并联,将难以避免地增加芯片面积,增加芯片自身负载,从而限制速度的提升。

技术实现思路

1、本发明旨在至少在一定程度上解决上述技术问题,本发明提供了一种芯片输出驱动电路。

2、为了实现上述目的,本发明采用以下技术方案:

3、第一方面,本发明提供了一种芯片输出驱动电路,包括第一复用电路单元、第二复用电路单元、第一共模电压采样电阻、第二共模电压采样电阻、第五开关和第六开关,所述第二复用电路单元连接有第一参考电压输入端vref1和第二参考电压输入端vref2,所述第一复用电路单元连接有第一差分信号输出端pad_n和第二差分信号输出端pad_p;

4、其中,所述第二复用电路单元包括第一p型场效应管、第一n型场效应管、第二n型场效应管、第三n型场效应管、第四n型场效应管、第一开关、第二开关、第三开关和第四开关;所述第一p型场效应管的栅极连接第一偏置电压输入端vbp,所述第一p型场效应管的源极连接电源输入端vcc,所述第一p型场效应管的漏极分别与所述第三n型场效应管的漏极和所述第四n型场效应管的漏极连接,所述第三n型场效应管的栅极分别连接所述第一开关的一端和所述第二开关的一端,所述第一开关的另一端与所述第一复用电路单元连接,所述第二开关的另一端分别连接所述第五开关的一端和所述第六开关的一端,所述第五开关的另一端通过所述第一共模电压采样电阻连接第二差分信号输出端pad_p,所述第六开关的另一端通过所述第二共模电压采样电阻连接第一差分信号输出端pad_n,所述第四n型场效应管的栅极分别与所述第三开关的一端和所述第四开关的一端连接,所述第三开关的另一端连接第一参考电压输入端vref1,所述第四开关的另一端连接第二参考电压输入端vref2,所述第三n型场效应管的源极与所述第一n型场效应管的漏极连接,所述第三n型场效应管的源极还分别与所述第一n型场效应管的栅极和所述第二n型场效应管的栅极连接,所述第四n型场效应管的源极与所述第二n型场效应管的漏极连接,所述第四n型场效应管的源极与所述第二n型场效应管的漏极的结合点与所述第一复用电路单元连接,所述第一n型场效应管的源极和所述第二n型场效应管的源极均接地;

5、所述第一复用电路单元包括第二p型场效应管、第一上拉器件、第二上拉器件、第一下拉器件、第二下拉器件、第五n型场效应管、第七开关和第八开关;所述第二p型场效应管的源极连接所述电源输入端vcc,所述第二p型场效应管的栅极连接所述第四n型场效应管的源极与所述第二n型场效应管的漏极的结合点,所述第二p型场效应管的漏极与所述第一开关的另一端连接,所述第二p型场效应管的漏极还分别与所述第一上拉器件的一端和所述第二上拉器件的一端连接,所述第一上拉器件的另一端与所述第一下拉器件的一端连接,所述第一上拉器件与所述第一下拉器件的结合点连接所述第一差分信号输出端pad_n,所述第二上拉器件的另一端与所述第二下拉器件的一端连接,所述第二上拉器件与所述第二下拉器件的结合点连接所述第二差分信号输出端pad_p,所述第一下拉器件的另一端和所述第二下拉器件的另一端均与所述第五n型场效应管的漏极连接,所述第五n型场效应管的栅极分别与所述第七开关的一端和所述第八开关的一端连接,所述第七开关的另一端连接第二偏置电压输入端vbn,所述第八开关的另一端连接所述电源输入端vcc,所述第五n型场效应管的源极接地。

6、在一个可能的设计中,当所述芯片输出驱动电路配置于lvds模式时,所述第二开关、所述第四开关、所述第五开关、所述第六开关和第七开关闭合,所述第一开关、所述第三开关和第八开关断开;当所述芯片输出驱动电路配置于slvs模式时,所述第二开关、所述第四开关、所述第五开关、所述第六开关和第七开关断开,所述第一开关、所述第三开关和第八开关闭合。

7、在一个可能的设计中,所述第一上拉器件包括第三p型场效应管和第八n型场效应管,所述第三p型场效应管的源极和所述第八n型场效应管的漏极均与所述第二p型场效应管的漏极连接,所述第三p型场效应管的漏极和所述第八n型场效应管的源极均连接所述第一差分信号输出端pad_n;所述第二上拉器件包括第四p型场效应管和第九n型场效应管,所述第四p型场效应管的源极和所述第九n型场效应管的漏极均与所述第二p型场效应管的漏极连接,所述第四p型场效应管的漏极和所述第九n型场效应管的源极均连接所述第二差分信号输出端pad_p;所述第一下拉器件包括第六n型场效应管,所述第六n型场效应管的漏极与所述第三p型场效应管的漏极和所述第八n型场效应管的源极的结合点连接,所述第六n型场效应管的源极与所述第五n型场效应管的漏极连接;所述第二下拉器件包括第七n型场效应管,所述第七n型场效应管的漏极与所述第四p型场效应管的漏极和所述第九n型场效应管的源极的结合点连接,所述第七n型场效应管的源极与所述第五n型场效应管的漏极连接。

8、在一个可能的设计中,所述第一上拉器件包括第三p型场效应管、第八n型场效应管和第四电阻,所述第三p型场效应管的源极和所述第八n型场效应管的漏极均与所述第二p型场效应管的漏极连接,所述第三p型场效应管的漏极和所述第八n型场效应管的源极均通过所述第四电阻连接所述第一差分信号输出端pad_n;所述第二上拉器件包括第四p型场效应管、第九n型场效应管和第五电阻,所述第四p型场效应管的源极和所述第九n型场效应管的漏极均与所述第二p型场效应管的漏极连接,所述第四p型场效应管的漏极和所述第九n型场效应管的源极均通过所述第五电阻连接所述第二差分信号输出端pad_p;所述第一下拉器件包括第六n型场效应管和第六电阻,所述第六n型场效应管的漏极依次通过所述第六电阻和所述第四电阻与所述第三p型场效应管的漏极和所述第八n型场效应管的源极的结合点连接,所述第六n型场效应管的源极与所述第五n型场效应管的漏极连接;所述第二下拉器件包括第七n型场效应管和第七电阻,所述第七n型场效应管的漏极依次通过所述第七电阻和所述第五电阻与所述第四p型场效应管的漏极和所述第九n型场效应管的源极的结合点连接,所述第七n型场效应管的源极与所述第五n型场效应管的漏极连接。

9、在一个可能的设计中,所述第一上拉器件包括第三p型场效应管,所述第三p型场效应管的源极与所述第二p型场效应管的漏极连接,所述第三p型场效应管的漏极连接所述第一差分信号输出端pad_n;所述第二上拉器件包括第四p型场效应管,所述第四p型场效应管的源极与所述第二p型场效应管的漏极连接,所述第四p型场效应管的漏极连接所述第二差分信号输出端pad_p;所述第一下拉器件包括第六n型场效应管,所述第六n型场效应管的漏极与所述第三p型场效应管的漏极连接,所述第六n型场效应管的源极与所述第五n型场效应管的漏极连接;所述第二下拉器件包括第七n型场效应管,所述第七n型场效应管的漏极与所述第四p型场效应管的漏极连接,所述第七n型场效应管的源极与所述第五n型场效应管的漏极连接。

10、在一个可能的设计中,所述第一上拉器件包括第三p型场效应管和第四电阻,所述第三p型场效应管的源极与所述第二p型场效应管的漏极连接,所述第三p型场效应管的漏极通过所述第四电阻连接所述第一差分信号输出端pad_n;所述第二上拉器件包括第四p型场效应管和第五电阻,所述第四p型场效应管的源极与所述第二p型场效应管的漏极连接,所述第四p型场效应管的漏极通过所述第五电阻连接所述第二差分信号输出端pad_p;所述第一下拉器件包括第六n型场效应管和第六电阻,所述第六n型场效应管的漏极依次通过所述第六电阻和所述第四电阻与所述第三p型场效应管的漏极连接,所述第六n型场效应管的源极与所述第五n型场效应管的漏极连接;所述第二下拉器件包括第七n型场效应管和第七电阻,所述第七n型场效应管的漏极依次通过所述第七电阻和所述第五电阻与所述第四p型场效应管的漏极连接,所述第七n型场效应管的源极与所述第五n型场效应管的漏极连接。

11、本发明公开了一种兼容lvds电平标准与slvs电平标准的芯片输出驱动电路,与传统技术中同时包括lvds驱动电路和slvs驱动电路的芯片输出驱动电路的结构不同,本发明使用一套电路即可实现lvds电平标准与slvs电平标准两种电平标准的输出,利于减小芯片自身负载影响,可有效避免芯片速度受限的问题;此外,本发明采用分时复用的电路结构,简化了外围电路设计,利于节省芯片面积和走线资源。

- 还没有人留言评论。精彩留言会获得点赞!