一种减小高精度DAC输出干扰脉冲的方法及设备与流程

本发明涉及电子电路,具体涉及一种减小高精度dac输出干扰脉冲的方法及设备。

背景技术:

1、在设计和优化高精度数模转换器(dac)以减小输出干扰脉冲时,常见的两种方法各有其局限性。首先,一种策略是对dac的数字码字进行严格同步处理,确保它们在时间上准确无误地并行馈入到dac阵列中,从而避免因不同开关路径间的不一致性导致的瞬态干扰。然而,即便进行了同步操作,由于实际硬件中的物理差异,各个开关器件之间仍然难以完全消除时延差,这会继续造成一定程度的干扰脉冲出现在输出信号中。

2、另一种常用的手段是在dac的输出端添加一个大容量电容来滤波,通过储能元件吸收瞬间变化的能量,从而减少干扰脉冲的幅度。这种方法虽然在理论上可以减弱噪声,但在实际应用中存在显著问题。当需要进一步降低干扰脉冲至非常小的水平时,可能需要配置一个相当大的电容值,这不仅会增加系统成本和面积,而且过大的电容还会显著延长dac的建立时间,即从输入数字信号改变到模拟输出达到稳定状态所需的时间。

3、因此,尽管上述两种技术在一定程度上能够改善高精度dac的输出质量,降低干扰脉冲,但它们同时也对dac的关键性能指标——建立时间带来了不利影响,并且无法保证将干扰脉冲降至极低水平,特别是在对响应速度和输出信号精度要求极高的应用场景下,需要寻求更先进的综合解决方案来有效克服这些挑战。

技术实现思路

1、针对上述存在的技术不足,本发明要解决的技术问题是提供一种减小高精度dac输出干扰脉冲的方法及设备,只在不影响dac输出的建立时间的情况下降低输出干扰脉冲。

2、为解决上述技术问题,本发明采用如下技术方案:本发明提供一种减小高精度dac输出干扰脉冲的方法,包括:在dac中增加的一个控制开关;其中,所述dac包括:电阻串dac、mdac或r-2r dac;所述控制开关分别位于dac的输出节点的输出端,形成dac的另一个输出节点,用于减小dac输入码字d0-dn切换时输出的干扰脉冲。

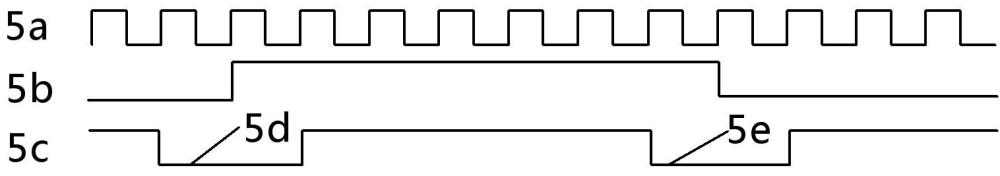

3、进一步地,所述dac的输入码字d0-dn通过同步时钟信号同步后产生相应开关阵列的控制信号控制dac的开关阵列的切换,所述控制开关的相应控制信号在所述dac的开关阵列切换前控制其控制开关断开,至该控制开关的相应控制信号再次切换后导通。

4、进一步地,所述控制开关的相应控制信号在dac的输出节点的输出端输出干扰脉冲达到预设区间时从低电平切换至高电平;

5、其中,所述电阻串dac、mdac和r-2r dac各自的输出节点分别为第一输出节点、第三输出节点和第五输出节点;所述电阻串dac、mdac和r-2r dac各自的另一个输出节点分别为第二输出节点、第四输出节点和第六输出节点。

6、进一步地,在电阻串dac中,

7、在第一开关阵列的控制信号从低电平切换到高电平之前/之时,第一控制开关的控制信号从高电平切换至低电平,第一控制开关在第一开关阵列切换前断开,第二输出节点保持为切换前的稳态电压值;

8、当第一输出节点处输出干扰脉冲达到预设区间时,第一控制开关的控制信号从低电平切换至高电平,第一控制开关导通,此时第二输出节点处的电压值与第一输出节点处的电压值相等。

9、进一步地,还包括,在第一开关阵列的控制信号从高电平切换到低电平之前/之时,第一控制开关的控制信号从高电平切换至低电平,第一控制开关在第一开关阵列切换前断开,第二输出节点保持为切换前的稳态电压值。

10、进一步地,在mdac中,

11、在第二开关阵列的控制信号从低电平切换到高电平之前/之时,第二控制开关的控制信号从高电平切换至低电平,第二控制开关在第二开关阵列切换前断开,第四输出节点保持为切换前的稳态电压值;

12、当第三输出节点处输出干扰脉冲达到预设区间时,第二控制开关的控制信号从低电平切换至高电平,第二控制开关导通,此时第四输出节点处的电压值与第三输出节点处的电压值相等。

13、进一步地,还包括,在第二开关阵列的控制信号从高电平切换到低电平之前/之时,第二控制开关的控制信号从高电平切换至低电平,第二控制开关在第二开关阵列切换前断开,第四输出节点电压保持为切换前的稳态电压值。

14、进一步地,在r-2r dac中,

15、在第三开关阵列的控制信号从低电平切换到高电平之前/之时,第三控制开关的控制信号从高电平切换至低电平,第三控制开关在第三开关阵列切换前断开,第六输出节点节点由于寄生电容仍然保持为切换前的稳态电压值;

16、当第五输出节点处输出干扰脉冲达到预设区间时,第三控制开关的控制信号从低电平切换至高电平,第三控制开关导通,此时第六输出节点处的电压值与第五输出节点处的电压值相等。

17、进一步地,还包括,在第三开关阵列的控制信号从高电平切换到低电平之前/之时,第三控制开关的控制信号从高电平切换至低电平,第三控制开关在第三开关阵列切换前断开,第六输出节点电压保持为切换前的稳态电压值。

18、一种减小高精度dac输出干扰脉冲的设备,包括:

19、存储器和处理器;

20、所述存储器用于存储计算机可执行指令,所述处理器用于执行所述计算机可执行指令,该计算机可执行指令被处理器执行时实现任一所述一种减小高精度dac输出干扰脉冲的方法的步骤。

21、本发明的有益效果在于:本发明通过在dac输出增加控制开关,在dac码字切换时或切换前将开关断开,在切换完成至输出干扰脉冲幅度很小时再将控制开关打开,dac输出干扰脉冲将不会被后级看到,减小甚至消除了dac输出干扰脉冲。

技术特征:

1.一种减小高精度dac输出干扰脉冲的方法,其特征在于,包括:在dac中增加的一个控制开关;其中,所述dac包括:电阻串dac、mdac或r-2r dac;所述控制开关分别位于dac的输出节点的输出端,形成dac的另一个输出节点,用于减小dac输入码字d0-dn切换时输出的干扰脉冲。

2.如权利要求1所述的一种减小高精度dac输出干扰脉冲的方法,其特征在于,所述dac的输入码字d0-dn通过同步时钟信号同步后产生相应开关阵列的控制信号控制dac的开关阵列的切换,所述控制开关的相应控制信号在所述dac的开关阵列切换前控制其控制开关断开,至该控制开关的相应控制信号再次切换后导通。

3.如权利要求1或2所述的一种减小高精度dac输出干扰脉冲的方法,其特征在于,所述控制开关的相应控制信号在dac的输出节点的输出端输出干扰脉冲达到预设区间时从低电平切换至高电平;

4.如权利要求2所述的一种减小高精度dac输出干扰脉冲的方法,其特征在于,在电阻串dac中,

5.如权利要求4所述的一种减小高精度dac输出干扰脉冲的方法,其特征在于,还包括,在第一开关阵列的控制信号从高电平切换到低电平之前/之时,第一控制开关的控制信号从高电平切换至低电平,第一控制开关在第一开关阵列切换前断开,第二输出节点保持为切换前的稳态电压值。

6.如权利要求2所述的一种减小高精度dac输出干扰脉冲的方法,其特征在于,在mdac中,

7.如权利要求6所述的一种减小高精度dac输出干扰脉冲的方法,其特征在于,还包括,在第二开关阵列的控制信号从高电平切换到低电平之前/之时,第二控制开关的控制信号从高电平切换至低电平,第二控制开关在第二开关阵列切换前断开,第四输出节点电压保持为切换前的稳态电压值。

8.如权利要求2所述的一种减小高精度dac输出干扰脉冲的方法,其特征在于,在r-2rdac中,

9.如权利要求8所述的一种减小高精度dac输出干扰脉冲的方法,其特征在于,还包括,在第三开关阵列的控制信号从高电平切换到低电平之前/之时,第三控制开关的控制信号从高电平切换至低电平,第三控制开关在第三开关阵列切换前断开,第六输出节点电压保持为切换前的稳态电压值。

10.基于如权利要求1所述的一种减小高精度dac输出干扰脉冲的方法的设备,其特征在于,包括:

技术总结

本发明涉及电子电路技术领域,公开了一种减小高精度DAC输出干扰脉冲的方法及设备,包括:在DAC中增加的一个控制开关;其中,DAC包括:电阻串DAC、MDAC或R‑2R DAC;控制开关分别位于DAC的输出节点的输出端,形成DAC的另一个输出节点,用于减小DAC输入码字D0‑Dn切换时输出的干扰脉冲。本发明通过在DAC输出增加控制开关,在DAC码字切换时或切换前将开关断开,在切换完成至输出干扰脉冲幅度很小时再将控制开关打开,DAC输出干扰脉冲将不会被后级看到,减小甚至消除了DAC输出干扰脉冲。

技术研发人员:沈娇,侯惠淇,常路讯,力争,陈涛

受保护的技术使用者:南京朗立微集成电路有限公司

技术研发日:

技术公布日:2024/5/16

- 还没有人留言评论。精彩留言会获得点赞!