基于量子密钥分发控制器的发光数据驱动接口标准电路的制作方法

1.本发明涉及量子通信领域,具体涉及基于量子密钥分发(qkd)控制器的发光数据驱动接口标准电路,其能兼容多种基于bb84协议的光子编码信息发送模式。

背景技术:

2.现有的量子密钥分发系统一般采用一到多块intel或xilinx fpga来构成控制器,在控制器内部,数据发送逻辑电路从输入的真随机数比特流(可以由真随机数发生器trng生成)中抽取一定长比特数,组合映射成所谓光子信息数据(或称发光数据),形成原始光子信息流。原始光子信息流一方面被送至片外主存储区保存以备后续读回并进行后续数据处理(如基矢比对);另一方面控制器需要根据每个光子信息数据,按照发光速率通过不同信号通道将数据发送至光源子系统内的驱动电路,以驱动dfb激光器发出光脉冲,或者驱动光强度调制器(im)/相位调制器(pm),视光脉冲调制机制不同,信号通道数有不同数量的场景。例如,相位调制需要3路,基于诱骗态的偏振调制需要8路。

3.图1示出了现有技术的一种量子密钥分发系统的控制器结构。如图所示,控制器采用fpga内嵌的多个高速串行解串器(serdes)电路发送光子信息流至片外,并通过pcb板连接至光源子系统的发光驱动电路中以根据bb84协议来实现光脉冲的生成。

4.将随机数调制到qkd光源有多种调制机制来实现bb84协议,其中偏振与相位调制是两种应用最广泛的方式。为了增强安全性,有些系统还发送诱骗态信号。此外,高成码率始终是qkd系统追求的目标之一,所以不同应用场景对发光速率要求也会不同,如有40mhz、625mhz、1.25ghz等。这些不同要求综合起来使得从控制器输出的信号通道数、信号输出速率和对信号传输的电气特性要求相差很大。qkd系统要求多通道信号传输时各通道间信号延时抖动不超过20ps,无论是采用分立芯片通过pcb连接、还是独立设计专用接口电路,这是一个超出常规cmos工艺技术的最低延时抖动限度。

5.目前为止,qkd系统并没有统一的控制器到光源的数据传输标准接口,不同研制者、不同应用场景、不同调制机制采用接口方式都不同,这给来自不同研制单位qkd控制器与光源模块互连带来不便,间接造成系统成本增加。

6.同时,目前市场上还未出现qkd控制器专用芯片,所有系统设备商都还是采用fpga作为其主控器和数据处理芯片,从主控到发光单元之间采用fpga嵌入的多个serdes来实现光子信息数据的发送,尤其发光速率较高时,serdes通道必不可少。然而,本发明人发现,采用通用fpga及其本身的serdes资源来实现发光数据信息与发光单元间接口至少存在以下技术不足:

7.1.对于采用fpga的系统,上电后需要从外部读出fpga配置代码对fpga进行重新配置,对所用fpga高速接口资源进行配置包含在其中。

8.2.fpga发送接口电路通道间不存在耦合关系,理论上不同芯片serdes通道间存在较大延时差,尽管采用现代纳米cmos工艺的fpga的serdes通道间延时差可以小至20ps级。

9.3.serdes是一种高性能的高速数据收发双向电路,内部含有编解码(如8b10b)、模

拟与数字均衡、时钟数据恢复(cdr)等复杂电路,而qkd光子信息数据只需要单向发送,无需serdes内含有的上述功能电路,采用serdes来发送发光数据存在资源浪费问题。

10.4.在fpga供应不足或其高速通道数量不足、或者通道间延时抖动很大情况下,采用其他通用芯片来构建发送数据通道十分不便。

技术实现要素:

11.针对现有技术的上述问题,本发明提出了一种可适用多种应用场景且能够同时发送多通道数据的发光数据驱动接口标准电路,其可用以取代fpga中不相干的多通道serdes。本发明的发光数据驱动接口标准电路不仅适合集成于qkd主控器专用集成电路(asic)内,使得单颗qkd主控器asic能够取代一到多颗fpga的使用,同时具备用于将光子信息数据发送到光源驱动电路的接口;同时该标准电路还适合以独立接口asic的形式实现qkd控制器芯片与发光驱动电路芯片之间的连接。

12.根据本发明,基于量子密钥分发控制器的发光数据驱动接口标准电路可以包括单个锁相环模块和多个数据通道模块,其中:

13.所述单个锁相环模块被设置用于向所述数据通道模块提供时钟驱动信号,以驱动所述数据通道模块内光子信息数据的发送;

14.所述数据通道模块被设置成单向地实现所述光子信息数据从所述量子密钥分发控制器到发光驱动电路的耦合发送,允许调节所述光子信息数据的发送波特率,以及允许对所述光子信息数据的输出模式进行配置。

15.进一步地,所述锁相环模块可以包括锁相环和偏置单元,其中:所述锁相环用于接收外部参考时钟信号,并基于所述外部参考时钟信号向所述数据通道模块提供时钟驱动信号;所述偏置单元用于向所述锁相环和所述数据通道模块提供偏置信号。

16.进一步地,本发明的发光数据驱动接口标准电路还可以包括:第一类接口refclk,其用于输入外部参考时钟信号;第三类接口txn_data,其用于输入所述光子信息数据;第四类接口txnp,其用作所述数据通道模块的差分输出正向端;第五类接口txnm,其用作所述数据通道模块的差分输出负向端;第六类接口baudrate,其用于输入所述光子信息数据的发送波特率的调节信号;以及,第七类接口txn_output_mode,其用于输入所述光子信息数据的输出模式的配置信号。

17.更进一步地,本发明的发光数据驱动接口标准电路还可以包括模拟电源输入接口vdda、模拟地接口vssa、数字电源输入接口vdd和数字地接口vss中的至少一个。

18.更进一步地,所述第一类接口refclk、第三类接口txn_data、第六类接口baudrate和第七类接口txn_output_mode可以为数字输入接口,第四类接口txnp和第五类接口txnm为模拟输出接口

19.更进一步地,所述配置信号可以被设置用于将所述光子信息数据的输出模式配置为cml或lvds。

20.进一步地,所述数据通道模块包括多路器单元、并行到串行转换单元、前向均衡电路单元、驱动器单元、伪随机序列发生器和伪随机序列检测单元。

21.更进一步地,所述多路器单元被设置成可接收所述光子信息数据和所述伪随机序列发生器的结果,并根据开关信号txn_test_en选择输出所述伪随机序列发生器的结果或

者所述光子信息数据。

22.更进一步地,所述并行到串行转换单元用于接收来自所述多路器单元的输出,且被设置成在所述锁相环模块提供的所述时钟驱动信号作用下将并行输入的数据逐一转换成差分信号。

23.更进一步地,所述前向均衡电路单元用于接收所述并行到串行转换单元输出的差分信号,且被设置成对所述差分信号进行预加重处理。其中,所述预加重处理的预加重系数可以由外部予以配置。

24.更进一步地,所述驱动器单元用于接收所述前向均衡电路单元输出的差分信号和来自所述锁相环模块的偏置信号,且被设置成根据配置信号选择以cml或lvds模式输出所述差分信号。

25.更进一步地,所述数据通道模块还可以被设置成:在内部测试状态下,由所述伪随机序列发生器输出的结果在所述驱动器单元的输出端处被返回至所述伪随机序列检测单元,以对所述结果进行检测并向外输出检测结果。

26.进一步地,本发明的发光数据驱动接口标准电路还可以包括第八类接口txn_bist_o,其用于向外输出所述伪随机序列检测单元的检测结果。

27.进一步地,本发明的发光数据驱动接口标准电路还可以包括第二类接口pll_lock,其用于显示内部pll的锁定;并且/或者,所述第三类接口txn_data的数量被设置成为允许对应于所述数据通道模块中的每一个,由外部输入的并行数据字长最多为10比特宽。

28.优选地,所述驱动器单元的输出端处可以设有片内电阻。所述数据通道模块可以被配置为8个。

附图说明

29.图1示意性地示出了现有技术的量子密钥分发系统控制器结构;

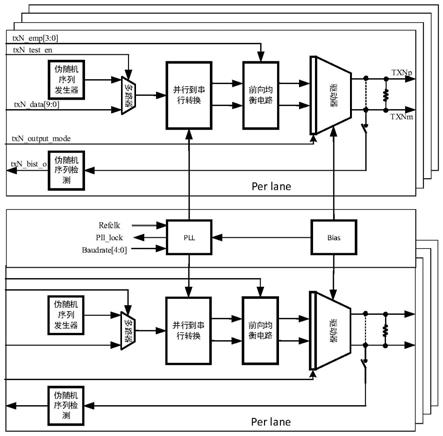

30.图2示意性地示出了本发明的基于量子密钥分发控制器的发光数据驱动接口标准电路的一种示例性结构。

具体实施方式

31.在下文中,本发明的示例性实施例将参照附图来详细描述。下面的实施例以举例的方式提供,以便充分传达本发明的精神给本发明所属领域的技术人员。因此,本发明不限于本文公开的实施例。

32.图2示出了本发明的基于量子密钥分发(qkd)控制器的发光数据驱动接口标准电路的一种示例性结构。

33.如图所示,该标准电路可以包括单个锁相环(pll)模块和多个数据通道模块。作为示例,数据通道模块可以被配置为8个。

34.在本发明的发光数据驱动接口标准电路中,该锁相环模块被设置用于向各个数据通道模块提供时钟驱动信号,以驱动各数据通道模块内的数据发送,同时精确且可控地在标准电路内建立起各个数据通道模块之间的相位关系,由此从数据源头上减少各个数据通道模块之间的延时差。

35.相应地,对应于该锁相环模块,本发明的标准电路可以包括第一类接口refclk,其

作为数字输入接口,用于输入外部参考时钟信号。此外,本发明的标准电路还可以包括第二类接口pll_lock,其作为数字输出接口,用于显示内部pll的锁定。

36.如图2所示,作为一种具体实现方式,锁相环模块可以包括锁相环和偏置单元bias。其中,锁相环接收外部参考时钟信号,并基于此向标准电路中的各个数据通道模块提供时钟驱动信号;偏置单元用于向锁相环和标准电路中的数据通道模块提供偏置信号。

37.根据本发明,数据通道模块可以被设置成单向地实现光子信息数据从qkd控制器(芯片)到发光驱动电路(芯片)的直流耦合发送。

38.相应地,对应于数据通道模块,本发明的标准电路还可以包括:第三类接口txn_data,其作为数字输入接口,用于输入光子信息数据;第四类接口txnp,其作为模拟输出接口,充当第n个数据通道模块的差分输出正向端;以及第五类接口txnm,其作为模拟输出接口,充当第n个数据通道模块的差分输出负向端。

39.根据本发明,第三类接口txn_data可以被配置为多个。例如,第三类接口txn_data的数量可以被设置成为允许对应于每个数据通道模块,由外部输入的并行数据字长最多为10比特宽,如图2所示那样。

40.在本发明中,数据通道模块还可以被设置成允许调节数据发送波特率。相应地,本发明的标准电路还可以包括第六类接口baudrate,其作为数字输入接口,用于输入光子信息数据输出速率的调节信号。

41.在本发明中,数据通道模块还可以被设置成允许将光子信息数据输出模式配置为cml(current mode logic,电流模式逻辑)或lvds(low-voltage differential signaling,低电压差分信号)。相应地,本发明的标准电路还可以包括第七类接口txn_output_mode,其作为数字输入接口,用于输入光子信息数据输出模式的配置信号。根据该配置信号,数据通道模块可以在cml和lvds之间择一作为光子信息数据的输出模式。

42.此外,本发明的标准电路中还可以包括模拟电源输入接口vdda、模拟地接口vssa、数字电源输入接口vdd和数字地接口vss。

43.进一步参见图2,作为一种具体实现方式,数据通道模块可以包括多路器单元、并行到串行转换单元、前向均衡电路单元、驱动器单元、伪随机序列发生器和伪随机序列检测单元。

44.根据本发明,多路器单元可以被设置成其输入端连接伪随机序列发生器和第三类接口txn_data,并根据开关信号txn_test_en选择输出来自伪随机序列发生器的输入或者来自第三类接口txn_data的输入。

45.并行到串行转换单元用于接收来自多路器单元的输出,且被设置成在锁相环模块提供的pll时钟驱动信号作用下将并行输入数据从低比特到高比特地逐一转换成差分信号。

46.前向均衡电路单元用于接收来自并行到串行转换单元的输出,且被设置成对差分信号进行预加重处理。本发明中,预加重系数可以由外部予以配置,例如图2中所示,借助配置信号txn_emp来实现。

47.驱动器单元用于接收来自前向均衡电路单元的输出和来自锁相环模块的偏置信号,且被设置成根据由第七类接口txn_output_mode输入的配置信号选择以cml或lvds模式输出差分信号。

48.根据本发明,数据通道模块还可以被设置成在内部测试状态下,由伪随机序列发生器输出的数据在驱动器单元的输出端处被返回至伪随机序列检测单元,其中,伪随机序列检测单元对该数据进行检测并向外输出检测结果。相应地,本发明的标准电路还可以包括第八类接口txn_bist_o,其作为数字输出接口,用于输出伪随机序列检测单元的检测结果。

49.作为优选示例,可以在驱动器单元的输出端处设置片内电阻。作为示例,该片内电阻可以具有50欧姆的阻值。

50.由此可见,本发明设计一种可高速同时发送多通道数据的发光数据驱动接口标准电路,其可用以取代现有技术的fpga中不相干的多通道serdes。并且,本领域技术人员容易理解,本发明的发光数据驱动接口标准电路不仅适合集成于qkd主控器专用集成电路(asic)内,使得单颗qkd主控器asic能够取代一到多颗fpga的使用,同时具备用于将光子信息数据发送到光源驱动电路的接口;同时该标准电路还适合以独立接口asic的形式实现qkd控制器芯片与发光驱动电路芯片之间的连接,从而统一qkd控制器asic或fpga到发光系统的接口方式,为未来第三方qkd专用处理器的推出提供接口标准,也为光源数据输入标准化奠定基础,有助于提高qkd处理控制器的通用性和qkd系统模块化。进一步地,本发明所提出的由单一pll电路模块驱动接口中的多个数据差分输出通道模块的电路架构可以有效地改善多个数据通道之间的时间延迟效应,极大提高成码率。通过在接口标准电路中引入通道数据波特率调节和差分输出模式配置功能,使其能够适应不同应用场景对于信号输出速率和信号传输电气特性要求的需求。

51.下表示例性地说明了本发明的发光数据驱动接口标准电路中的各种信号/接口的定义。

[0052][0053][0054]

尽管前面结合附图通过具体实施例对本发明进行了说明,但是,本领域技术人员容易认识到,上述实施例仅仅是示例性的,用于说明本发明的原理,其并不会对本发明的范围造成限制,本领域技术人员可以对上述实施例进行各种组合、修改和等同替换,而不脱离本发明的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1