高频模块以及通信装置的制作方法

1.本发明涉及高频模块以及通信装置。

背景技术:

2.在专利文献1中公开了电路部件内置模块(高频模块)的结构,该结构在多层电路基板的第一主面安装有表面安装部件,在第二主面安装有半导体元件。在该电路部件内置模块中,在俯视多层电路基板的情况下,将多个通孔以及焊盘配置为包围半导体元件。由此,电路部件内置模块作为高频动作、抗噪声性、散热性、小型化优异的高频模块是有用的。

3.专利文献1:日本特开2007-281160号公报

4.然而,如专利文献1所公开的电路部件内置模块(高频模块)那样,在上述俯视时,由多个通孔以及焊盘包围半导体元件(半导体ic)的情况下,在第二主面上的半导体元件(半导体ic)的配置自由度受到限制。进一步,由于半导体元件的配置自由度受到限制,所以例如难以使与配置于第一主面的表面安装部件的连接布线最佳化(最短化),而存在高频传输特性劣化的可能性。另外,由于将具有相同直径的多个通孔以及焊盘配置为与半导体元件(半导体ic)的所有外边对置,所以需要用于配置该通孔以及焊盘的较大的空间。因此,无法使多层电路基板小型化,例如在外部(母)基板配置电路部件内置模块(高频模块)的自由度受到限制。

5.像这样,在专利文献1所公开的电路部件内置模块(高频模块)中,虽然通过将相同直径的多个通孔以及焊盘配置为包围半导体元件(半导体ic),能够在某种程度确保高频动作和抗噪声性等电气性能以及安装强度等机械性能,但存在无法确保与半导体元件(半导体ic)的配置相关的设计自由度以及起因于高频模块的尺寸的设计自由度这样的问题。

技术实现要素:

6.因此,本发明是为了解决上述课题而完成的,目的在于提供提高了设计自由度,而不使电气以及机械性能劣化的高频模块以及通信装置。

7.为了实现上述目的,本发明的一个方式的高频模块具备:模块基板,具有第一主面和第二主面;半导体ic,处理高频信号,上述半导体ic具有第三主面和第四主面,按照上述模块基板、上述第三主面以及上述第四主面的顺序安装在上述第一主面上;多个第一连接电极,在上述第一主面的垂直方向上从上述第一主面至少延伸到包含上述第四主面的第一虚拟平面;以及多个第二连接电极,在上述垂直方向上从上述第一主面至少延伸到上述第一虚拟平面,上述第二连接电极的与上述第一主面平行的剖面的面积比上述多个第一连接电极中的每一个第一连接电极的与上述第一主面平行的剖面的面积小,在俯视上述模块基板的情况下,上述半导体ic的外边缘包括:第一边、第二边、第三边以及第四边,上述第一边和上述第二边相互平行,上述第三边和上述第四边与上述第一边和上述第二边正交,且相互平行,在上述模块基板上的第一区域以及第二区域分别配置有上述多个第一连接电极中的几个上述第一连接电极,其中,上述第一区域是构成上述模块基板的外边缘的多个边中

的与上述第一边对置的边和上述第一边之间的区域,上述第二区域是上述多个边中的与上述第二边对置的边和上述第二边之间的上述模块基板上的区域,在上述多个边中的与上述第三边对置的边和上述第三边之间的上述模块基板上的第三区域配置有上述多个第二连接电极中的几个上述第二连接电极,而未配置上述多个第一连接电极。

8.根据本发明,能够提供提高了设计自由度,而不使电气以及机械性能劣化的高频模块以及通信装置。

附图说明

9.图1是表示实施方式1的通信装置的电路结构的一个例子的电路框图。

10.图2是表示实施方式1的内置于半导体ic的电路元件的配置的一个例子的平面示意图。

11.图3a是实施方式1的高频模块的平面结构示意图。

12.图3b是实施方式1的高频模块的剖面结构示意图。

13.图4是实施方式1的变形例的高频模块的平面结构示意图。

14.图5a是实施方式2的高频模块的剖面结构示意图。

15.图5b是比较例1的高频模块的剖面结构示意图。

16.图5c是比较例2的高频模块的剖面结构示意图。

17.图5d是比较例3的高频模块的剖面结构示意图。

18.图6是表示实施方式3的高频模块的平面结构以及剖面结构的示意图。

19.图7是表示实施方式3的变形例的高频模块的平面结构以及剖面结构的示意图。

具体实施方式

20.以下,使用实施方式及其附图对本发明的实施方式进行详细说明。此外,以下说明的实施方式均表示概括性或者具体的例子。在以下的实施方式中示出的数值、形状、材料、构成要素、构成要素的配置以及连接方式等是一个例子,主旨并不是对本发明进行限定。对于以下的实施方式中的构成要素中未记载于独立权利要求的构成要素,作为任意的构成要素进行说明。另外,附图所示的构成要素的大小或者大小之比未必严格。

21.(实施方式1)

22.[1.1通信装置以及高频模块的电路结构]

[0023]

图1是表示实施方式1的通信装置5的电路结构的一个例子的电路块结构图。如该图所示,通信装置5具备:高频模块1、天线元件2、rf信号处理电路(rfic)3以及基带信号处理电路(bbic)4。高频模块1例如配置于对应多模/多频段的移动电话的前端部。

[0024]

rfic3是对通过天线元件2收发的高频信号进行处理的rf信号处理电路。具体而言,rfic3通过下变频等,对经由高频模块1的输出端子102输入的高频信号进行信号处理,并将通过该信号处理生成的接收信号输出至bbic4。

[0025]

bbic4是使用比在高频模块1中传输的高频信号低频的中间频带进行信号处理的电路。通过bbic4处理的信号例如作为用于图像显示的图像信号来使用、或者为了经由扬声器的通话而作为声音信号来使用。

[0026]

天线元件2与高频模块1的共用端子101连接,接收来自外部的高频信号并输出至

高频模块1。

[0027]

此外,在本实施方式的通信装置5中,天线元件2以及bbic4并不是必需的构成要素。

[0028]

接下来,对高频模块1的详细结构进行说明。

[0029]

高频模块1具备:数字控制电路11、开关12、13及14、电感器31、低噪声放大器41、以及滤波器21及22。

[0030]

开关12、13及14具有分别切换被输入到高频模块1的高频信号的传输路径的功能。

[0031]

更具体而言,开关12例如具有共用端子以及多个选择端子,切换天线元件2与滤波器21的连接、天线元件2与滤波器22的连接、以及天线元件2与其它滤波器的连接。

[0032]

开关13例如具有共用端子以及两个选择端子,切换滤波器21与电感器31的连接、以及滤波器22与电感器31的连接。

[0033]

开关14例如具有共用端子以及两个选择端子,切换低噪声放大器41与rfic3的连接、以及其它低噪声放大器与rfic3的连接。

[0034]

滤波器21例如是将第一频带作为通带的带通型滤波器,滤波器22例如是将第二频带作为通带的带通型滤波器。

[0035]

此外,滤波器21以及22例如可以是弹性表面波滤波器、使用了baw(bulk acoustic wave:体声波)的弹性波滤波器、lc谐振滤波器、以及电介质滤波器中的任意一种,并且,并不限定于这些滤波器。

[0036]

电感器31是用于取得滤波器21以及22的输出阻抗与低噪声放大器41的输入阻抗的阻抗匹配的匹配元件。此外,对于作为匹配元件的电感器31,例示出串联配置在连结开关13与低噪声放大器41的路径上的结构,但也可以连接在该路径上的节点与地线之间,另外,也可以由一个以上的电感器以及一个以上的电容器构成。另外,典型地,电感器31是安装于模块基板90上的芯片电感器,但例如也可以利用形成于模块基板90内的多个平面线圈构成。

[0037]

低噪声放大器41是对通过了滤波器21或者22的第一频带或者第二频带的高频信号进行放大的低噪声放大器。

[0038]

数字控制电路11内置于半导体ic10。

[0039]

图2是表示内置于实施方式1的半导体ic10的电路元件的配置的一个例子的平面示意图。该图所示的半导体ic10内设置有:数字控制电路11、开关12、13及14、以及低噪声放大器41,数字控制电路11与作为高频电路元件的开关12~14以及低噪声放大器41形成于同一ic基板。

[0040]

半导体ic10例如是由cmos(complementary metal oxide semiconductor:互补金属氧化物半导体)构成。由此,能够低成本地制造半导体ic10。此外,半导体ic10也可以由gaas构成。由此,能够输出具有高质量放大性能以及噪声性能的高频信号。

[0041]

内置于半导体ic10的各电路元件与数字控制电路11分别通过数字控制布线连接。开关12与数字控制电路11通过控制布线112连接,开关13与数字控制电路11通过控制布线113连接,开关14与数字控制电路11通过控制布线114连接,低噪声放大器41与数字控制电路11通过控制布线141连接。

[0042]

通过上述结构,数字控制电路11经由控制布线112向开关12供给用于切换开关12

的导通以及非导通的数字控制信号112s。另外,数字控制电路11经由控制布线113向开关13供给用于切换开关13的导通以及非导通的数字控制信号113s。另外,数字控制电路11经由控制布线114向开关14供给用于切换开关14的导通以及非导通的数字控制信号114s。另外,数字控制电路11经由控制布线141向低噪声放大器41供给用于调整低噪声放大器41的放大率的数字控制信号141s。

[0043]

通过上述结构,高频模块1通过数字控制电路11控制开关12~14以及低噪声放大器41,从而使由天线元件2接收到的高频信号通过适当的信号路径进行传输,并传递到rfic3以及bbic4。

[0044]

此外,在本实施方式中,作为高频模块1例示出具有接收分波电路的高频模块,但本发明的高频模块也可以是发送合波电路、或者也可以是能够进行发送以及接收双方的分波/合波电路。另外,对于频带(信号路径)的数量并不限定。进一步,高频模块1也能够应用于不光仅选择一个信号路径,而能够同时接收多个频带的高频信号的系统。在该情况下,例如,开关12~14可以分别具有能够同时连接共用端子和两个以上的选择端子的结构。

[0045]

进一步,本发明的高频模块至少具有构成实施方式1的高频模块1的电路元件(电路部件)中的半导体ic10即可。进一步,半导体ic10至少具有数字控制电路11即可,也可以不具有低噪声放大器41以及开关12~14。在该情况下,低噪声放大器41以及开关12~14也可以作为独立部件配置于半导体ic10以外的高频模块1。

[0046]

[1.2高频模块的电路元件配置结构]

[0047]

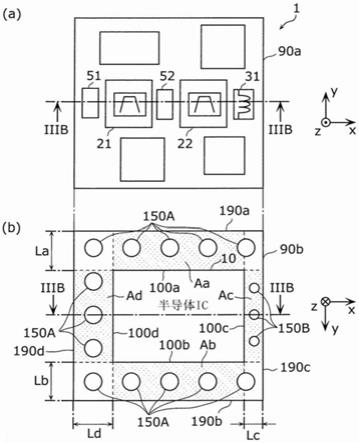

图3a是实施方式1的高频模块1的平面结构示意图。另外,图3b是实施方式1的高频模块1的剖面结构示意图,具体而言,是图3a的iiib-iiib线上的剖视图。此外,在图3a的(a)示出从z轴正方向侧观察模块基板90的主面90a以及90b中的主面90a的情况下的电路元件的配置图。另一方面,在图3a的(b)示出从y轴负方向侧观察主面90b的情况下的电路元件的配置图。

[0048]

如图3a以及图3b所示,本实施方式的高频模块1具有:模块基板90、半导体ic10、多个柱状电极150a以及多个柱状电极150b、滤波器21及22、电感器31、电路元件51及52、树脂部件80a及80b。

[0049]

模块基板90是具有主面90a(第二主面)以及主面90b(第一主面),并安装半导体ic10、滤波器21及22、电感器31、以及电路元件51及52的基板。作为模块基板90,例如可使用具有多个电介质层的层叠结构的低温共烧陶瓷(low temperature co-fired ceramics:ltcc)基板、或者印刷电路基板等。

[0050]

滤波器21及22、电感器31、以及电路元件51及52安装于主面90a。滤波器21及22、电感器31、以及电路元件51及52分别经由形成于模块基板90的主面90a的焊盘电极和凸块或者焊料等,与模块基板90电连接并机械连接。

[0051]

虽然在图1所示的高频模块1的电路结构中未示出电路元件51以及52,但其为构成高频模块1的其它电路元件,例如相当于滤波器、开关、电感器、电容器等。

[0052]

此外,模块基板90是能够在主面90a以及90b这两面安装电路元件的基板,但也可以不在主面90a安装滤波器21及22、电感器31、以及电路元件51及52等电路元件。

[0053]

半导体ic10具有主面10a(第三主面)以及主面10b(第四主面),在俯视主面10a以及10b的情况下,具有矩形形状的外形。半导体ic10安装在主面90b上,使得主面10a与模块

基板90的主面90b对置。半导体ic10经由形成于模块基板90的主面90b的焊盘电极和凸块或者焊料等与模块基板90电连接并且机械连接。

[0054]

此外,半导体ic10具有矩形形状的外形,但角部也可以带有倒角或者圆角,另外,也可以在外边缘部具有切口部。

[0055]

另外,安装于主面90a的电路元件间的电连接、内置于安装于主面90b的半导体ic10的各元件间的电连接、以及安装于主面90a的电路元件与半导体ic10的电连接通过形成于主面90a和90b以及模块基板90的内部的平面布线图案和通孔导体来实现。

[0056]

此外,所谓的平面布线图案是指沿着与模块基板90的主面90a以及90b平行的方向形成的导电膜,所谓的通孔导体是指在与模块基板90的主面90a以及90b垂直的方向上延伸的柱状导体。

[0057]

树脂部件80a配置于模块基板90的主面90a,覆盖安装于主面90a的电路元件的至少一部分以及主面90a,具有确保上述电路元件的机械强度以及耐湿性等可靠性的功能。树脂部件80b配置于模块基板90的主面90b,覆盖半导体ic10以及主面90b,具有确保半导体ic10的机械强度以及耐湿性等可靠性的功能。此外,树脂部件80b无需覆盖主面90b以及半导体ic10的全部,可以覆盖其一部分。例如,树脂部件80b也可以仅填充在半导体ic10与主面90b之间。此外,树脂部件80a以及80b并不是本发明的高频模块必需的构成要素。

[0058]

在图3b中剖视模块基板90的情况下,柱状电极150a是在主面90b的垂直方向(z轴方向)上从主面90b至少延伸到包含主面10b的虚拟平面100p(第一虚拟平面)的第一连接电极。另外,在图3b中剖视模块基板90的情况下,柱状电极150b是在主面90b的垂直方向(z轴方向)上从主面90b至少延伸至虚拟平面100p的第二连接电极。柱状电极150b的与主面90b平行的剖面积比柱状电极150a的与主面90b平行的剖面积小。在本实施方式中,柱状电极150a以及150b具有圆柱形状,柱状电极150b的与主面90b平行的剖面直径比柱状电极150a的与主面90b平行的剖面直径小。

[0059]

在本实施方式中,柱状电极150a以及150b在主面90b的垂直方向(z轴方向)上从主面90b超过虚拟平面100p延伸到树脂部件80b的表面。柱状电极150a以及150b各自的一端在主面90b与形成于模块基板90的焊盘电极、平面布线图案或者通孔导体电连接。另外,柱状电极150a以及150b各自的另一端在树脂部件80b的表面露出,能够与安装高频模块1的外部(母)基板的电极电连接。柱状电极150a以及150b分别可以是设定为高频模块1的接地电位(gnd)的电极,或者也可以是使在高频模块1中传输的高频信号(hot)导通的电极(例如,图1的共用端子101)。

[0060]

此外,在本实施方式以及后述的实施方式2中,柱状电极150a以及150b可以是圆柱形状,另外,也可以具有棱柱形状等。另外,柱状电极150a以及150b也可以是焊球、或者凸块电极等连接电极,在该情况下,在柱状电极150a以及150b的表面也可以具有球面形状。

[0061]

此外,柱状电极150a以及150b的与主面90b平行的剖面的形状也可以不是正圆,也可以是椭圆、矩形或者多边形。

[0062]

如图3a的(b)所示,半导体ic10的外边缘包含:边100a(第一边)和100b(第二边)、以及边100c(第三边)和100d(第四边),其中,边100a(第一边)和100b(第二边)相互平行,边100c(第三边)和100d(第四边)与边100a以及100b正交,且相互平行。

[0063]

模块基板90的外边缘包含有:相互平行的边190a和190b、以及与边190a和190b正

交且相互平行的边190c和190d。

[0064]

此外,在本说明书中,所谓的两条边平行并不限定于两条边所成的角度严格地为0deg,可定义为两条边所成的角度在

±

15deg以内。

[0065]

在这里,在与边100a对置的边190a和边100a之间的模块基板90上的区域aa(第一区域)、与边100b对置的边190b和边100b之间的模块基板90上的区域ab(第二区域)、以及与边100d对置的边190d和边100d之间的模块基板90上的区域ad中的每一个区域配置有柱状电极150a。另一方面,在与边100c对置的边190c和边100c之间的模块基板90上的区域ac(第三区域)配置有柱状电极150b,而未配置柱状电极150a。

[0066]

此外,所谓的半导体ic10的边与模块基板90的边对置表示在该两条边之间没有半导体ic10的其它边以及模块基板90的其它边的状态。

[0067]

根据上述结构,在俯视模块基板90的情况下,在区域ac代替剖面积较大的柱状电极150a,而配置有剖面积较小的柱状电极150b。由此,与具有在区域aa~ad的全部区域配置有柱状电极150a的结构的高频模块相比,提高半导体ic10的配置自由度,另外,也能够缩小区域ac。换句话说,由于能够实现半导体ic10的配置自由度、或者由模块基板90的缩小所带来的高频模块1的节省面积化,所以高频模块1的设计自由度提高。另一方面,由于在包围半导体ic10的四个区域aa~ad配置有柱状电极150a或者150b,所以能够充分地确保通过半导体ic10以及各电路元件处理的电信号的取出以及接地强化,并且确保高频模块1的向外部基板的安装强度。

[0068]

此外,也可以在上述俯视时,边100c与规定区域ac的模块基板90的边190c的距离lc比边100a与边190a的距离la小,并且,比边100b与边190b的距离lb小。

[0069]

由此,通过配置于包围半导体ic10的四个区域aa~ad的柱状电极150a或者150b,能够充分地确保通过半导体ic10以及各电路元件处理的电信号的取出以及接地强化,确保高频模块1的向外部基板的安装强度,并且实现由缩小模块基板90的区域ac所带来的高频模块1的节省面积化。

[0070]

图4是实施方式1的变形例的高频模块1a的平面结构示意图。该图所示的高频模块1a与实施方式1的高频模块1相比,仅柱状电极150a以及150b的配置结构不同。以下,对于本变形例的高频模块1a,对与实施方式1的高频模块1相同的结构省略说明,而对不同的结构进行说明。

[0071]

在与边100a对置的边190a和边100a之间的模块基板90上的区域aa(第一区域)、以及与边100b对置的边190b和边100b之间的模块基板90上的区域ab(第二区域)中的每一个区域,配置有剖面积较大的柱状电极150a。另一方面,在与边100c对置的边190c和边100c之间的模块基板90上的区域ac(第三区域)、以及与边100d对置的边190d和边100d之间的模块基板90上的区域ad(第四区域)中的每一个区域,配置有剖面积较小的柱状电极150b,而未配置柱状电极150a。

[0072]

根据上述结构,在俯视模块基板90的情况下,在对置的区域ac以及ad,代替剖面积较大的柱状电极150a,而配置有剖面积较小的柱状电极150b。由此,与具有在区域aa~ad的全部区域配置有柱状电极150a的构成的高频模块相比,半导体ic10的配置自由度提高,另外,也能够缩小区域ac以及ad。换句话说,高频模块1a的设计自由度进一步提高。另一方面,由于在包围半导体ic10的四个区域aa~ad配置有柱状电极150a或者150b,所以能够充分地

确保通过半导体ic10以及各电路元件处理的电信号的取出以及接地强化,并且能够进行高频模块1a的向外部基板的安装。

[0073]

[1.3效果等]

[0074]

本实施方式的高频模块1具备:模块基板90,具有主面90a以及90b;半导体ic10,具有主面10a以及10b,按照模块基板90、主面10a、以及主面10b的顺序安装在主面90b上,上述半导体ic10对高频信号进行处理;多个柱状电极150a,在主面90b的垂直方向上从主面90b至少延伸到包含主面10b的虚拟平面100p;以及柱状电极150b,在上述垂直方向上从主面90b至少延伸到虚拟平面100p,且与主面90b平行的剖面的面积比柱状电极150a的与主面90b平行的剖面的面积小。在俯视模块基板90的情况下,半导体ic10的外边缘包括:相互平行的边100a和100b、以及与边100a和100b正交且相互平行的边100c和100d。在与边100a对置的边190a和边100a之间的模块基板90上的区域aa、以及与边100b对置的边190b和边100b之间的模块基板90上的区域ab中的每一个区域,配置有多个柱状电极150a中的几个柱状电极150a。另外,在与边100c对置的边190c和边100c之间的模块基板90上的区域ac配置有多个柱状电极150b中的几个柱状电极150b,而未配置柱状电极150a。

[0075]

据此,在俯视模块基板90的情况下,在区域ac代替剖面积较大的柱状电极150a,而配置有剖面积较小的柱状电极150b。由此,与具有在区域aa~ad的全部区域配置有柱状电极150a的结构的高频模块相比,半导体ic10的配置自由度提高,另外,也能够缩小区域ac。换句话说,由于能够实现半导体ic10的配置自由度、或者由模块基板90的缩小所带来的高频模块1的节省面积化,所以高频模块1的设计自由度提高。另一方面,由于在包围半导体ic10的四个区域aa~ad配置有柱状电极150a或者150b,所以能够充分地确保通过半导体ic10以及各电路元件处理的电信号的取出以及接地强化,进行高频模块1的向外部基板的安装。

[0076]

由此,能够提供提高了设计自由度而不使电气性能以及机械性能劣化的高频模块1、以及具备高频模块1的通信装置5。

[0077]

(实施方式2)

[0078]

在本实施方式中,对内置于半导体ic10的放大电路以及与该放大电路连接的匹配用电路元件的配置结构进行说明。

[0079]

图5a是实施方式2的高频模块1b的剖面结构示意图。此外,对于本实施方式的高频模块1b的平面结构,与图3a相同。具体而言,图5a是图3a的iiib-iiib线上的剖视图。

[0080]

如图5a所示,本实施方式的高频模块1b具有:模块基板90、半导体ic10、多个柱状电极150a及150b、滤波器21及22、电感器31、电路元件51及52、以及树脂部件80a及80b。该图所示的高频模块1b与实施方式1的高频模块1相比,在示有半导体ic10内的元件配置结构的点、以及示有半导体ic10与电感器31的连接结构的点不同。以下,对于本实施方式的高频模块1b,对与实施方式1的高频模块1相同的结构省略说明,以不同的结构为中心进行说明。

[0081]

柱状电极150b的与主面90b平行的剖面积比柱状电极150a的与主面90b平行的剖面积小。在本实施方式中,柱状电极150a以及150b具有圆柱形状,柱状电极150b的与主面90b平行的剖面直径比柱状电极150a的与主面90b平行的剖面直径小。

[0082]

电感器31是配置于主面90a的第一部件。电感器31与半导体ic10经由通孔导体91连接,其中,上述通孔导体91在模块基板90内沿着与主面90a以及90b垂直的方向(z轴方向)

而形成。

[0083]

由此,能够缩短电感器31与半导体ic10的连接布线长度,由于利用低电阻以及寄生电容较小的布线(通孔导体91)连接,所以能够实现高频模块1b的低损耗化以及高性能化。

[0084]

此外,在本实施方式中,经由通孔导体91与半导体ic10连接的第一部件并不限定于电感器31,也可以是安装于主面90a的滤波器21以及22、电路元件51以及52中的任一个。

[0085]

此外,在上述俯视时,也可以最接近边100a~100d中的边100c来配置通孔导体91。

[0086]

由此,通孔导体91配置在不与剖面积较大的柱状电极150a接近的区域,并且,配置在半导体ic10的端部区域且与模块基板90内的布线接近的概率较低的区域。由此,能够降低由通孔导体91和柱状电极150a或者上述布线形成的寄生电容。另外,通过在边100c侧配置通过通孔导体91与半导体ic10连接的电感器31,能够将电感器31配置为在上述俯视时与半导体ic10重叠,所以能够缩短电感器31与半导体ic10的布线,并进行节省面积化。

[0087]

另外,如图5a所示,在本实施方式的高频模块1b中,半导体ic10内置有低噪声放大器41。电感器31与低噪声放大器41经由通孔导体91连接。

[0088]

图5b是比较例1的高频模块500的剖面结构示意图。如该图所示,比较例1的高频模块500具有:模块基板90、半导体ic510、多个柱状电极150a、滤波器21及22、电感器31、电路元件51及52、以及树脂部件80a及80b。比较例1的高频模块500与实施方式2的高频模块1b相比,在半导体ic510内的低噪声放大器541的配置结构不同、以及在模块基板90上的区域ac也配置有柱状电极150a的点不同。以下,对于比较例1的高频模块500,对与实施方式2的高频模块1b相同的结构省略说明,对不同的结构进行说明。

[0089]

半导体ic510内置有低噪声放大器541。电感器31与低噪声放大器541经由通孔导体591以及平面布线图案592连接。

[0090]

另外,在构成半导体ic510的外边缘的四条边中的各边和分别与该四条边对置的模块基板90的各边之间的区域aa、ab、ac、ad中的每一个区域配置有柱状电极150。

[0091]

另外,在上述俯视时,低噪声放大器541由于配置在区域ac的柱状电极150,不接近边100a~100d来配置,而配置在半导体ic510的中央区域。另一方面,最接近边100a~100d中的边100c来配置电感器31,将电感器31配置于模块基板90的端部区域。

[0092]

根据比较例1的高频模块500的上述结构,由于电感器31配置在模块基板90的端部区域,所以可抑制与安装于模块基板90的其它部件以及布线的不必要的磁场耦合或者电解耦合。然而,由于电感器31与低噪声放大器541通过具有高电阻以及较大的寄生电容的布线(通孔导体591以及平面布线图案592)连接,所以高频模块500的传输损耗增大。

[0093]

图5c是比较例2的高频模块500a的剖面结构示意图。比较例2的高频模块500a与比较例1的高频模块500相比,低噪声放大器541以及电感器31的配置结构不同。

[0094]

相对于比较例1的高频模块500,若想要像比较例2的高频模块500a那样,仅通过通孔导体91来连接低噪声放大器541和电感器31,则需要使电感器31向主面90a的中央侧偏移,而在主面90a的外周区域,换句话说在俯视主面90a的情况下与柱状电极150重叠的主面90a上的区域产生死区ds。即使在死区ds配置其它的部件,也存在该部件与电感器31进行不必要的耦合的担忧。

[0095]

根据比较例2的高频模块500a的上述结构,由于死区ds而无法使高频模块500a节

省面积化,另外,由于电感器31与其它部件的不必要的耦合而高频模块500的高频信号传输特性劣化。

[0096]

图5d是比较例3的高频模块500b的剖面结构示意图。比较例3的高频模块500b与比较例2的高频模块500a相比,在主面90a的中央侧还配置有低噪声放大器541以及电感器31。由此,配置于电感器31的周围的其它部件与电感器31产生不必要的耦合的概率进一步提高。

[0097]

根据比较例3的高频模块500b的上述结构,由于电感器31与其它部件的不必要的耦合而高频模块500的高频信号传输特性劣化。

[0098]

与此相对,根据本实施方式的高频模块1b,在上述俯视时,低噪声放大器41以及电感器31的配置被最佳化,最接近边100a~100d中的边100c来配置低噪声放大器41以及电感器31。

[0099]

据此,低噪声放大器41、电感器31、以及通孔导体91配置于不与剖面积较大的柱状电极150a接近的区域,并且,配置于半导体ic10的端部区域且是与模块基板90内的布线接近的概率较低的区域。因此,可抑制电感器31与其它电路元件以及布线的不必要的磁场耦合或者电解耦合。另外,由于电感器31与半导体ic10的连接布线长较短,并且,通过低电阻以及寄生电容较小的布线(通孔导体91)连接,所以能够降低在低噪声放大器41的前段产生的高频噪声。由此,能够实现高频模块1b的低损耗化以及高性能化。

[0100]

此外,虽然作为在上述俯视时,最接近边100c配置的组合,列举了低噪声放大器41以及电感器31,但在半导体ic10内置有功率放大器的情况下,也可以是功率放大器和与该功率放大器的输出端连接的匹配元件的组合。换句话说,作为最接近边100c配置的组合,也可以是放大电路以及与该放大电路连接的匹配元件(第一部件)。

[0101]

(实施方式3)

[0102]

在本实施方式中,对具有从半导体ic10的主面在该主面的垂直方向上延伸的第二连接电极的高频模块的结构进行说明。

[0103]

图6是表示实施方式3的高频模块1c的平面结构以及剖面结构的示意图。在图6的(a)示出从z轴负方向侧观察模块基板90的主面90a以及90b中的主面90b的情况下的电路元件的配置图。另外,图6的(b)是图6的(a)的vi-vi线上的剖视图。此外,由于从z轴正方向侧观察主面90a的情况下的电路元件的配置图与图3a的(a)相同,所以省略图示。

[0104]

如图6所示,本实施方式的高频模块1c具有:模块基板90、半导体ic10、多个柱状电极150a以及多个柱状电极150b、通孔导体151、滤波器21及22、电感器31、电路元件51及52、树脂部件80a及80b。该图所示的高频模块1c与实施方式2的高频模块1b相比,在配置有通孔导体151这一点不同。以下,对于本实施方式的高频模块1c,对与实施方式2的高频模块1b相同的结构省略说明,以不同的结构为中心进行说明。

[0105]

在剖视模块基板90的情况下,柱状电极150a以及150b在主面90b的垂直方向(z轴方向)上从主面90b延伸到比虚拟平面100p(第一虚拟平面)更远离主面90b的虚拟平面100q(第二虚拟平面)。在这里,虚拟平面100q(第二虚拟平面)是包含树脂部件80b的表面的平面。

[0106]

柱状电极150b的与主面90b平行的剖面积比柱状电极150a的与主面90b平行的剖面积小。在本实施方式中,柱状电极150a以及150b具有圆柱形状,柱状电极150b的与主面

90b平行的剖面径比柱状电极150a的与主面90b平行的剖面径小。

[0107]

如图6的(a)所示,在与边100a对置的边190a和边100a之间的模块基板90上的区域aa(第一区域)、与边100b对置的边190b和边100b之间的模块基板90上的区域ab(第二区域)、以及与边100d对置的边190d和边100d之间的模块基板90上的区域ad中的每一个区域配置有柱状电极150a。另一方面,在与边100c对置的边190c和边100c之间的模块基板90上的区域ac(第三区域)配置柱状电极150b,而未配置柱状电极150a。

[0108]

通孔导体151是在上述垂直方向上从半导体ic10的主面10b(第四主面)延伸到树脂部件80b的表面(虚拟平面100q)的第三连接电极。

[0109]

多个通孔导体151中的几个通孔导体151经由通孔电极140与低噪声放大器41连接。另外,多个通孔导体151中的几个通孔导体151经由贯通半导体ic10的通孔电极160与形成于模块基板90的焊盘电极连接。

[0110]

另外,最接近边100a~100d中的边100c来配置低噪声放大器41以及电感器31。

[0111]

根据上述结构,为了填补配置于模块基板90上的区域ac的剖面积较小的柱状电极150b,而配置从半导体ic10的主面10b(顶面)延伸的通孔导体151,从而能够填补电信号的取出、接地强化、以及与外部基板的安装强化,并实现高频模块1c的小面积化。

[0112]

图7是表示实施方式3的变形例的高频模块1d的平面结构以及剖面结构的示意图。在图7的(a)示出从z轴负方向侧观察模块基板90的主面90a以及90b中的主面90b的情况下的半导体ic10以及柱状电极150a以及150b的配置图。另外,图7的(b)是图7的(a)的vii-vii线上的剖视图。此外,从z轴正方向侧观察主面90a的情况下的电路元件的配置图与图3a的(a)相同,所以省略图示。

[0113]

如图7所示,本变形例的高频模块1d具有:模块基板90、半导体ic10、多个柱状电极150a以及多个柱状电极150b、通孔导体152、滤波器21及22、电感器31、电路元件51及52、树脂部件80a及80b、以及屏蔽电极70。该图所示的高频模块1d与实施方式1的高频模块1相比,在示出半导体ic10内的元件配置结构的点、配置有通孔导体152的点、以及配置有屏蔽电极70这一点不同。以下,对于本实施方式的高频模块1d,对与实施方式1的高频模块1相同的结构省略说明,以不同的结构为中心进行说明。

[0114]

在剖视模块基板90的情况下,柱状电极150a以及150b在主面90b的垂直方向(z轴方向)上从主面90b延伸到比虚拟平面100p(第一虚拟平面)更远离主面90b的虚拟平面100q(第二虚拟平面)。在这里,虚拟平面100q(第二虚拟平面)是包含树脂部件80b的表面的平面。

[0115]

柱状电极150b的与主面90b平行的剖面积比柱状电极150a的与主面90b平行的剖面积小。在本变形例中,柱状电极150a以及150b具有圆柱形状,柱状电极150b的与主面90b平行的剖面直径比柱状电极150a的与主面90b平行的剖面直径小。

[0116]

如图7的(a)所示,在与边100a对置的边190a和边100a之间的模块基板90上的区域aa(第一区域)、与边100b对置的边190b和边100b之间的模块基板90上的区域ab(第二区域)、以及与边100d对置的边190d和边100d之间的模块基板90上的区域ad中的每一个区域,配置有柱状电极150a。另一方面,在与边100c对置的边190c和边100c之间的模块基板90上的区域ac(第三区域)配置有柱状电极150b,而未配置柱状电极150a。

[0117]

半导体ic10内置有数字控制电路11。最接近边100a~100d中的边100c来配置数字

控制电路11。

[0118]

通孔导体152是在上述垂直方向上从半导体ic10的主面10b(第四主面)延伸到树脂部件80b的表面(虚拟平面100q)的第三连接电极。

[0119]

多个通孔导体152中的几个通孔导体152经由通孔电极110与数字控制电路11连接。

[0120]

根据上述结构,由于数字控制电路11配置于半导体ic10的端部区域,所以无需在模块基板90内迂回布线,能够抑制经由数字布线的数字噪声(杂波)流入其它电路元件。另外,由于在未配置剖面积较大的柱状电极150a的区域ac的附近配置与数字控制电路11的顶面连接的通孔导体152,所以能够填补数字噪声的除去、电信号的取出、接地强化、以及与外部基板的安装强化,并实现高频模块1d的小面积化。

[0121]

进一步,本实施方式的高频模块1d还具备屏蔽电极70,其中,上述屏蔽电极70形成为覆盖树脂部件80b的至少侧面,并在该侧面与接地电极92g连接。

[0122]

接地电极92g是沿着与模块基板90的主面90a以及90b平行的方向形成的平面布线图案。

[0123]

若数字控制电路11配置于半导体ic10以及模块基板90的端部区域,则存在也向高频模块的外部辐射数字噪声的担忧。

[0124]

与此相对,能够抑制从半导体ic10输出的高频信号,特别是从数字控制电路11发出的数字噪声直接从高频模块1d辐射到外部。另外,能够抑制外来噪声侵入半导体ic10。进一步,由于能够经由屏蔽电极70对半导体ic10的发热进行散热,所以高频模块1d散热性提高。

[0125]

此外,在本变形例的高频模块1d中,也可以不配置屏蔽电极70。另外,也可以在本实施方式的高频模块1c配置屏蔽电极70以及接地电极92g。

[0126]

此外,在本实施方式及其变形例中,通孔导体151以及152既可以是圆柱形状,另外,也可以具有棱柱形状等。另外,通孔导体151以及152也可以是焊球、或者凸块电极等连接电极,在该情况下,也可以在通孔导体151以及152的表面具有球面形状。

[0127]

(其它实施方式等)

[0128]

以上,列举上述实施方式对实施方式1~3的高频模块以及通信装置进行了说明,但本发明的高频模块以及通信装置并不限定于上述实施方式。组合上述实施方式中的任意的构成要素实现的其它实施方式、在不脱离本发明的主旨的范围内对上述实施方式施加本领域技术人员想到的各种变形而得到的变形例、内置有本公开的高频模块以及通信装置的各种设备也包含于本发明。

[0129]

例如,在上述实施方式的高频模块以及通信装置中,也可以在附图所公开的各电路元件以及连接信号路径的路径之间插入其它的电路元件以及布线等。

[0130]

另外,本发明的半导体ic10也可以被实现为作为集成电路的lsi(large scale integration:大规模集成电路)。另外,作为集成电路化的方法,可以利用专用电路或者通用处理器来实现。也可以在制造lsi后,利用能够进行编程的fpga(field programmable gate array:现场可编程门阵列)、能够重建lsi内部的电路单元的连接、设定的可重构处理器。进一步,若根据半导体技术的进步或者派生的其它技术而出现替换lsi的集成电路化的技术,则当然也可以使用该技术来进行功能模块的集成化。

[0131]

本发明能够作为要求小型化的高频模块,广泛地利用于移动电话等通信设备。

[0132]

附图标记说明

[0133]

1、1a、1b、1c、1d、500、500a、500b

…

高频模块,2

…

天线元件,3

…

rf信号处理电路(rfic),4

…

基带信号处理电路(bbic),5

…

通信装置,10、510

…

半导体ic,10a、10b、90a、90b

…

主面,11

…

数字控制电路,12、13、14

…

开关,21、22

…

滤波器,31

…

电感器,41、541

…

低噪声放大器,51、52

…

电路元件,70

…

屏蔽电极,80a、80b

…

树脂部件,90

…

模块基板,91、151、152、591

…

通孔导体,92g

…

接地电极,100a、100b、100c、100d、190a、190b、190c、190d

…

边,100p、100q

…

虚拟平面,101

…

共用端子,102

…

输出端子,110、140、160

…

通孔电极,112、113、114、141

…

控制布线,112s、113s、114s、141s

…

数字控制信号,150a、150b

…

柱状电极,592

…

平面布线图案,aa、ab、ac、ad

…

区域,la、lb、lc、ld

…

距离。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1