接收器的物理层中的集成电路及接收器的物理层的制作方法

[0001]

本申请涉及时钟前送接口(clock forwarding interface),尤其涉及一种位于时钟前送接口接收器(clock forward interface receiver)中具有可在时钟与数据通道之间互换使用的通道的集成电路,以及时钟前送接口接收器的物理层(physical layer)。

背景技术:

[0002]

某些通信系统利用时钟前送方案(clock forwarding scheme)以在传输器与接收器之间提供高速数据传输。于此时钟前送方案中,一时钟信号连同一个或多个数据信号从一传输器传送到一接收器。举例来说,所述接收器可包括一时钟前送接口,其具有一时钟通道(clock lane)和多条数据通道(data lane)。所述时钟通道上的一时钟信号连同所述多条数据通道上的多个数据信号会从所述传输器向前传送(forward)到所述接收器。因此,所述接收器可利用所述传输器所向前传送的所述时钟信号来捕获所述多个数据信号。视所使用的物理层(physical layer,phy)规格而定,所述时钟前送接口中各通道(即,时钟通道或数据通道)可以是用于时钟或数据传输的点到点(point-to-point)、双线(two-wire)或三线(three-wire)接口。

技术实现要素:

[0003]

本申请的实施例公开了一种位于时钟前送接口接收器中具有可在时钟与数据通道之间互换使用的通道的集成电路,及其相关的物理层。

[0004]

本申请的某些实施例公开了一种一接收器的一物理层的集成电路。所述集成电路包括一多通道接口、一通道选取电路以及n个采样电路。n是大于1的整数。所述多通道接口具有n条通道。所述通道选取电路耦接于所述多通道接口,用以将所述n条通道中的m条通道选为m条时钟通道,并输出分别在所述m条时钟通道上的m个信号。m是小于n的正整数。剩余的(n-m)条通道作为(n-m)条数据通道。所述n个采样电路耦接于所述多通道接口及所述通道选取电路。所述n个采样电路中的(n-m)个采样电路分别耦接于所述(n-m)条数据通道。所述(n-m)个采样电路中的各采样电路用以根据所述m条时钟通道上的所述m个信号其中的一个,对所述(n-m)条数据通道中的一数据通道上的信号进行采样。

[0005]

本申请的某些实施例公开了一种一接收器的一物理层的集成电路。所述集成电路包括一多通道接口、n个采样电路以及一通道选取电路。n是大于1的整数。所述多通道接口具有n条通道。所述n个采样电路耦接于所述多通道接口。所述n个采样电路中的各采样电路均具有一时钟输入端与一数据输入端。所述通道选取电路用以通过将所述n条通道中的m条通道耦接于所述n个采样电路的n个时钟输入端,来将所述m条通道选为m条时钟通道。m是小于n的正整数。剩余的(n-m)条通道作为(n-m)条数据通道。于一模式中,所述n条通道中的一通道被选为耦接于所述n个时钟输入端中的一个或多个时钟输入端的一时钟通道。于另一模式中,所述n条通道中被选取的所述通道作为耦接于所述n个采样电路的n个数据输入端其中的一个而未耦接于所述n个时钟输入端的一数据通道。

[0006]

本申请的某些实施例公开了一种一接收器的物理层。所述物理层包括一物理介质连接层(physical medium attachment layer,pma)以及一物理编码子层(physical coding sublayer,pcs)。所述物理介质连接层用以输出分别与m个不同时钟域相关的m个时钟信号。m是大于1的整数。所述物理编码子层具有n条通道,并耦接于所述物理介质连接层。n是大于m的整数。所述物理编码子层用以将所述n条通道中的m条通道选为m条时钟通道,并通过所述m条时钟通道接收所述m个时钟信号。所述n条通道中剩余的(n-m)条通道中的一条或多条通道作为一条或多条数据通道。

[0007]

通过可在时钟通道与数据通道之间互换使用的至少一通道,接收侧的物理层可支持传输侧的不同的通道配置(lane configuration)。例如,物理层可分为多个物理接口以支持(support)多个传输器。此外,可根据一时钟/数据通道的通道标识符来选择所述时钟/数据通道,以方便时钟/数据通道的选取。

附图说明

[0008]

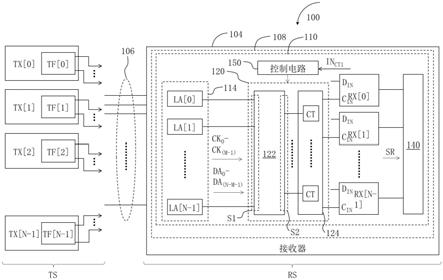

图1是根据本申请某些实施例的例示性多通道通信系统的功能方框示意图。

[0009]

图2a至图2c是根据本申请某些实施例的图1所示的接收器的不同模式的示意图。。

[0010]

图3是根据本申请某些实施例的图1所示的集成电路的具体实施方式的示意图。

[0011]

图4a至图4c是根据本申请某些实施例的图3所示的集成电路的操作示意图。

[0012]

图5a至图5c是根据本申请某些实施例的图1所示的集成电路的其他具体实施方式的示意图。

[0013]

图6是根据本申请某些实施例的图1所示的集成电路的另一具体实施方式的示意图。

[0014]

图7是根据本申请某些实施例的图1所示的集成电路的另一具体实施方式的示意图。

[0015]

图8是根据本申请某些实施例的图1所示的集成电路的另一具体实施方式的示意图。

[0016]

图9是根据本申请某些实施例的图7所示的状态机的操作的示意图。

[0017]

图10是根据本申请某些实施例的用于图7所示的多条通道的通道标识符的具体实施方式的示意图。

[0018]

图11是根据本申请某些实施例的例示性接收器的功能方框示意图。

[0019]

图12是根据本申请某些实施例的图11所示的物理编码子层中的集成电路的实施例的示意图。

[0020]

图13是根据本申请某些实施例的图11所示的物理编码子层中的集成电路的另一实施例的示意图。

[0021]

图14是根据本申请某些实施例的例示性多通道通信系统的功能方框示意图。

具体实施方式

[0022]

以下披露内容公开了多种实施方式或例示,其能用以实现本申请内容的不同特征。下文所述的参数值、组件与配置的具体例子用以简化本申请内容。当可想见,这些叙述仅为例示,其本意并非用于限制本申请内容。此外,本申请内容可能会在多个实施例中重复

使用组件符号和/或标号。此种重复使用乃是基于简洁与清楚的目的,且其本身不代表所讨论的不同实施例和/或组态之间的关系。

[0023]

再者,当可理解,若将一部件描述为与另一部件“连接(connected to)”或“耦接(coupled to)”,则两者可直接连接或耦接,或两者间可能出现其他中间(intervening)部件。

[0024]

采用时钟前送接口的接收器的物理层可使用专用的时钟通道(dedicated clock lane)来接收通过传输侧(transmitter side)的时钟通道所传送的时钟信号。然而,在传输器的时钟通道与多条数据通道彼此互换使用以满足某些通信要求的应用中,此接收器将不再适用。例如,位于传输侧的传输装置的个数可能会改变。又例如,位于传输侧的传输装置可能会在某些操作情境中,将时钟通道与数据通道互换使用。

[0025]

本申请公开了位于一时钟前送接口接收器中具有可在时钟与数据通道之间互换使用(interchangeable)的通道的一例示性集成电路。在某些实施例中,所述例示性集成电路可实施于所述时钟前送接口接收器的物理层的子层(sublayer)中,诸如物理介质连接层(physical medium attachment layer,pma)或物理编码子层(physical coding sublayer,pcs)。通过所述例示性集成电路,所述时钟前送接口接收器可适应于时钟通道与数据通道之间的互换使用,从而支持传输侧的不同的通道配置(lane arrangement)。

[0026]

图1是根据本申请某些实施例的一例示性多通道通信系统(multi-lane communication system)的功能方框示意图。多通道通信系统100包括位于一传输侧ts的k个传输器tx[0]-tx[k-1]以及位于一接收侧(receiver side)rs的一接收器104,其中k是正整数。k个传输器tx[0]-tx[k-1]中的各传输器可包括一多通道接口(即,k个多通道接口tf[0]-tf[k-1]其中的一个)以传输时钟信息和数据信息。k个多通道接口tf[0]-tf[k-1]中的各多通道接口可包括至少一时钟通道和至少一数据通道(图1未示)。

[0027]

接收器104用以通过一通信链路(communication link)106和k个传输器tx[0]-tx[k-1]中的各传输器进行通信。接收器104的一物理层108可采用时钟前送方案来接收通信链路106上所传送的时钟信息和数据信息。因此,至少一时钟信号可连同至少一数据信号从传输侧ts向前传送到接收侧rs。物理层108包括一集成电路110,其可设置于物理层108的物理介质连接层或物理编码子层。集成电路110可适应于传输侧ts的多种通道配置(lane arrangements/configurations)。举例来说,集成电路110可操作在一模式以与传输侧ts进行通信,其中传输侧ts将单一通道作为一时钟通道以传输一时钟信号。集成电路110可操作在另一模式以与传输侧ts进行通信,其中传输侧ts将多条通道作为多条时钟通道以传输多个时钟信号。

[0028]

于此实施例中,集成电路110包括(但不限于)一多通道接口(multi-lane interface)114、一通道选取电路(lane selection circuit)120以及n个采样电路rx[0]-rx[n-1],其中n是大于1的整数。多通道接口114通过通信链路106连接于k个多通道接口tf[0]-tf[k-1]中的各通道接口。多通道接口114包括n条通道la[0]-la[n-1]。n条通道la[0]-la[n-1]中的至少一通道可通用于(interchangeable between)时钟通道与数据通道,也就是说,所述至少一通道可在时钟通道与数据通道之间互换使用。

[0029]

通道选取电路120耦接于多通道接口114,用以将n条通道la[0]-la[n-1]中的m条通道选为m条时钟通道,其中m是小于n的正整数。此外,通道选取电路120可用于输出分别在

所述m条时钟通道上的m个信号ck

0-ck

(m-1)

(即,m个时钟信号)。剩余的(n-m)条通道可分别作为(n-m)条数据通道。所述(n-m)条数据通道中的至少一数据通道可携带从传输侧ts所传送的数据信号。于此实施例中,所述m个时钟信号可连同(n-m)个数据信号(即,所述(n-m)条通道上的(n-m)个信号da

0-da

(n-m-1)

)向前传送,使各数据通道可携带一数据信号。值得注意的是,通道选取电路120可将n条通道la[0]-la[n-1]中的任一通道选为时钟通道。n条通道la[0]-la[n-1]中的各通道均可通用于时钟通道与数据通道。

[0030]

于此实施例中,通道选取电路120包括(但不限于)多个选取级(selection stage)122与124。选取级122具有一输入侧s1与一输出侧s2。输入侧s1耦接于多通道接口114。选取级122用以将所述m条时钟通道上的m个信号ck

0-ck

(m-1)

从输入侧s1耦接于输出侧s2。选取级124设置于输出侧s2与n个采样电路rx[0]-rx[n-1]之间,用以将m个信号ck

0-ck

(m-1)

中的各信号耦接于n个采样电路rx[0]-rx[n-1]中的一个或多个采样电路。举例来说,选取级122可实施为n对m多工器(n-to-m multiplexer),其可将n条通道la[0]-la[n-1]中的m条通道耦接于输出侧s2。选取级124可实施为m个时钟树(clock tree)ct,其中各时钟树均可将一时钟信号(即,m个信号ck

0-ck

(m-1)

其中的一个)分配给不止一个采样电路。

[0031]

n个采样电路rx[0]-rx[n-1]耦接于多通道接口114及通道选取电路120,用以根据从传输侧ts所传送的时钟信息与数据信息来进行数据采样。于此实施例中,n个采样电路rx[0]-rx[n-1]中的各采样电路用以接收所述m条时钟通道上的m个信号ck

0-ck

(m-1)

其中的一个。此外,n个采样电路rx[0]-rx[n-1]中的(n-m)个采样电路分别耦接于所述(n-m)条数据通道,用以接收所述(n-m)条数据通道上的(n-m)个信号da

0-da

(n-m-1)

。所述(n-m)个采样电路中的各采样电路用以根据m个信号ck

0-ck

(m-1)

其中的一个,对(n-m)个信号da

0-da

(n-m-1)

其中的一个进行采样。

[0032]

举例来说(但本申请不限于此),n个采样电路rx[0]-rx[n-1]中的各采样电路可包括一时钟输入端c

in

及一数据输入端d

in

。各采样电路利用输入到相应的时钟输入端c

in

的信号来对输入到相应的数据输入端d

in

的信号进行采样。通过将n条通道la[0]-la[n-1]中的m条通道耦接于n个采样电路rx[0]-rx[n-1]的n个时钟输入端c

in

,通道选取电路120可将n条通道la[0]-la[n-1]中的所述m条通道选为所述m条时钟通道。剩余的(n-m)条通道中的各通道可耦接于一数据输入端d

in

而未耦接于所述n个时钟输入端c

in

,从而作为一数据通道。因此,当各采样电路通过其包括的数据输入端d

in

耦接于一数据通道,以及通过其包括的时钟输入端c

in

耦接于一时钟通道时,所述采样电路可利用所述时钟通道上的信号来对所述数据通道上的信号进行采样。在某些实施例中,一时钟通道可耦接于所述n个时钟输入端c

in

中的一个或多个时钟输入端,使多个采样电路可根据相同的时钟信号进行数据采样。

[0033]

n个采样电路rx[0]-rx[n-1]所输出的采样结果sr包括时钟信息与数据信息,其可传送到集成电路110中包括其他功能方框(图1未示)的输出电路140以进行进一步的处理。举例来说,同时耦接于m个信号ck

0-ck

(m-1)

其中的一个信号与(n-m)个信号da

0-da

(n-m-1)

其中的一个信号的一采样电路可输出一数据信号,所述数据信号可作为采样结果sr的一部分。耦接于m个信号ck

0-ck

(m-1)

其中的一个信号而未耦接于(n-m)个信号da

0-da

(n-m-1)

的一采样电路可输出一时钟信号,所述时钟信号可作为采样结果sr的另一部分。输出电路140可根据采样结果sr输出m个时钟信号与(n-m)个数据信号。在某些实施例中,输出电路140可包括一反序列化块(deserializer block)。从输出电路140所输出的所述m个时钟信号和所述(n-m)

个数据信号中的各信号均可为多位并行输出信号(multi-bit parallel output signal)。

[0034]

在某些实施例中,传输器可提供信息以指示出哪一条通道应该作为一时钟通道。根据传输器所提供的信息,接收器104可对通道选取电路120进行配置/设定(configure),以将适当的通道选为所述时钟通道。接收器104可正确地使用所述时钟通道上的信号,以对一条或多条数据通道上的信号进行处理。

[0035]

在某些实施例中,传输器可通过重复一特定位模式(bit pattern)来产生一时钟信号,从而指示出传输侧rs上哪一条通道应该作为一时钟通道。举例来说,传输器可重复地发送一位模式“01”,诸如“01010101”,以作为一时钟信号。接收器104可通过检查一通道所接收的比特流(bit stream)中是否具有一重复位模式,辨识出哪一条通道可作为所述时钟通道。也就是说,接收器104可根据一预定重复位模式的侦测结果来对通道选取电路120进行配置/设定。

[0036]

在某些实施例中,与接收器104相关的系统应用程序(system application)(图1未示)可决定多通道接口104中的哪一条通道应该作为一时钟通道。根据系统应用程序所发送的指令,接收器104可对通道选取电路120进行配置/设定,以将适当的通道选为所述时钟通道。

[0037]

请注意,以上所述仅供说明的目的,并非用来限制本申请的范围。在某些实施例中,图1所示的通道选取电路120可由单一选取级或不止两个选取级来实施,而不致背离本申请的范围。在某些实施例中,图1所示的n个采样电路rx[0]-rx[n-1]中的至少一个采样电路可利用具有不止一个数据输出端的采样电路来实施。

[0038]

通过可在时钟通道与数据通道之间互换使用的至少一通道,接收侧rs的物理层108可支持传输侧ts的不同的通道配置。为了进一步说明接收侧rs的通道互换方案(lane interchange scheme),以下提供了传输侧ts的通道配置的某些实施例。本领域的技术人员应可了解接收侧rs的通道互换方案可支持传输侧ts的其他通道配置,而不致背离本申请的范围。

[0039]

图2a至图2c是根据本申请某些实施例的图1所示的接收器104的不同模式的示意图。接收器104可根据传输侧ts的不同通道配置分别操作在不同模式op1-op3。于图2a所示的模式op1中,接收器104可用来接收单一传输器所提供的时钟信息与数据信息。为方便说明,所述单一传输器可由图1所示的传输器tx[0]来代表。传输器tx[0]的多通道接口tf[0]包括多条通道l0[0]-l0[p],p为正整数。传输器tx[0]用以将通道l0[p]上的时钟信号c0连同p条通道l0[0]-l0[p-1]上的p个数据信号d0

0-d0

(p-1)

一并输出。

[0040]

接收器104用以将n条通道la[0]-la[n-1]其中的一条通道选为一时钟通道(即,m=1),以通过通信链路106接收时钟信号c0。剩余的(n-1)条通道中的p条通道可作为p条数据通道以接收p个数据信号d0

0-d0

(p-1)

。于此实施例中,从传输器tx[0]所传送的数据信号的个数以及时钟信号的个数两者的总和可等于多通道接口114的通道个数(即,p+1=n)。因此,n条通道la[0]-la[n-1]中的各通道可用来接收传输侧tx[0]所提供的信号信息。接收器104可将通道la[n-1](即,通道l0[p]上的时钟信号c0输入的通道)选为所述时钟通道。剩余的(n-1)条通道la[0]-la[n-2]可作为(n-1)条数据通道以接收p个数据信号d0

0-d0

(p-1)

。

[0041]

于图2b所示的模式op2中,接收器104可用来接收多个传输器所提供的时钟信息与数据信息,其中传输侧ts的多条通道可作为多条时钟通道以携带多个时钟信号。例如,当操

作在分岔模式(bifurcation mode)时,物理层108可分成彼此不同的多个物理层以支持图1所示的k个传输器tx[0]-tx[k-1]中的多个传输器。为方便说明,于此实施例中,所述多个传输器可由两个传输器tx[1]与tx[2]来代表。传输器tx[1]的多通道接口tf[1]包括多条通道l1[0]-l0[q],q为正整数。传输器tx[1]用以将通道l1[q]上的时钟信号c1连同q条通道l1[0]-l1[q-1]上的q个数据信号d1

0-d1

(q-1)

一并输出。传输器tx[2]的多通道接口tf[2]包括多条通道l2[0]-l2[r],r为正整数。传输器tx[2]用以将通道l2[r]上的时钟信号c2连同r条通道l2[0]-l2[r-1]上的r个数据信号d2

0-d2

(r-1)

一并输出。由于传输侧ts的两条通道于模式op2中均作为时钟通道,因此,传输侧ts于模式op2中的通道配置不同于传输侧ts于模式op1中的通道配置(其采用单一通道作为时钟通道)。

[0042]

回应模式op2,接收器104可将n条通道la[0]-la[n-1]中的两条通道选为两条时钟通道(即,m=2),以接收传输侧ts所传送的多个时钟信号c1与c2。剩余的(n-2)条通道中的(q+r)条通道可作为(q+r)条数据通道,以接收多个数据信号d1

0-d1

(q-1)

与d2

0-d2

(r-1)

。于此实施例中,从多个传输器tx[1]与tx[2]所传送的数据信号的个数以及时钟信号的个数两者的总和,可等于多通道接口114的通道个数(即,q+r+2=n)。因此,n条通道la[0]-la[n-1]中的各通道可用来接收多个传输器tx[1]与tx[2]所提供的信号信息。接收器104可将两条通道la[j]与la[n-1](即,多个时钟信号c1与c2输入的通道)选为两条时钟通道。j为介于0与n-2之间的整数。剩余的(n-2)条通道可作为(n-2)条数据通道以接收多个数据信号d1

0-d1

(q-1)

与d2

0-d2

(r-1)

。由于通道la[j]可在模式op1中作为数据通道,而在模式op2中作为时钟通道,因此,集成电路110不仅可支持单个传输器,也可支持多个传输器。

[0043]

在某些实施例中,一个或多个传输器具有可在数据通道与时钟通道之间互换使用的通道,以于传输侧ts提供不同的通道配置。举例来说,于图2c所示的模式op3中,接收器104可用来接收传输器tx[0]所提供的时钟信息与数据信息,其中传输器tx[0]可从通道l0[0]传送时钟信号c0,以及从p条通道l0[1]-l0[p]传输p个数据信号d0

0-d0

(p-1)

。相较于模式op1,传输器tx[0]可致使于时钟通道上以及于数据通道上传输的信号彼此互换。因此,在模式op1中作为数据通道的通道l0[0]可在模式op3中作为时钟通道,而在模式op1中作为时钟通道的通道l0[p]可在模式op3中作为数据通道。接收器140可将通道la[0]选为时钟通道以接收时钟信号c0。剩余的(n-1)条通道la[1]-la[n-1]中的p条通道可作为p条数据通道以接收p个数据信号d0

0-d0

(p-1)

。通过将通道la[0]与通道la[n-1]分别在数据通道与时钟通道之间互换使用,集成电路110可支持能够将时钟通道与数据通道互换使用的传输器tx[0]。

[0044]

为便于理解本申请的内容,以下提供一些实施例以进一步说明采用通道互换方案的时钟前送接口接收器。本领域的技术人员应可了解,其他基于图1所示的集成电路110或接收器104所描述的通道互换方案的实施例均遵循本申请的精神而落入本申请的保护范围。

[0045]

图3是根据本申请某些实施例的图1所示的集成电路110的具体实施方式的示意图。集成电路310设置于接收器300的物理层中,诸如物理介质连接层,以接收传输侧的一个或多个传输器所传送的时钟信息与数据信息。集成电路310可作为图1所示的集成电路110(其包括六条可通用于时钟通道与数据通道的通道,n=6)的实施例。于此实施例中,集成电路310可包括图1所示的多个采样电路rx[0]-rx[5]、一多通道接口314以及一通道选取电路320。多通道接口314以及通道选取电路320可分别作为图1所示的多通道接口114以及通道

选取电路120的实施例。

[0046]

于此实施例中,多通道接口314的多条通道la[0]-la[5]中的各通道均可利用双线通道(two-wire lane)来实施。双线通道是包括一对信号引脚(apair of signal pins)及一放大器的差分通道(differential lane)。在某些实施例中,多条通道la[0]-la[5]中的各通道均可利用其他类型的通道来实施,诸如单线通道或具有超过两线的通道,而不致背离本申请的范围。

[0047]

通道选取电路320用以将多条通道la[0]-la[5]中的一条或多条通道选为一条或多条时钟通道。通道选取电路320可包括多个选取级322和324,其可分别作为图1所示的多个选取级122和124的实施例。于此实施例中,选取级322可将一条或两条通道耦接于选取级324,以回应集成电路310的模式。选取级322包括(但不限于)多个通道选取单元322.0和322.1。通道选取单元322.0用以根据一时钟选取信号sel

00

将多条通道la[0]-la[2]从输入侧s01耦接于输出侧s02。通道选取单元322.1用以根据一时钟选取信号sel

01

将多条通道la[3]-la[5]从输入侧s11耦接于输出侧s12。

[0048]

选取级324可将选取级322所选取的各通道上的信号分配给不止一个采样电路。选取级324包括(但不限于)多个通道选取单元324.0-324.5。多个通道选取单元324.0-324.5均可根据相应的时钟选取信号(即,多个时钟选取信号sel

10-sel

15

其中的一个)多个输出侧s02和s12耦接于相应的采样电路。关于多个时钟选取信号sel

00

、sel

01

与sel

10-sel

15

的说明请容后再叙。

[0049]

多个采样电路rx[0]-rx[5]各自的时钟输入端c

in

分别耦接于多个通道选取单元324.0-324.5各自的输出端。多个采样电路rx[0]-rx[5]各自的数据输入端d

in

分别耦接于多条通道la[0]-la[5]。于此实施例中,多个采样电路rx[0]-rx[5]中的各采样电路均可利用触发器(flip-flop)(诸如d型触发器(d-type flip-flop))来实施,以进行数据采样。本领域的技术人员应可了解多个采样电路rx[0]-rx[5]的各采样电路均可利用其他类型的采样电路来实施,而不致背离本申请的范围。

[0050]

图4a至图4c是根据本申请某些实施例的图3所示的集成电路310的操作示意图。于图4a与图4b所示的实施例中,集成电路310操作在与图2a/2c所示的模式op1/op3相似的模式中,以接收来自多通道接口314的单个时钟信号。通道选取电路320可将多条通道la[0]-la[5]其中的一条通道选为一时钟通道,以接收所述时钟信号。通道选取电路320用以将所述时钟通道上的信号(即,时钟信号)耦接于多个采样电路rx[0]-rx[5]中的各采样电路。于图4c所示的实施例中,集成电路310操作在与图2b所示的模式op2相似的模式中,以接收来自多通道接口314的多个时钟信号。通道选取电路320可将多条通道la[0]-la[5]中的两条通道选为两条时钟通道,以接收所述多个时钟信号。通道选取电路320用以将各时钟通道上的信号耦接于多个采样电路rx[0]-rx[5]中的一个或多个采样电路。

[0051]

首先请参阅图4a,集成电路310可支持“5d1c”通道配置,其中一时钟信号5d_clk输入到多条通道la[0]-la[2]其中的一条通道(于此实施例中,以输入至通道la[0]为例来说明)。五个数据信号5d

0-5d4输入到剩余的五条通道。通道选取单元322.0根据时钟选取信号sel

00

将通道la[0]耦接于输出侧s02,以将通道la[0]选为时钟通道。多条通道la[1]和la[2]未耦接于输出侧s02。此外,多个通道选取单元324.0-324.5中的各通道选取单元可根据相应的时钟选取信号,将通道选取单元322.0的输出侧s02耦接于相应的采样电路。因此,时钟

信号5d_clk可传送到多个采样电路rx[0]-rx[5]各自的时钟输入端c

in

。分别耦接于多条通道la[1]-la[5]的多个采样电路rx[1]-rx[5]可根据时钟信号5d_clk对多个数据信号5d

0-5d4进行采样。

[0052]

请参阅图4b,集成电路310可支持“5d1c”通道配置,其中时钟信号5d_clk输入到多条通道la[3]-la[5]其中的一条通道(于此实施例中,以输入至通道la[3]为例来说明)。多个数据信号5d

0-5d4输入到剩余的五条通道。通道选取单元322.1根据时钟选取信号sel

01

将通道la[3]耦接于输出侧s12,以将通道la[3]选为时钟通道。多个通道选取单元324.0-324.5中的各通道选取单元可将通道选取单元322.1的输出侧s12耦接于相应的采样电路。因此,分别耦接于多条通道la[0]-la[2]、la[4]和la[5]的多个采样电路rx[0]-rx[2]、rx[4]和rx[5]可根据时钟信号5d_clk对多个数据信号5d

0-5d4进行采样。

[0053]

请参阅图4c,集成电路310可作为两个电路接口,其均可支持“2d1c”通道配置(两条通道作为数据通道,一条通道作为时钟通道)。于此实施例中,一时钟信号2d_clk0输入到多条通道la[0]-la[2]其中的一条通道,诸如通道la[0]。相关的数据信号2d

00

与2d

01

可输入到剩余的两条通道。此外,一时钟信号2d_clk1输入到多条通道la[3]-la[5]其中的一条通道,诸如通道la[3]。相关的数据信号2d

10

与2d

11

可输入到剩余的两条通道。

[0054]

通道选取单元322.0用以根据时钟选取信号sel

00

将通道la[0]耦接于输出侧s02。多个通道选取单元324.0-324.2中的各通道选取单元用以根据相应的时钟选取信号将输出侧s02耦接于相应的采样电路。因此,分别耦接于多条通道la[1]和la[2]的多个采样电路rx[1]和rx[2]可根据时钟信号2d_clk0对多个数据信号2d

00

和2d

01

进行采样。相似地,通道选取单元322.1用以根据时钟选取信号sel

01

将通道la[3]耦接于输出侧s12。多个通道选取单元324.3-324.5中的各通道选取单元用以根据相应的时钟选取信号将输出侧s12耦接于相应的采样电路。因此,分别耦接于多条通道la[4]与la[5]的多个采样电路rx[4]和rx[5]可根据时钟信号2d_clk1对多个数据信号2d

10

和2d

11

进行采样。由于多个时钟选取信号sel

10-sel

12

中的各时钟选取信号的信号电平/信号值,均可不同于多个时钟选取信号sel

13-sel

15

中的各时钟选取信号的信号电平/信号值,因此,多个通道选取单元324.0-324.5可将不同的时钟信号2d_clk0与2d_clk1分配给多个采样电路rx[0]-rx[5]。

[0055]

通过参照图4a与图4b所描述的选取操作,图3所示的选取级322及选取级324可分别作为一6对1多工器(6-to-1multiplexer)及一时钟树,以支持“5d1c”通道配置。此外,通过参照图4c所描述的选取操作,图3所示的选取级322可作为两个3对1多工器(3-to-1multiplexer),以及图3所示的选取级324可作为两个时钟树,从而支持分岔模式中的“2d1c”通道配置。因此,图3所示的通道选取电路320可通过操作为6对m多工器(6-to-mmultiplexer)及m个时钟树,来支持一个或多个传输器,其中m可等于1或2(取决于集成电路310的模式)。

[0056]

请注意,图3所示的多个选取级322与324的电路结构只是用于方便说明的目的,并非用来限制本申请的范围。在某些实施例中,选取级322可由其他电路结构来实施以提供多工器的操作。在某些实施例中,选取级324可由其他电路结构来实施以建构一个或多个时钟树。在某些实施例中,各选取的时钟通道上的信号(诸如时钟信号)可未耦接于各采样电路的数据输入端d

in

。举例来说,当图3所示的通道la[0]被选取为时钟通道时,通道la[0]可未耦接于各采样电路的数据输入端d

in

。

[0057]

在某些实施例中,多个时钟选取信号sel

10-sel

12

可利用相同的时钟选取信号来实施,或者可具有相同的信号值。在某些实施例中,多个时钟选取信号sel

13-sel

15

可利用相同的时钟选取信号来实施,或者可具有相同的信号值。这些设计修改与变化均遵循本申请的精神而落入本申请的保护范围。

[0058]

图5a至图5c是本申请某些实施例的图1所示的集成电路110的其他具体实施方式的示意图。图5a至图5c所示的多个集成电路510a-510c中的各集成电路均可作为图1所示的集成电路110(其包括六条可通用于时钟通道与数据通道的通道,n=6)的实施例。在这些实施例中,图1所示的通道选取电路120可利用不同的时钟树群组(clock tree group)来实施,以支持传输侧的不同的通道配置。各时钟树群组包括至少一时钟树电路,以及一时钟树电路包括一多工器与一时钟树。

[0059]

首先请参阅图5a。除了通道选取电路520a之外,集成电路510a的结构与图3所示的集成电路310的结构相似/相同。通道选取电路520a所提供的电路操作,可以与参照图4a/4b所描述的通道选取电路320的电路操作相似/相同。于此实施例中,通道选取电路520a可利用一时钟树群组g1来实施。时钟树群组g1具有一时钟树电路,其包括一多工器522a(即,6对1多工器)以及一时钟树524a。多工器522a可根据一时钟选取信号sel

a

将多条通道la[0]-la[5]其中的一条通道选为时钟通道,从而从一输出端t

5d

输出所选取的通道上的信号。时钟树524a可将输出端t

5d

上的信号分配给多个采样电路rx[0]-rx[5]中的各采样电路。请注意,图4a/4b所示的选取级322的电路结构可作为多工器522a的实施方式。此外,或替代地,图4a/4b所示的选取级324的电路结构可作为时钟树524a的实施方式。由于本领域的技术人员在阅读图3、图4a与图4b相关的段落说明之后,应可了解图5a所示的通道选取电路520a于“5d1c”通道配置的操作细节,因此,关于通道选取的进一步说明在此便不再赘述。

[0060]

请参阅图5b。除了通道选取电路520b之外,集成电路510b的结构与图3所示的集成电路310的结构相似/相同。通道选取电路520b所提供的电路操作,可以与参照图4c所描述的通道选取电路320的电路操作相似/相同。于此实施例中,通道选取电路520b可利用一时钟树群组g2来实施。时钟树群组g2具有两个时钟树电路,其中一时钟树电路包括一多工器522b.0及一时钟树524b.0,另一时钟树电路包括一多工器522b.1及一时钟树524b.1。多工器522b.0(即,3对1多工器)可根据一时钟选取信号sel

b0

将多条通道la[0]-la[2]其中的一条通道选为时钟通道。时钟树524b.0可将输出端t

2d0

上的信号分配给多个采样电路rx[0]-rx[2]中的各采样电路。多工器522b.1(即,3对1多工器)可根据一时钟选取信号sel

b1

将多条通道la[3]-la[5]其中的一条通道选为时钟通道。时钟树524b.1可将输出端t

2d1

上的信号分配给多个采样电路rx[3]-rx[5]中的各采样电路。请注意,图4c所示的选取级322的电路结构可作为多个多工器522b.0和522b.1的实施方式。此外,或替代地,图4c所示的选取级324的电路结构可作为多个时钟树524b.0和524b.1的实施方式。由于本领域的技术人员在阅读图3与图4c相关的段落说明之后,应可了解图5b所示的通道选取电路520b于“2d1c”通道配置的操作细节,因此,关于通道选取的进一步说明在此便不再赘述。

[0061]

请参阅图5c。除了通道选取电路520c之外,集成电路510c的结构与图3所示的集成电路310的结构相似/相同。通道选取电路520c可利用一时钟树群组g3来实施。时钟树群组g3具有三个时钟树电路,从而可支持设置了三条时钟通道及其相关的三条数据通道的传输侧。于此实施例中,通道选取电路520c包括多个多工器522c.0-522c.2(即,多个2对1多工

器)以及多个时钟树524c.0-524c.2。多工器522c.0可根据一时钟选取信号sel

c0

将多条通道la[0]和la[1]其中的一条通道选为时钟通道。多工器522c.1可根据一时钟选取信号sel

c1

将多条通道la[2]和la[3]其中的一条通道选为时钟通道。多工器522c.2可根据一时钟选取信号sel

c2

将多条通道la[4]和la[5]其中的一条通道选为时钟通道。时钟树524c.0可将输出端t

1d0

上的信号分配给多个采样电路rx[0]与rx[1]中的各采样电路。时钟树524c.1可将输出端t

1d1

上的信号分配给多个采样电路rx[2]和rx[3]中的各采样电路。时钟树524c.2可将输出端t

1d2

上的信号分配给多个采样电路rx[4]和rx[5]中的各采样电路。

[0062]

举例来说,多个多工器522c.0-522c.2可将多条通道la[0]、la[2]和la[4]选为多条时钟通道。因此,采样电路rx[1]可根据通道la[0]上的信号对通道la[1]上的信号进行采样。采样电路rx[3]可根据通道la[2]上的信号对通道la[3]上的信号进行采样。采样电路rx[5]可根据通道la[4]上的信号对通道la[5]上的信号进行采样。集成电路510c可分成三个接口,各接口均可支持“1d1c”通道配置(一通道可作为时钟通道,另一通道可作为数据通道)。

[0063]

图6是本申请某些实施例的图1所示的集成电路110的另一具体实施方式的示意图。集成电路610可作为图1所示的集成电路110(其包括六条可通用于时钟通道与数据通道的通道,n=6)的实施例。于此实施例中,集成电路610可采用图5a至图5c所示的多个时钟树群组g1-g3,以支持不同的通道配置。集成电路610包括一通道选取电路620以及图3所示的多通道接口314和多个采样电路rx[0]-rx[5]。通道选取电路620可作为图1所示的通道选取电路120的实施例,并可包括多个选取级622与624。

[0064]

选取级622可包括图5a所示的时钟树群组g1的多工器522a、图5b所示的时钟树群组g2的多个多工器522b.0与522b.1,以及图5c所示的时钟树群组g3的多个多工器522c.0-522c.2。选取级624可包括多个多工器624.0-624.5。多工器624.0用以将多个输出端t

5d

、t

2d0

和t

1d0

其中的一个输出端耦接于采样电路rx[0]的时钟输入端c

in

。多工器624.1用以将多个输出端t

5d

、t

2d0

和t

1d0

其中的一个输出端耦接于采样电路rx[1]的时钟输入端c

in

。多工器624.2用以将多个输出端t

5d

、t

2d0

和t

1d1

其中的一个输出端耦接于采样电路rx[2]的时钟输入端c

in

。多工器624.3用以将多个输出端t

5d

、t

2d1

和t

1d1

其中的一个输出端耦接于采样电路rx[3]的时钟输入端c

in

。多工器624.4用以将多个输出端t

5d

、t

2d1

和t

1d2

其中的一个输出端耦接于采样电路rx[4]的时钟输入端c

in

。多工器624.5用以将多个输出端t

5d

、t

2d1

和t

1d2

其中的一个输出端耦接于采样电路rx[5]的时钟输入端c

in

。

[0065]

在集成电路610用于支持“5d1c”通道配置的模式中,多个多工器624.0-624.5中的各多工器用以将输出端t

5d

耦接于相应的采样电路,使输出端t

5d

上的时钟信号5d_clk可分配给各采样电路。举例来说,多工器522a可根据时钟选取信号sel

a

将通道la[0]耦接于输出端t

5d

。剩余的多条通道la[1]-la[5]可作为数据通道。分别耦接于多条通道la[1]-la[5]的多个采样电路rx[1]-rx[5]可根据时钟信号5d_clk执行数据采样操作。请注意,能够作为一时钟树以分配时钟信号5d_clk的多个多工器624.0-624.5,可以用来实施图5a所示的时钟树群组g1中的时钟树524a。

[0066]

在集成电路610用于支持“2d1c”分岔通道配置(lane configurations with bifurcation)的另一模式中,多个多工器624.0-624.2中的各多工器用以将输出端t

2d0

耦接于相应的采样电路,使输出端t

2d0

上的时钟信号2d_clk0可分配给多个采样电路rx[0]-rx

[2]中的各采样电路。多个多工器624.3-624.5中的各多工器用以将输出端t

2d1

耦接于相应的采样电路,使输出端t

2d1

上的时钟信号2d_clk1可分配给多个采样电路rx[3]-rx[5]中的各采样电路。多个多工器624.0-624.5可以用来实施图5b所示的时钟树群组g2中的多个时钟树524b.0和524b.1。因此,多个采样电路rx[0]-rx[5]可分为两组采样电路。集成电路610所处在的物理层可操作成分开的两个物理层,其中一物理层包括多条通道la[0]-la[2]以及多个采样电路rx[0]-rx[2],另一物理层包括多条通道la[3]-la[5]以及多个采样电路rx[3]-rx[5]。

[0067]

在集成电路610用于支持“1d1c”分岔通道配置的另一模式中,多个多工器624.0和624.1中的各多工器用以将输出端t

1d0

耦接于相应的采样电路,使输出端t

1d0

上的时钟信号1d_clk0可分配给多个采样电路rx[0]和rx[1]中的各采样电路。相似地,多个多工器624.2和624.3中的各多工器用以将输出端t

1d1

耦接于相应的采样电路,使输出端t

1d1

上的时钟信号1d_clk1可分配给多个采样电路rx[2]和rx[3]中的各采样电路。多个多工器624.4和624.5中的各多工器用以将输出端t

1d2

耦接于相应的采样电路,使输出端t

1d2

上的时钟信号1d_clk2可分配给多个采样电路rx[4]和rx[5]中的各采样电路。多个多工器624.0-624.5可以用来实施图5c所示的时钟树群组g3中的多个时钟树524c.0-524c.2。因此,多个采样电路rx[0]-rx[5]可分为三组采样电路。集成电路610所处在的物理层可操作成分开的三个物理层,以支持三个传输器。

[0068]

通过多个多工器522a、522b.0、522b.1和522c.0-522c.2,选取级622可操作成6对m多工器,其中及m可等于1、2或3(取决于集成电路610的模式)。此外,通过多个多工器624.0-624.5,选取级624可操作成m个时钟树,其中及m可等于1、2或3(取决于集成电路610的模式)。因此,集成电路610可将多条通道la[0]-la[5]分成一个或多个通道群组(groups of lanes),其中各通道群组包括时钟通道与数据通道,以支持一个或多个传输器。

[0069]

以上参照图6所述的电路结构与操作只是用于方便说明的目的,并非用来限制本申请的范围。在某些实施例中,集成电路610可操作在同时支持“3d1c”通道配置和“1d1c”通道配置的分岔模式中。举例来说,多个多工器624.0-624.3可用将输出端t

5d

耦接于相应的采样电路,使输出端t

5d

上的时钟信号5d_clk可分配给多个采样电路rx[0]-rx[3]中的各采样电路。多个多工器624.4和624.5中的各多工器用以将输出端t

1d2

耦接于相应的采样电路,使输出端t

1d2

上的时钟信号1d_clk2可分配给多个采样电路rx[4]和rx[5]中的各采样电路。因此,集成电路610所处在的物理层可操作成分开的两个物理层,以支持两个具有不同数据通道个数的传输器。

[0070]

在某些实施例中,在进行数据传输时,不使用作为数据通道的一通道也是可行的。举例来说,当用以支持“5d1c”通道配置时,集成电路610可使用五条或少于五条的数据通道以接收传输侧所传送的数据信息。所使用的数据通道的个数可取决于传送到多通道接口314的数据信号的个数。

[0071]

在某些实施例中,选取级622可利用其他多工器电路来实施,以回应集成电路610的模式来选取一条或多条通道。在某些实施例中,选取级624可利用其他时钟树结构来实施,以回应集成电路610的模式来分配一个或多个时钟信号。这些设计修改与变化均遵循本申请的精神而落入本申请的保护范围。

[0072]

图7是本申请某些实施例的图1所示的集成电路110的另一具体实施方式的示意

图。集成电路710可作为图1所示的集成电路110(其包括六条可通用于时钟通道与数据通道的通道,n=6)的实施例。于此实施例中,集成电路710可设置在物理层中的物理介质连接层,以执行串行到并行转换(serial-to-parallel conversion)。

[0073]

集成电路710包括一通道选取电路720、多个串行到并行转换器(serial-to-parallel converter,以下称为“s2p转换器”)730.0-730.5,以及图3所示的多通道接口314。通道选取电路720可作为图1所示的通道选取电路120的实施例,并可包括多个选取级722和724。选取级722可包括多个多工器722.0和722.1。多工器722.0用以根据一时钟选取信号sel

70

将多条通道la[0]-la[5]耦接于一输出端t

70

。多工器722.0用以根据一时钟选取信号sel

71

将多条通道la[0]-la[5]耦接于一输出端t

71

。选取级724可实施为包括一多工器724.0,其可根据一时钟选取信号sel

72

将多个输出端t

70

与t

71

耦接于一输出端t

72

。

[0074]

多个s2p转换器730.0-730.5中的各s2p转换器用以输出一多位并行输出信号。所述多位并行输出信号可以是一并行数据信号(parallel data signal)、一字节数据信号(byte data signal)、一并行时钟信号(parallel clock signal)或一字节时钟信号(byte clock signal)。于此实施例中,各s2p转换器包括一采样电路以及一反序列化器(deserializer)(即,图3所示的多个采样电路rx[0]-rx[5]其中的一个以及多个反序列化器ds[0]-ds[5]其中的一个)。多个反序列化器ds[0]-ds[5]可作为一输出电路740,其可根据多个采样电路rx[0]-rx[5]的采样结果sr输出一个或多个时钟信号。

[0075]

在集成电路710用于支持“5d1c”通道配置的模式中,多工器724.0用以将输出端t

70

耦接于输出端t

72

。当多工器722.0将多条通道la[0]-la[5]其中的一条通道选为一时钟通道时,所述时钟通道上的信号可耦接于输出端t

70

,并分配给多个采样电路rx[0]-rx[5]各自的时钟输入端c

in

。举例来说,多工器722.0可将通道la[0]选为时钟通道。多个采样电路rx[1]-rx[5]中的各采样电路均可根据相同的时钟信号(即,通道la[0]上的信号)进行数据采样。反序列化器ds[0]可根据采样结果sr输出一时钟信号(即,一并行时钟信号)。请注意,在此模式中,多个多工器722.0和724.0可作为图5a所示的时钟树群组g1的实施例。

[0076]

在集成电路710用于支持“2d1c”分岔通道配置的模式中,多工器724.0用以将输出端t

71

耦接于输出端t

72

。当多工器722.0将多条通道la[0]-la[5]其中的一条通道选为一时钟通道时,多工器722.1可将多条通道la[0]-la[5]其中的另一条通道选为一时钟通道。因此,可根据所选取的时钟通道上的信号来对剩余的通道上的信号进行采样。多个反序列化器ds[0]-ds[5]其中的两个反序列化器可根据采样结果sr输出两个时钟信号。举例来说,多工器722.0可将通道la[0]选为时钟通道,多个采样电路rx[1]和rx[2]中的各采样电路均可根据通道la[0]上的信号进行数据采样。多工器722.1可将通道la[3]选为时钟通道,多个采样电路rx[4]和rx[5]中的各采样电路均可根据通道la[3]上的信号进行数据采样。反序列化器ds[0]可输出与通道la[0]上的信号相关的一并行时钟信号,以及多个反序列化器ds[1]和ds[2]可分别输出与多条通道la[1]和la[2]上各自的信号相关的多个并行数据信号。此外,反序列化器ds[3]可输出与通道la[3]上的信号相关的一并行时钟信号,以及多个反序列化器ds[4]和ds[5]可分别输出与多条通道la[4]与la[5]上各自的信号相关的多个并行数据信号。在此模式中,多个多工器722.0、722.1和724.0可作为图5b所示的时钟树群组g2的实施例。

[0077]

以上参照图7所述的电路结构与操作并非用来限制本申请的范围。举例来说,通道

选取电路720可由图3所示的通道选取电路320或图6所示的通道选取电路620来实施,而不致背离本申请的范围。又例如,通道选取电路720中的多个多工器722.0、722.1与724.0可设置为图8所示的排列方式。请参阅图8,除了通道选取电路820之外,集成电路810的结构与图7所示的集成电路710的结构相似/相同。于此实施例中,多工器724.0可根据时钟选取信号sel

72

将多个时钟选取信号sel

70

与sel

71

其中的一个耦接于输出端t

71

。多工器722.1可根据多工器724.0所输出的信号将多条通道la[0]-la[5]耦接于输出端t

71

。由于本领域的技术人员在阅读图1至图7相关的段落说明之后,应可了解通道选取电路820的操作细节,因此,关于通道选取的进一步说明在此便不再赘述。

[0078]

请注意,为了方便通道选取,本申请所公开的时钟前送方案所使用的一时钟选取信号可具有映射到欲选取的一时钟通道的一通道标识符(lane identifier)的信号值/信号模式(signal pattern)。通道选取电路可根据所述时钟选取信号来选取此时钟通道。在某些实施例中,所述通道标识符可以是所选取的时钟通道的通道名称(lane name)、位于所选取的时钟通道中的信号引脚(signal pin)的引脚名称(pin name),或信号引脚的引脚编号(pin number)。例如,所述通道标识符可以标记在具有所选取的时钟通道的一集成电路所设置的电路板上,或标记在膠封(encapsulate)所述集成电路的封装体(package)上。又例如,所述通道标识符可以标记或描述于所述集成电路的数据表(datasheet)、数据手册(data book)或装置规格(device specification)中。在某些实施例中,所述通道标识符可以是所选取的时钟通道携带的识别信息。所述集成电路可通过侦测所述识别信息来决定哪条通道应该被选为时钟通道。

[0079]

请再次参阅图7。集成电路710还包括一控制电路750,其可用来产生多个时钟选取信号sel

70-sel

72

以控制通道选取电路720。当时钟选取信号sel

70

/sel

71

具有映射到多条通道la[0]-la[5]中的一通道的通道标识符的信号值时,通道选取电路720可根据时钟选取信号sel

70

/sel

71

选取多条通道la[0]-la[5]中的所述通道。于此实施例中,多条通道la[0]-la[5]各自的通道标识符均可包括一数字符号(numeral symbol),以及多条通道la[0]-la[5]各自的通道标识符所包括的多个数字符号指示出一组连续数字(a group of consecutive numbers)。举例来说(但本申请不限于此),一通道所对应的一引脚名称可作为所述通道的一通道标识符。通道la[0]的一对信号引脚可命名为“dp0”和“dn0”,通道la[1]的一对信号引脚可命名为“dp1”和“dn1”,以此类推。多个引脚名称dp0-dp5各自的数字符号(即,“0

”-“

5”)可指示出一组连续数字(0-5)。

[0080]

于此实施例中,控制电路750可回应一控制输入in

ct7

产生多个时钟选取信号sel

70-sel

72

,其中控制输入in

ct7

可指示出所选取的时钟通道的一通道标识符的信息。控制输入in

ct7

可包括(但不限于)一模式选取信号mss、一通道选取信号cks0以及一通道选取信号cks1。模式选取信号mss可指示出集成电路710的模式。举例来说,模式选取信号mss可包括一个位(bit)以指示出集成电路710是否操作在“1c”模式或“2c”模式。集成电路710操作在“1c”模式以通过多通道接口314接收单一时钟信号。集成电路710操作在“2c”模式以通过多通道接口314接收两个时钟信号。

[0081]

通道选取信号cks0可包括(但不限于)三个位,并可指示出所选取的一时钟通道(即,多条通道la[0]-la[5]其中的一条)的一通道标识符。通道选取信号cks0可具有映射到所选取的所述时钟通道的所述通道标识符的位模式或信号值。例如,具有位模式“000”(对

应于信号值“0”)的通道选取信号cks0可指示出通道la[0]被选为时钟通道。又例如,具有位模式“011”(对应于信号值“3”)的通道选取信号cks0可指示出通道la[3]被选为时钟通道。

[0082]

通道选取信号cks1可包括(但不限于)三个位,并可指示出所选取的一时钟通道(即,多条通道la[0]-la[5]其中的一条)的一通道标识符。通道选取信号cks1可具有映射到所选取的所述时钟通道的所述通道标识符的位模式或信号值。当集成电路710操作在“2c”模式以通过所选取的两条时钟通道接收两个时钟信号时,通道选取信号cks0可指示出所选取的所述两条时钟通道的其中一条的一通道标识符,通道选取信号cks1可指示出所选取的所述多条时钟通道的其中另一条的一通道标识符。例如,当多个通道选取信号cks0和cks1于“2c”模式中分别具有位模式“000”和“011”时,控制输入in

ct7

可指示出通道la[0]和通道la[3]均被选为时钟通道以分别接收相应的时钟信号。

[0083]

于操作中,当集成电路710操作在一模式(诸如“1c”模式)中以通过多通道接口314接收单一时钟信号cka时,控制电路750可回应控制输入in

ct7

产生时钟选取信号sel

72

。时钟选取信号sel

72

可具有一第一信号值,使输出端t

70

上的信号可分配给各采样电路。例如,控制电路750可根据模式选取信号mss产生时钟选取信号sel

72

。又例如,控制电路750可将模式选取信号mss作为时钟选取信号sel

72

。值得注意的是,在某些实施例中,控制输入in

ct7

中的模式选取信号mss可直接输入到多工器724.0,以作为时钟选取信号sel

72

。

[0084]

此外,控制电路750可根据时钟信号cka输入的通道的通道标识符来产生时钟选取信号sel

70

。于此实施例中,控制电路750可根据通道选取信号cks0来产生时钟选取信号sel

70

,其中通道选取信号cks0可指示出时钟信号cka输入的通道的通道标识符。举例来说,当通道选取信号cks0指示出通道la[0]被设定为时钟通道以接收时钟信号cka时,控制电路750可根据通道选取信号cks0,产生具有信号值为“0”的时钟选取信号sel

70

,其映射到引脚名称dp0/dn0的数字符号“0”(即,通道la[0]的通道标识符)。又例如,当通道选取信号cks0指示出通道la[3]被设定为时钟通道以接收时钟信号cka时,控制电路750可根据通道选取信号cks0,产生具有信号值为“3”的时钟选取信号sel

70

,其映射到引脚名称dp3/dn3的数字符号“3”。值得注意的是,在某些实施例中,由于通道选取信号cks0可具有映射到所选取的时钟通道的通道标识符,控制电路750可将通道选取信号cks0作为时钟选取信号sel

70

。

[0085]

当集成电路710操作在另一模式(诸如“2c”模式)中以通过多通道接口314接收两个时钟信号ckb和ckc时,控制电路750可回应控制输入in

ct7

产生时钟选取信号sel

72

。时钟选取信号sel

72

可具有不同于所述第一信号值的一第二信号值。因此,输出端t

70

上的信号可分配给多个采样电路rx[0]-rx[2],而输出端t

71

上的信号可分配给多个采样电路rx[3]-rx[5]。例如,控制电路750可根据模式选取信号mss产生时钟选取信号sel

72

,或将模式选取信号mss作为时钟选取信号sel

72

。值得注意的是,在某些实施例中,控制输入in

ct7

中的模式选取信号mss可直接输入至多工器724.0,以作为时钟选取信号sel

72

。

[0086]

此外,控制电路750可根据时钟信号ckb输入的通道的通道标识符来产生时钟选取信号sel

70

,以及根据时钟信号ckc输入的通道的通道标识符来产生时钟选取信号sel

71

。于此实施例中,控制电路750可于上述另一模式(诸如“2c”模式)中,分别根据多个通道选取信号cks0和cks1来产生多个时钟选取信号sel

70

和sel

71

。例如,当多个通道选取信号cks0和cks1可指示出多条通道la[0]和la[3]被设定为时钟通道以分别接收多个时钟信号cka和ckc时,控制电路750可根据通道选取信号cks0产生具有信号值为“0”的时钟选取信号sel

70

,

以及根据通道选取信号cks1产生具有信号值为“3”的时钟选取信号sel

71

。值得注意的是,在某些实施例中,由于多个通道选取信号cks0和cks1均可具有映射到所选取的时钟通道的通道标识符,控制电路750可将多个通道选取信号cks0和cks1分别作为多个时钟选取信号sel

70

和sel

71

。

[0087]

在某些实施例中,传输侧可在发送一时钟信号至接收侧的一通道之前,发送一前导信号(preamble signal)到所述通道。通过侦测所述前导信号是否存在,接收侧可判断出所述时钟信号是否会抵达所述通道。当侦测到出现在接收侧的一预定通道上的一前导信号时,接收侧可操作在分岔模式以支持多时钟传输(multi-clock transmission)。举例来说,于图7所示的实施例中,控制电路750可包括一状态机(state machine)755以自动地选取集成电路710的模式。

[0088]

图9是根据本申请某些实施例的图7所示的状态机755的操作的示意图。请连同图7参阅图9。当集成电路710的物理层启用(enabled)时,状态机755可停留在状态st0(例如,初始状态)。于状态st0中,时钟选取信号sel

72

可具有所述第一信号值,使所选取的一时钟通道上的信号可通过输出端t

70

分配给各采样电路。经过一段时间t_wait之后,状态机755可进入状态st1,使控制电路750可用来侦测多通道接口314是否接收一前导信号。当所述前导信号在多通道接口314的一预定通道(即,所选取的另一时钟通道)上被侦测到时,状态机755可进入状态st2,以及时钟选取信号sel

72

可具有所述第二信号值,使集成电路710可操作在分岔模式。在所述预定通道停用(deactivated)之后,状态机755可回到状态st0。时钟选取信号sel

72

的信号值可被设为所述第一信号值。

[0089]

在某些实施例中,所述预定通道可以是时钟选取信号cks1所指示的通道。通过侦测一前导信号是否输入至通道选取信号cks1所指示的通道,控制电路750可决定出时钟选取信号sel

72

的信号值。在某些实施例中,除了通道选取信号cks1所指示的通道,控制电路750还可用来侦测是否有任何通道接收一前导信号。控制电路750所侦测的各通道均可对应于状态st1中所侦测的所述预定通道。

[0090]

以上所述的自动通道侦测操作只是用于说明的目的,并非用来限制本申请的范围。请再次参阅图7,在某些实施例中,图7所示的控制电路750可用来侦测是否有不止一个前导信号抵达多通道接口314。当侦测出不止一个前导信号抵达多通道接口314时,控制电路750可操作在分岔模式以支持多时钟传输。举例来说,控制电路750可耦接于多通道接口314,并可在侦测出一通道上的单个前导信号时,产生具有所述第一信号值的时钟选取信号sel

72

。当侦测出两条通道上的多个前导信号时,控制电路750可产生具有所述第二信号值的时钟选取信号sel

72

,使集成电路710操作在分岔模式。

[0091]

此外,以上所述的采用通道标识符与控制输入之间的映射关系来实现通道选取的实施方式只是用于说明的目的,并非用来限制本申请的范围。在某些实施例中,控制电路750可包括一解码器(decoder)(图7未示)。所述解码器可对一通道选取信号进行译码,以产生用于欲选取的一时钟通道的一时钟选取信号,其中所述通道选取信号具有映射到所述时钟通道的通道标识符的信号值/信号模式。因此,控制电路750可根据所述时钟通道的通道标识符与控制输入in

ct7

的所述通道选取信号之间的映射关系,正确地选取所述时钟通道。

[0092]

请注意,一通道选取信号的信号值(或一时钟选取信号的信号值)可直接或间接地对应/映射到(map)欲选取的一时钟通道的通道标识符。举例来说,当时钟信号cka/ckb输入

至通道la[0]时,通道选取信号cks0可具有位模式“000001”,其对应于映射到引脚名称dp0/dn0的数字符号“0”的信号值“2

0”。此外,或替代地,控制电路750可产生具有位模式“000001”的时钟选取信号sel

70

,其中位模式“000001”对应于映射到引脚名称dp0/dn0的数字符号“0”的信号值“2

0”。又例如,当时钟信号ckc输入至通道la[3]时,通道选取信号cks1可具有位模式“001000”,其对应于映射到引脚名称dp3/dn3的数字符号“3”的信号值“2

3”。此外,或替代地,控制电路750可产生具有位模式“001000”的时钟选取信号sel

71

,其中位模式“001000”对应于映射到引脚名称dp3/dn3的数字符号“3”的信号值2

3”。

[0093]

在某些实施例中,其他类型的通道标识符(诸如通道名称、引脚编号,或通道所携带的识别信息)可映射到通道选取信号的信号值。在某些实施例中,控制电路750可根据其他类型的通道标识符(诸如通道名称、引脚编号,或通道所携带的识别信息)来决定时钟选取信号的信号值。在某些实施例中,通道标识符的数字符号可具有阿拉伯数字的形式、罗马数字的形式、字母的形式,或其他类型的数字符号的形式。在某些实施例中,多个通道标识符各自的数字符号所指示的一组连续数字可以是多个连续奇数、多个连续偶数,或具有预定连续顺序的多个数字。例如,根据本申请的某些实施例,图7所示的多条通道la[0]-la[5]的通道标识符的某些实施例显示于图10。这些设计修改与变化均遵循本申请的精神而落入本申请的保护范围。

[0094]

以上所述的通道选取操作可应用于图1所示的集成电路110、图3所示的集成电路310、图5a至图5c所示的多个集成电路510a-510c、图6所示的集成电路610以及图8所示的集成电路810。举例来说,请再次参阅图3。集成电路310还包括一控制电路350,其可回应一控制输入in

ct3

产生多个时钟选取信号sel

00

、sel

01

与sel

10-sel

15

,从而控制通道选取电路320。

[0095]

控制输入in

ct3

可指示出所选取的时钟通道的通道标识符的信息。举例来说。控制输入in

ct3

可包括多个通道选取信号,其中各通道选取信号均可指示出所选取的一时钟通道的通道标识符的信息。控制电路350可根据一通道选取信号产生时钟选取信号sel

00

,以及根据另一通道选取信号产生时钟选取信号sel

01

。又例如,控制输入in

ct3

还可包括一模式选取信号,其可指示出集成电路310的模式。控制电路350可根据所述模式选取信号产生多个时钟选取信号sel

10-sel

15

。

[0096]

于“5d1c”通道配置中,多个时钟选取信号sel

10-sel

15

可具有相同的信号值,使多个输出侧s02与s12其中的一个可耦接于各采样电路。当时钟信号5d_clk输入至多条通道la[0]-la[2]中的一通道时,多个时钟选取信号sel

10-sel

15

可具有一第一信号值,使输出侧s02可耦接于各采样电路。控制电路350可根据控制输入in

ct3

中的一通道选取信号产生时钟选取信号sel

00

,其中所述通道选取信号具有映射到所述通道的通道标识符的信号值。此外,或替代地,时钟选取信号sel

00

可具有映射到所述通道的通道标识符的信号值。当时钟信号5d_clk输入至多条通道la[3]-la[5]中的一通道时,多个时钟选取信号sel

10-sel

15

可具有一第二信号值,使输出侧s12可耦接于各采样电路。控制电路350可根据控制输入in

ct3

中的另一通道选取信号产生时钟选取信号sel

01

,其中所述另一通道选取信号具有映射到所述通道的通道标识符的信号值。此外,或替代地,时钟选取信号sel

01

可具有映射到所述通道的通道标识符的信号值。

[0097]

于“2d1c”分岔通道配置中,多个时钟选取信号sel

10-sel

12

中的各时钟选取信号均可具有一信号值,其中所述信号值不同于多个时钟选取信号sel

13-sel

15

中的各时钟选取信

号的信号值。因此,输出侧s02可耦接于多个采样电路rx[0]-rx[2],而输出侧s12可耦接于多个采样电路rx[3]-rx[5]。由于时钟信号2d_clk0输入至多条通道la[0]-la[2]中的一通道,因此,控制电路350可根据控制输入in

ct3

中的一通道选取信号产生时钟选取信号sel

00

,其中所述通道选取信号具有映射到所述通道的通道标识符的信号值。此外,或替代地,时钟选取信号sel

00

可具有映射到所述通道的通道标识符的信号值。相似地,由于时钟信号2d_clk0输入至多条通道la[3]-la[5]中的一通道,因此,控制电路350可根据控制输入in

ct3

中的另一通道选取信号产生时钟选取信号sel

01

,其中所述另一通道选取信号具有映射到所述通道的通道标识符的信号值。此外,或替代地,时钟选取信号sel

01

可具有映射到所述通道的通道标识符的信号值。

[0098]

在某些实施例中,时钟选取信号sel

00

和时钟选取信号sel

01

可实施为单个时钟选取信号。多个通道选取单元322.0和322.1均可根据所述单个时钟选取信号执行通道选取操作。控制电路350可根据欲选取的一条或多条通道的一个或多个通道标识符,来决定所述单一时钟选取信号的信号值/信号模式。举例来说,于“5d1c”通道配置中,所述单个时钟信号具有一信号值,其映射到时钟信号5d_clk输入的通道的通道标识符。又例如,于“2d1c”分岔通道配置中,所述单一时钟信号的前三个最低有效位(least significant bit,lsb)具有一信号值,其映射到多条通道la[0]-la[2]其中的一条通道的通道标识符。所述单一时钟信号的前三个最高有效位(most significant bit,msb)具有一信号值,其映射到多条通道la[3]-la[5]其中的一条通道的通道标识符。

[0099]

相似地,请再次参阅图1,集成电路110还包括一控制电路150,其可根据一控制输入in

ct1

产生一时钟选取信号,或根据所选取的多条时钟通道中的一通道的一通道标识符产生所述时钟选取信号。控制输入in

ct1

可指示出所述通道标识符。此外,或替代地,所述时钟选取信号可具有映射到所述通道标识符的信号值。因此,通道选取电路120可根据所述时钟选取信号来选取所述通道。此外,或替代地,在图5a、图5b、图5c与图6所示的实施例中,时钟选取信号sel

a

/sel

b1

/sel

b2

/sel

c1

/sel

c2

/sel

c3

的信号值可根据时钟信号输入的通道的通道标识符来决定。由于本领域的技术人员在阅读上述关于图7、图8和图3的段落说明之后,应可了解产生图5a、图5b、图5c和图6所示的时钟选取信号sel

a

/sel

b1

/sel

b2

/sel

c1

/sel

c2

/sel

c3

的细节,因此,进一步的说明在此便不再赘述。

[0100]

以上所述的通道互换方案与通道选取操作的至少其一可运用于物理层的其他子层中,诸如物理编码子层。图11是根据本申请某些实施例的一例示性接收器的功能方框示意图。接收器1104可作为图1所示的接收器104的实施例。接收器1104的物理层1108包括一物理介质连接层(pma)1105以及一物理编码子层(pcs)1107。物理介质连接层1105可采用参照图1至图10所述的电路结构与操作。

[0101]

物理介质连接层1105包括(但不限于)一多通道接口1114、一通道选取电路1120以及多个s2p转换器1130

0-1130

n-1

,其中n是大于1的整数。多通道接口1114和通道选取电路1120可分别作为图1所示的多通道接口114和通道选取电路120的实施例。多通道接口114可包括图1所示的n条通道la[0]-la[n-1]。通道选取电路1120用以根据一组时钟选取信号{sel

pma

}将多通道接口1114中的一条或多条通道选为一条或多条时钟通道。此外,多个s2p转换器1130

0-1130

n-1

可利用图1所示的n个采样电路rx[0]-rx[n-1]和输出电路140来实施。

[0102]

物理编码子层1107包括(但不限于)一多通道接口1116、一通道选取电路1122以及

多个处理电路1132

0-1132

n-1

。多通道接口1116可作为图1所示的多通道接口114的实施例。多通道接口1116包括耦接于物理介质连接层1105的n条通道ls[0]-ls[n-1]。通道选取电路1122可作为图1所示的通道选取电路120的实施例。通道选取电路1122用以根据一组时钟选取信号{sel

pcs

}将n条通道ls[0]-ls[n-1]中的一条或多条通道选为一条或多条时钟通道。n条通道ls[0]-ls[n-1]中的各通道均可通用于时钟通道与数据通道。此外,多个处理电路1132

0-1132

n-1

可实施为分别包括图1所示的n个采样电路rx[0]-rx[n-1],以根据来自物理介质连接层1105的一个或多个时钟信号进行数据采样。

[0103]

于操作中,物理介质连接层1105可用以输出分别与m个不同时钟域(clock domain)相关的m个时钟信号ckd

1-ckd

m

,m是小于n的正整数。物理编码子层1107可将n条通道ls[0]-ls[n-1]中的m条通道选为m条时钟通道以接收m个时钟信号ckd

1-ckd

m

。也就是说,回应物理介质连接层1105的通道选取操作,物理编码子层1107可执行相应的通道选取操作。举例来说,物理介质连接层1105的多通道接口1114可接收m个传输器(图11未示)所传送的m个时钟信号,以产生m个时钟信号ckd

1-ckd

m

,其中所述m个传输器分别操作在所述m个不同时钟域。通道选取电路1120可根据一组时钟选取信号{sel

pma

}来将多通道接口1114中的m条通道选为m条时钟通道。多个s2p转换器1130

0-1130

n-1

中的m个s2p转换器(耦接于所选取的m条通道)可分别产生m个时钟信号ckd

1-ckd

m

。回应物理介质连接层1105的通道选取操作,物理编码子层1107中的通道选取电路1122可根据一组时钟选取信号{sel

pcs

}来将n条通道ls[0]-ls[n-1]中的m条通道选为m条时钟通道。n条通道ls[0]-ls[n-1]中剩余的(n-m)条通道包括的一条或多条通道可作为一条或多条数据通道。多个处理电路1132

0-1132

n-1

可根据m个时钟信号ckd

1-ckd

m

对所述一条或多条数据通道上的数据进行处理。

[0104]

一组时钟选取信号{sel

pma

}以及一组时钟选取信号{sel

pcs

}可由物理介质连接层1105与物理编码子层1107共享的一控制输入所产生。于此实施例中,物理编码子层1107还可包括一控制电路1150,其可作为图1所示的控制电路150的实施例。控制电路1150可根据一控制输入in

ctrl

产生一组时钟选取信号{sel

pma

}及一组时钟选取信号{sel

pcs

}。控制输入in

ctrl

可指示出物理介质连接层1105中所选取的时钟通道的通道标识符,以及指示出物理编码子层1107中所选取的时钟通道的通道标识符。举例来说,当控制输入in

ctrl

具有映射到物理介质连接层1105的通道la[0]的通道标识符的信号模式/信号值时,控制电路1150可根据控制输入in

ctrl

产生一组时钟选取信号{sel

pma

},使通道la[0]可被设定为时钟通道以接收传输器(图11未示)所传送的时钟信号。此外,控制电路1150可根据控制输入in

ctrl

产生一组时钟选取信号{sel

pcs

},使通道ls[0](具有映射到控制输入in

ctrl

的信号模式/信号值的通道标识符)可被设定为时钟通道以接收物理介质连接层1105所输出的时钟信号,其中物理介质连接层1105所输出的时钟信号是回应传输器所传送的时钟信号而产生。

[0105]

举例来说(但本申请不限于此),控制输入in

ctrl

可包括多个通道选取信号,其中各通道选取信号均可指示出所选取的一时钟通道的通道标识符。又例如,控制输入in

ctrl

可一模式选取信号以及多个通道选取信号,其中所述模式选取信号可指示出接收器1104的模式,诸如“1c”模式或分岔模式。由于本领域的技术人员在阅读图1至图10相关的段落说明之后,应可了解控制电路1150可采用通道标识符与控制输入之间的映射关系来控制通道选取电路1120和通道选取电路1122,因此,关于通道选取的重复说明在此便不再赘述。

[0106]

在某些实施例中,共享的控制电路1150可设置于物理介质连接层1105中,而不是

设置于物理编码子层1107中。在某些实施例中,物理介质连接层1105可具有一第一控制电路设置于其中,而物理编码子层1107可具有一第二控制电路设置于其中。所述第一控制电路和所述第二控制电路可根据相同的控制输入(诸如控制输入in

ctrl

)来控制通道选取操作。这些设计修改与变化均遵循本申请的精神而落入本申请的保护范围。

[0107]

以下提供一些实施例以进一步说明采用通道互换方案的物理编码子层1107。本领域的技术人员应可了解,采用了参照图1至图10所述的通道互换方案的其他物理编码子层均遵循本申请的精神而落入本申请的保护范围。

[0108]

图12是根据本申请某些实施例的图11所示的物理编码子层1107中的一集成电路的实施例的示意图。物理编码子层1207中的集成电路1210可作为图1所示的集成电路110(其包括六条可通用于时钟通道与数据通道的通道,n=6)的实施例。于此实施例中,物理编码子层1207用以接收物理介质连接层(pma)1205所传送的时钟与数据信息,其中物理介质连接层1205可作为图11所示的物理介质连接层1105的实施例。集成电路1210可包括一多通道接口1214、一通道选取电路1220以及多个采样电路rm[0]-rm[5]。多通道接口1214和通道选取电路1220可分别作为图1所示的多通道接口114和通道选取电路120的实施例。多个采样电路rm[0]-rm[5]可作为图1所示的多个采样电路rx[0]-rx[5]的实施例。

[0109]

多通道接口1214耦接于物理介质连接层1205,并包括图11所示的多条通道ls[0]-ls[5]。多条通道ls[0]-ls[5]可作为图1所示的n条通道la[0]-la[n-1]的实施例(即,n=6)。于此实施例中,多条通道ls[0]-ls[5]中的各通道可携带一多位输出信号(multi-bit output signal),诸如一字节数据信号或一字节时钟信号。

[0110]

通道选取电路1220用以将多条通道ls[0]-ls[5]中的一条或多条通道选为一条或多条时钟通道。剩余的通道中的一条或多条通道可作为一条或多条数据通道。通道选取电路1220包括(但不限于)多个选取级1222和1224,其可分别作为图1所示的多个选取级122和124的实施例。于此实施例中,选取级1222可回应集成电路1210的模式将一条或两条通道耦接于选取级1224。选取级1222包括多个通道选取单元1222.0和1222.1。通道选取单元1222.0用以根据一时钟选取信号sel

100

将多条通道ls[0]-ls[5]耦接于一输出端t

100

。通道选取单元1222.1用以根据一时钟选取信号sel

101

将多条通道ls[0]-ls[5]耦接于一输出端t

101

。选取级1224可实施为包括一通道选取单元1224.0,其可根据一时钟选取信号sel

102

将输出端t

100

和输出端t

101

其中的一个耦接于一输出端t

102

。

[0111]

多个采样电路rm[0]-rm[5]耦接于多通道接口1214和通道选取电路1220,用以根据物理介质连接层1205所传送的时钟信息与数据信息来进行数据采样。于此实施例中,多个采样电路rm[0]-rm[5]中的各采样电路可包括一时钟输入端pc

in

及一数据输入端pd

in

。各采样电路可利用输入到相应的时钟输入端pc

in

的信号,对输入到相应的数据输入端pd

in

的信号进行采样。

[0112]

在集成电路1210用于支持“4d1c”通道配置的模式中,通道选取单元1224.0用以将输出端t

100

耦接于输出端t

102

。当通道选取单元1222.0将多条通道ls[0]-ls[5]中的一通道选为一时钟通道时,所述时钟通道上的信号可耦接于输出端t

100

,并分配给多个采样电路rm[0]-rm[5]各自的时钟输入端pc

in

。举例来说,当一时钟信号输入至通道ls[0]时,通道选取单元1222.0可将通道ls[0]选为时钟通道,而多个采样电路rm[0]-rm[5]中的四个采样电路可根据相同的时钟信号(即,通道ls[0]上的信号)来进行数据采样。

[0113]

在集成电路1210用于支持“2d1c”分岔通道配置的模式中,通道选取单元1224.0用以将输出端t

101

耦接于输出端t

102

。当通道选取单元1222.0将多条通道ls[0]-ls[5]中的一通道选为一时钟通道时,通道选取单元1222.1可多条通道ls[0]-ls[5]中的另一通道选为一时钟通道。因此,可根据所选取的多条时钟通道上的信号来对剩余的多条通道上的信号进行采样。例如,当两个时钟信号分别输入至通道ls[1]和通道ls[4]时,通道选取单元1222.0可将通道ls[1]选为一时钟通道,而通道选取单元1222.1可将通道ls[4]选为另一时钟通道。多个采样电路rm[0]-rm[5]中的四个采样电路可根据涉及不同时钟域的这两个时钟信号来进行数据采样。

[0114]

值得注意的是,物理编码子层1207可采用前文所述的通道选取操作。于此实施例中,集成电路1210还包括一控制电路1250,其可根据一控制输入in

ct12

产生多个时钟选取信号sel

100-sel

102

,从而控制通道选取电路1220。举例来说,当物理介质连接层1205所传送的一时钟信号于“4d1c”通道配置中输入至多条通道ls[0]-ls[5]中的一通道时,控制电路1250可根据控制输入in

ct12

产生时钟选取信号sel

100

,其可指示出所述通道的通道标识符。又例如,当两个时钟信号于“2d1c”分岔通道配置中输入至多条通道ls[0]-ls[5]中的两条通道时,控制电路1250可根据控制输入in

ct12

产生时钟选取信号sel

100

,其可指示出所述两条通道其中的一条通道的通道标识符。此外,控制电路1250可根据控制输入in

ct12

产生时钟选取信号sel

101

,其可指示出所述两条通道其中的另一条通道的通道标识符。

[0115]

以上所述的通道选取操作可应用于数据通道选取操作。举例来说,通道选取电路1220还包括多个通道选取单元1232.0-1232.3,其可由控制电路1250所产生的多个数据选取信号sel

110-sel

113

所控制。于此实施例中,多个通道选取单元1232.0-1232.3可将物理介质连接层1205所传送的数据分别提供给多个采样电路rm[0]、rm[2]、rm[3]和rm[5]。

[0116]

在“4d1c”通道配置的模式中(多条通道ls[0]-ls[5]其中的一条被选为时钟通道),控制电路1250可根据控制输入in

ct12

产生多个数据选取信号sel

110-sel

113

,其中控制输入in

ct12

可指示出携带物理介质连接层1205所传送的数据信号的四条通道各自的通道标识符。举例来说,多个数据选取信号sel

110-sel

113

各自的信号值可分别映射到所述四条通道各自的通道标识符。

[0117]

在“2d1c”通道配置的模式中(多条通道ls[0]-ls[5]其中的两条通道选为时钟通道),控制电路1250可根据控制输入in

ct12

产生多个数据选取信号sel

110

和sel

111

,其中控制输入in

ct12

可指示出所述两条通道各自的通道标识符。所述两条通道可携带与通道选取单元1222.0所输出的时钟信号相关的数据信号。举例来说,多个数据选取信号sel

110

和sel

111

各自的信号值可分别映射到所述两条通道各自的通道标识符。此外,控制电路1250可根据另外两条通道各自的通道标识符产生多个数据选取信号sel

112

和sel

113

,其中所述另外两条通道可携带与通道选取单元1222.1所输出的时钟信号相关的数据信号。举例来说,多个数据选取信号sel

112

和sel

113

各自的信号值可分别映射到所述另外两条通道各自的通道标识符。

[0118]

由于本领域的技术人员应可了解,于时钟前送方案中所采用的数据通道选取操作可以与参照图1至图11所述的时钟通道选取操作相似/相同,因此,重复的说明在此便不再赘述。

[0119]

在某些实施例中,控制电路1250可由物理介质连接层1205与物理编码子层1207所

共享。举例来说,控制电路1250可产生一个或多个时钟选取信号,以控制物理介质连接层1205的时钟选取操作。又例如,控制电路1250可使用通道选取电路1220的一个或多个时钟选取信号,来控制物理介质连接层1205的通道选取电路(图12未示),从而使物理介质连接层1205和物理编码子层1207各自的通道选取操作彼此一致。

[0120]

值得注意的是,图12所示的通道选取电路1220的电路结构和操作只是用于说明的目的。在某些实施例中,通道选取电路1220可利用图1所示的通道选取电路120、图3所示的通道选取电路320、图5a至图5c所示的多个通道选取电路520a-520c、图6所示的通道选取电路620、图7所示的通道选取电路720、图8所示的通道选取电路820,以及前文所述相关的设计变化来实施,而不致背离本申请的范围。

[0121]

举例来说,请参阅图13,其为根据本申请某些实施例的图11所示的物理编码子层1107中的一集成电路的另一实施例的示意图。除了通道选取电路1320以外,物理编码子层1307的集成电路1310的结构可以与图12所示的集成电路1210的结构相似/相同。于此实施例中,通道选取电路1320中的选取级1322包括一通道选取单元1322.a、一通道选取单元1322.b以及图12所示的通道选取单元1222.1。通道选取单元1322.a可根据时钟选取信号sel

100

将多条通道ls[0]-ls[5]耦接于一输出端t

13a

,其中输出端t

13a

耦接于多个采样电路rm[0]-rm[2]各自的时钟输入端pc

in

。通道选取单元1322.b可根据时钟选取信号sel

100

将多条通道ls[0]-ls[5]耦接于一输出端t

13b

,其中输出端t

13b

耦接于通道选取单元1224.0。由于本领域的技术人员在阅读图1至图12相关的段落说明之后,应可了解通道选取电路1320的操作细节,因此,进一步的说明在此便不再赘述。

[0122]

此外,以上所述的通道选取方案也可应用传输侧。图14是根据本申请某些实施例的一例示性多通道通信系统的功能方框示意图。多通道通信系统1400可包括一传输器1402以及一接收器1404。传输器1402可作为图1所示的k个传输器tx[0]-tx[k-1]其中的一个的实施例。接收器1404可采用参照图1至图13所述的电路结构与操作。于此实施例中,传输器1402可致使于时钟通道上以及于数据通道上传输的信号彼此互换。传输器1402包括(但不限于)多个信号产生电路1410.0-1410.2、一通道选取电路1420、多个并列至串行转换器(parallel-to-serial converter,以下称为“p2s转换器”)1430.0-1430.2、一多通道接口1440以及一控制电路1450。

[0123]

多个信号产生电路1410.0-1410.2中的各信号产生电路可在数据总线(data bus)上产生一多位输出信号,诸如一并行时钟信号或一并行数据信号。于此实施例中,信号产生电路1410.0与信号产生电路1410.1均可由一数据信号产生器来实施,而信号产生电路1410.2可由一时钟信号产生器来实施。因此,多个信号产生电路1410.0和1410.1可分别在多个数据总线db0与db1产生多个并行数据信号pd0和pd1。信号产生电路1410.2可在数据总线db2产生一并行时钟信号pc0。

[0124]

通道选取电路1420耦接于多个信号产生电路1410.0-1410.2,用以将多个信号产生电路1410.0-1410.2所产生的多个多位输出信号分配给多个p2s转换器1430.0-1430.2。于此实施例中,通道选取电路1420包括多个通道选取单元1422.0-1422.2,其中各通道选取单元可根据相应的选取信号(即,多个选取信号sel

t0-sel

t2

其中的一个)来输出多个数据总线db0-db2上的多个输出信号其中的一个。

[0125]

多个p2s转换器1430.0-1430.2中的各p2s转换器可将一并行输出信号转换为一串

行输出信号(serial output signal)。多通道接口1440可作为图1所示的k个多通道接口tf[0]-tf[k-1]其中的一个的实施例。多通道接口1440可包括多条通道lt[0]-lt[2]。多条通道lt[0]-lt[2]中的至少一通道可通用于时钟通道与数据通道。于此实施例中,多条通道lt[0]-lt[2]中的各通道可利用一双线通道来实施,所述双线通道是包括一对信号引脚的差分通道。通道lt[0]的包括的一对信号引脚可命名为“dpt0”和“dnt0”,通道lt[1]的包括的一对信号引脚可命名为“dpt1”和“dnt1”,以此类推。在某些实施例中,多条通道lt[0]-lt[2]中的各通道均可利用其他类型的通道来实施,诸如单线通道或具有超过两线的通道,而不致背离本申请的范围。

[0126]

控制电路1450用以根据一控制输入in

ct14

产生多个选取信号sel

t0-sel

t2

,从而控制通道选取电路1420。多个选取信号sel

t0-sel

t2

中各选取信号的信号值均可根据控制输入in

ct14

来决定,其中控制输入in

ct14

可指示出一通道所对应的通道标识符。举例来说,接收器1404可将通道1406.0作为一时钟通道,以接收传输器1402所传送的时钟信息。通道1406.1和通道1406.2均可作为接收器1404的数据通道。通过将信号产生电路1410.2耦接于p2s转换器1430.0,通道选取单元1422.0可根据选取信号sel

t0

将通道lt[0](其耦接于通道1406.0)选为一时钟通道。控制电路1450可根据通道lt[0]的通道标识符(诸如引脚名称“dpt0/dnt0”或通道名称“lt[0]”)来决定选取信号sel

t0

的信号值。此外,通道选取单元1422.1可根据选取信号sel

t1

将通道lt[1]选为一数据通道,以及通道选取单元1422.2可根据选取信号sel

t2

将通道lt[2]选为一数据通道。由于本领域的技术人员在阅读上述关于接收侧的时钟/数据通道选取操作的段落说明之后,应可了解通道选取电路1420的时钟/数据通道选取操作的细节,因此,进一步的说明在此便不再赘述。

[0127]

以上所述的电路结构只是用于说明的目的,并非用来限制本申请的范围。在某些实施例中,上述的多通道接口的通道个数可根据不同的设计需求及应用而改变。举例来说,多通道接口可根据不同的实施例而包括四条通道、八条通道或其他通道个数。在某些实施例中,上述的一个或多个通道选取单元可利用一个或多个多工器来实施,或利用其他具有信号路径选择能力的电路来实施。在某些实施例中,上述的一个或多个多工器可基于反相器、或逻辑门(or-logic gate)、其他具有信号路径选择能力的电路,或其组合来实施。

[0128]

通过可在时钟通道与数据通道之间互换使用的至少一通道,接收侧的物理层可支持传输侧的不同的通道配置。例如,物理层可分为多个物理接口以支持多个传输器。此外,可根据一时钟/数据通道的通道标识符来选择所述时钟/数据通道,以方便时钟/数据通道的选取。

[0129]

上文的叙述简要地提出了本申请某些实施例的特征,而使得本领域的技术人员能够更全面地理解本申请的多种态样。本领域的技术人员当可理解,其可轻易地利用本申请内容作为基础,来设计或更动其他工艺与结构,以实现与此处所述的实施方式相同的目的和/或达到相同的优点。本领域的技术人员应当明白,这些均等的实施方式仍属于本申请内容的精神与范围,且其可进行各种变更、替代与更动,而不会背离本申请内容的精神与范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1