一种信息加解密处理方法及装置与流程

1.本技术涉及信息技术领域,特别涉及一种信息加解密处理方法及装置。

背景技术:

2.sm4分组密码算法(原sms4分组密码算法)是一种被配置于电子设备中,可应用于电子设备间的保密通信或电子设备自身保密信息处理的解决方案。

3.2006年01月中国国家密码管理局发布无线局域网产品密码事宜公告,将sm4分组密码算法应用于无线局域网产品中,标志着sm4分组密码算法进入了商用化阶段。

4.sm4分组密码算法作为一种简洁、安全及高效的密码算法,其在信息加密保护及完整性校验功能领域得到很好的应用。在sm4分组密码算法应用过程中,算法运算效率一直是算法应用者们所关注的一个重要因素,然而,针对物联网等领域,在资源受限场景下的算法应用也同样有必要得到相应的关注。

5.sm4分组密码算法,分组长度为128比特,密钥长度为128比特,加解密算法与密钥扩展算法都采用32轮非线性迭代结构。算法加解密运算原理描述如下:将明文输入,用轮密钥进行32轮非线性迭代变换后进行反序运算得到密文输出,其中,32轮非线性迭代变换包括合成置换t、线性变换l、非线性变换τ和sbox(s盒)查表。

6.在sm4分组密码算法中,解密算法与加密算法的结构相同,只是轮密钥的使用顺序相反;对sm4分组密码算法加解密运算过程分析可知,sm4分组密码算法运算步骤核心为32轮非线性迭代结构(轮函数f),且合成置换t为非线性迭代结构的核心,即合成置换t处理效率直接决定算法加解密处理性能。因此,需要对合成置换t处理过程进行优化,提高sm4分组密码算法加解密运算单轮处理性能,进而实现在32轮循环调用中,算法加解密运算整体性能的提升。

7.综上所述,本技术提出一种优化现有的sm4分组密码算法加解密过程的方法及装置,以提升sm4分组密码算法加解密运算的性能,同时在方案选取上考虑了资源受限场景下的实际应用。

技术实现要素:

8.本技术提供一种信息加解密处理方法及装置,用以优化现有的sm4分组密码算法加解密过程,以提升sm4分组密码算法加解密运算性能。

9.第一方面,本技术提供一种信息加密处理方法,该方法包括:

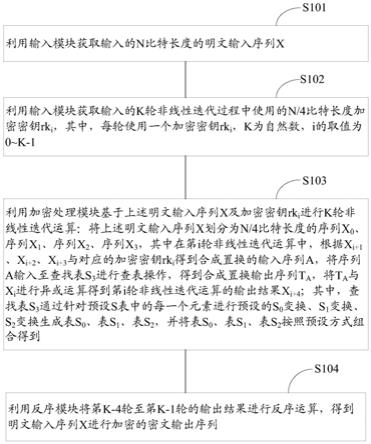

10.利用输入模块获取输入的n比特长度的明文输入序列x;

11.利用输入模块获取输入的k轮非线性迭代过程中使用的n/4比特长度加密密钥rki,其中,每轮使用一个加密密钥rki,k为自然数,i的取值为0~k-1;

12.利用加密处理模块基于所述明文输入序列x及加密密钥rki进行k轮非线性迭代运算:将所述明文序列x划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的加密密钥rki得到合成置换的输入序列a,将序

列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,所述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

13.利用反序模块将第k-4轮至第k-1轮的输出结果进行反序运算,得到所述明文输入序列x进行加密的密文输出序列。

14.上述方法中,优化了sm4分组密码算法加密过程中的合成置换运算,采用查s3表操作减少了sm4分组密码算法加密算法中合成置换的运算步骤,进而减少了sm4分组密码算法加密算法的复杂度,提升性能。

15.第二方面,本技术提供一种信息解密处理方法,该方法包括:

16.利用输入模块获取输入的n比特长度的密文输入序列x’;

17.利用输入模块获取输入的k轮非线性迭代过程中使用的n/4比特长度解密密钥rki,其中,每轮使用一个解密密钥rki,k为自然数,i的取值为0~k-1;

18.利用解密处理模块基于所述密文输入序列x’及解密密钥rki进行k轮非线性迭代运算:将所述密文输入序列x’划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的解密密钥rk

k-1-i

得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,所述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

19.利用反序模块将第k-4轮至第k-1轮的输出结果进行反序运算,得到所述密文输入序列x’进行解密的明文输出序列。

20.上述方法中,优化了sm4分组密码算法解密过程中的合成置换运算,采用查s3表操作减少了sm4分组密码算法解密算法中合成置换的运算步骤,进而减少了sm4分组密码算法解密算法的复杂度,提升性能。

21.第三方面,本技术提供一种信息加密处理的加密装置,包括:

22.输入模块,用于获取输入的n比特长度的明文输入序列x;以及用于获取输入的k轮非线性迭代过程中使用的n/4比特长度加密密钥rki,其中,每轮使用一个加密密钥rki,k为自然数,i的取值为0~k-1;

23.加密处理模块,用于基于所述明文输入序列x及加密密钥rki进行k轮非线性迭代运算:将所述明文序列x划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的加密密钥rki得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,所述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

24.反序模块,用于将第k-4轮至第k-1轮的输出结果进行反序运算,得到所述明文输入序列x进行加密的密文输出序列。

25.第四方面,本技术提供一种信息解密处理的解密装置,包括:

26.输入模块,用于获取输入的n比特长度的密文输入序列x’;以及用于获取输入的k轮非线性迭代过程中使用的n/4比特长度解密密钥rki,其中,每轮使用一个解密密钥rki,k为自然数,i的取值为0~k-1;

27.解密处理模块,用于基于所述密文输入序列x’及解密密钥rki进行k轮非线性迭代运算:将所述密文输入序列x’划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的解密密钥rk

k-1-i

得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,所述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

28.反序模块,用于将第k-4轮至第k-1轮的输出结果进行反序运算,得到所述密文输入序列x’进行解密的明文输出序列。

29.第五方面,本技术提供一种信息加密处理的加密设备,该设备包括处理器和存储器,所述存储器用于存储可执行程序,所述可执行程序被执行时,所述处理器实现如下过程:

30.获取输入的n比特长度的明文输入序列x;

31.获取输入的k轮非线性迭代过程中使用的n/4比特长度加密密钥rki,其中,每轮使用一个加密密钥rki,k为自然数,i的取值为0~k-1;

32.基于所述明文输入序列x及加密密钥rki进行k轮非线性迭代运算:将所述明文序列x划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的加密密钥rki得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,所述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

33.将第k-4轮至第k-1轮的输出结果进行反序运算,得到所述明文输入序列x进行加密的密文输出序列。

34.第六方面,本技术提供一种信息解密处理的解密设备,该设备包括处理器和存储器,所述存储器用于存储可执行程序,所述可执行程序被执行时,所述处理器实现如下过程:

35.获取输入的n比特长度的密文输入序列x’;

36.获取输入的k轮非线性迭代过程中使用的n/4比特长度解密密钥rki,其中,每轮使用一个解密密钥rki,k为自然数,i的取值为0~k-1;

37.基于所述密文输入序列x’及解密密钥rki进行k轮非线性迭代运算:将所述密文输入序列x’划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的解密密钥rk

k-1-i

得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,所述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

38.将第k-4轮至第k-1轮的输出结果进行反序运算,得到所述密文输入序列x’进行解密的明文输出序列。

39.另外,第三方面至第六方面中任一种实现方式所带来的技术效果可参见第一方面和第二方面所带来的技术效果,此处不再赘述。

附图说明

40.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简要介绍。显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域的普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

41.图1为本技术实施例1中提供的一种信息加密处理方法的流程图;

42.图2为本技术实施例1中提供的一种信息解密处理方法的流程图;

43.图3为本技术实施例2中提供的合成置换t的一种实施原理框图;

44.图4为本技术实施例3中提供的一种用于信息加密处理的加密装置的结构示意图;

45.图5为本技术实施例3中提供的一种用于信息加密处理的加密设备的结构示意图;

46.图6为本技术实施例4中提供的一种用于信息解密处理的解密装置的结构示意图;

47.图7为本技术实施例4中提供的一种用于信息解密处理的解密设备的结构示意图。

具体实施方式

48.为了使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术作进一步地详细描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本技术保护的范围。

49.下面对文中出现的一些词语进行解释:

50.本技术实施例中术语“和/或”,描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。字符“/”一般表示前后关联对象是一种“或”的关系。

51.本技术实施例描述的应用场景是为了更加清楚的说明本技术实施例的技术方案,并不构成对于本技术实施例提供的技术方案的限定,本领域普通技术人员可知,随着新应用场景的出现,本技术实施例提供的技术方案对于类似的技术问题,同样适用。其中,在本技术的描述中,除非另有说明,“多个”的含义是两个或两个以上。

52.sm4分组密码算法,分组长度为128比特,密钥长度为128比特,加解密算法与密钥扩展算法都采用32轮非线性迭代结构,其算法加解密运算原理描述如下:

53.(1)输入明文:

54.假设明文输入为x=(x0、x1、x2、x3),密文输出为y=(y0、y1、y2、y3),轮密钥为rki(i=0,1,2,

…

,31),其中,x0、x1、x2、x3,y0、y1、y2、y3,rki均为32比特的数据,i为加密过程或解密过程中非线性迭代变换的轮次的标识信息,i的取值为小于32的非负整数;

55.(2)32轮非线性迭代变换:

56.x

i+4

=f(xi,x

i+1

,x

i+2

,x

i+3

,rki)=xi⊕

t(x

i+1

⊕

x

i+2

⊕

x

i+3

⊕

rki),i=0、

57.1、2、

…

、31;其中:

58.合成置换t:t(a)=l(τ(a)),a=(a0、a1、a2、a3),其中a0~a3均为8比特数据,上述f为轮函数;

59.线性变换l:l(b)=b

⊕

(b《《《2)

⊕

(b《《《10)

⊕

(b《《《18)

⊕

(b《《《24),其中,

⊕

为异或运算,《《《为循环左移,b=(b0、b1、b2、b3)=τ(a),其中b0~b3均为8比特数据;

60.非线性变换τ:τ(a)=(sbox(a0),sbox(a1),sbox(a2),sbox(a3));sbox()为查s表操作,其中s表参见表1:

61.表1

[0062] 0123456789abcdef0d690e9fecce13db716b614c228fb2c0512b679a762abe04c3aa4413264986069929c4250f491ef987a33540b43edcfac623e4b31ca9c908e89580df94fa758f3fa644707a7fcf37317ba83593c19e6854fa85686b81b27164da8bf8eb0f4b70569d3561e240e5e6358d1a225227c3b012178877d40046579fd327524c3602e7a0c4c89e8eabf8ad240c738b5a3f7f2cef96115a19e0ae5da49b341a55ad933230f58cb1e3a1df6e22e8266ca60c02923ab0d534e6fbd5db3745defd8e2f03ff6a726d6c5b51c8d1baf92bbddbc7f11d95c411f105ad8d0ac13188a5cd7bbd2d74d012b8e5b4b0e8969974a0c96777e65b9f109c56ec684f18f07dec3adc4d2079ee5f3ed7cb3948

[0063]

上述表1中的数据均采用16进制表示,当查s表操作的输入序列为“ef”时,经过上述s盒后的值为上述表1中第e行和第f列的值,即当输入序列为“ef”时,查s表操作的输出结果为16进制的“84”。

[0064]

(3)将第28至第31轮的非线性迭代变换的结果x

32

、x

33

、x

34

、x

35

进行反序运算得到输出序列y;

[0065]

即y=(y0、y1、y2、y3)=r(x

32

,x

33

,x

34

,x

35

)=(x

35

,x

34

,x

33

,x

32

),其中r为反序运算。

[0066]

在sm4分组密码算法中,解密算法与加密算法的结构相同,只是轮密钥的使用顺序相反,在32轮非线性迭代变换过程中解密密钥的使用顺序是加密密钥的使用顺序的逆序,如下:

[0067]

加密时密钥的使用顺序为(rk0、rk1,

…

,rk

31

);

[0068]

解密时密钥的使用顺序为(rk

31

、rk

30

,

…

,rk0)。

[0069]

下面结合说明书附图对本技术实施例做进一步详细描述。

[0070]

本技术中,预先根据加密运算原理和解密运算原理,获取加密处理过程和解密处理过程中进行k轮非线性迭代运算中使用的查找表s3,并基于获得的查找表s3对明文输入序

列x进行加密处理,从而获得明文输入序列x的密文输出序列,或基于获得的查找表s3对密文输入序列x’进行解密处理,从而获得密文输入序列x’的明文输出序列。

[0071]

实施例1

[0072]

本技术实施例提供一种信息加密处理方法,可以将预先获取的查找表s3应用在本实施例的方法中,该方法可以应用于上述采用sm4分组密码算法进行加密处理的场景中。如图1所示,具体包括以下步骤:

[0073]

步骤s101,利用输入模块获取输入的n比特长度的明文输入序列x。

[0074]

步骤s102,利用输入模块获取输入的k轮非线性迭代过程中使用的n/4比特长度加密密钥rki,其中,每轮使用一个加密密钥rki,k为自然数,i的取值为0~k-1。

[0075]

步骤s103,利用加密处理模块基于上述明文输入序列x及加密密钥rki进行k轮非线性迭代运算:将上述明文输入序列x划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的加密密钥rki得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,并将表s0、表s1、表s2按照预设方式组合得到。

[0076]

作为一种实施例,在步骤s103中根据x

i+1

、x

i+2

、x

i+3

与对应的加密密钥rki得到合成置换的输入序列a时,可以将x

i+1

、x

i+2

、x

i+3

与对应的rki进行异或运算得到合成置换的输入序列a。

[0077]

步骤s104,利用反序模块将第k-4轮至第k-1轮的输出结果进行反序运算,得到明文输入序列x进行加密的密文输出序列。

[0078]

作为一种实施例,步骤s104中可以利用反序模块将第k-4轮至第k-1轮的输出结果xk、x

k+1

、x

k+2

、x

k+3

,变换为x

k+3

、x

k+2

、x

k+1

、xk的序列顺序,构成对上述明文输入序列x进行加密的密文输出序列。

[0079]

作为一种实施例,上述步骤s101至步骤s104中,n可以为128,k为32,s表为256字节元素组成的表,上述查找表s3包括至少一个子查找表,上述子查找表为1024字节元素组成的表。

[0080]

本技术实施例中查找表s3包括第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一、任二或任三,在利用预先获取的查找表s3实现sm4分组密码算法加密过程时,可以利用上述第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一个、任二个或任三个子查找表实现;即,在加密过程中通过查询m0s

30

+m1s

31

+m2s

32

+m3s

33

(m0≥0,m1≥0,m2≥0,m3≥0,0<m0+m1+m2+m3<4)的方式,完成加密过程中的合成置换处理;m0至m3分别表示查询的第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

的数量,mqs

3q

(q为0或1或2或3)表征使用mq个子查找表s

3q

进行查表操作;其中子查找表s

30

、s

31

、s

32

、s

33

之间的关系将在后文中介绍。

[0081]

作为一种实施例,在步骤s103中,可以通过如下方式,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta:

[0082]

将序列a划分为n/16比特长度的序列a0、序列a1、序列a2、序列a3;

[0083]

将序列a0、序列a1、序列a2、序列a3分别输入至查找表s3进行查表操作,对应得到n/4

比特长度的序列b0、序列b1、序列b2、序列b3,并基于移位原则对查表操作结果进行处理;对处理后的查表操作结果进行异或运算得到合成置换输出序列ta;其中,移位原则包括,若序列b0是序列a0通过第一子查找表s

30

进行查表操作获得的,则不对序列b0进行移位处理;若序列b1是序列a1通过第二子查找表s

31

进行查表操作获得的,则不对序列b1进行移位处理;若序列b2是序列a2通过第三子查找表s

32

进行查表操作获得的,则不对序列b2进行移位处理;若序列b3是序列a3通过第四子查找表s

33

进行查表操作获得的,则不对序列b3进行移位处理。

[0084]

作为一种实施例,将序列a0、序列a1、序列a2、序列a3分别输入至查找表s3进行查表操作,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,并基于移位原则对查表操作结果进行处理;对处理后的查表操作结果进行异或运算得到合成置换输出序列ta的过程中,可以通过查询上述m0s

30

+m1s

31

+m2s

32

+m3s

33

(m0≥0,m1≥0,m2≥0,m3≥0,0<m0+m1+m2+m3<4),得到合成置换输出序列ta。

[0085]

以下给出0<m0+m1+m2+m3<4时的几种示例性的例子,其中示例a1至a4为m0+m1+m2+m3=1时的示例,示例b1至b2为m0+m1+m2+m3=2时的示例,示例c为m0+m1+m2+m3=3时的示例。

[0086]

示例a1:仅查询第一子查找表s

30

[0087]

将序列a0、序列a1、序列a2、序列a3分别输入至第一子查找表s

30

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b1、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b1循环左移n/16位,b2循环左移n/8位,b3循环左移3n/16位;

[0088]

示例a2:仅查询第二子查找表s

31

[0089]

将序列a0、序列a1、序列a2、序列a3分别输入至第二子查找表s

31

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移3n/16位,b2循环左移n/16位,b3循环左移n/8位;

[0090]

示例a3:仅查询第三子查找表s

32

[0091]

将序列a0、序列a1、序列a2、序列a3分别输入至第三子查找表s

32

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/8位,b1循环左移3n/16位,b3循环左移n/16位;

[0092]

示例a4:仅查询第四子查找表s

33

[0093]

将序列a0、序列a1、序列a2、序列a3分别输入至第四子查找表s

33

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b2进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/16位,b1循环左移n/8位,b2循环左移3n/16位。

[0094]

示例b1:仅查询两个相同的子查找表

[0095]

可选地,当同时查询两个第一子查找表s

30

时(m0=2,m1=0,m2=0,m3=0),将序列a0、序列a1分别输入至这两个第一子查找表s

30

,对应得到n/4比特长度的序列b0、序列b1,再将序列a2、序列a3分别输入至这两个第一子查找表s

30

,对应得到n/4比特长度的序列b2、序列b3,对b1、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b1循环左移n/16位,b2循环左移n/8位,b3循环左移3n/16位。

[0096]

可以理解的是,当同时查询两个第二子查找表s

31

、第三子查找表s

32

和第四子查找表s

33

时,其原理与上述查询两个第一子查找表s

30

相同,对应的移位操作可参考示例a2-a4,此处不再赘述。

[0097]

示例b2:仅查询两个不同的子查找表

[0098]

可选地,当同时查询第一子查找表s

30

和第三子查找表s

32

时(m0=1,m1=0,m2=1,m3=0),将序列a0输入至第一子查找表s

30

,同时将序列a2输入至第三子查找表s

32

,对应得到n/4比特长度的序列b0、序列b2,再将序列a1输入至第一子查找表s

30

,同时将序列a3输入至第三子查找表s

32

,对应得到n/4比特长度的序列b1、序列b3,对b1、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b1循环左移n/16位,b3循环左移n/16位。

[0099]

可选的,当同时查询第一子查找表s

30

和第二子查找表s

31

时(即m0=1,m1=1,m2=0,m3=0),其原理与上述同时查询第一子查找表s

30

和第三子查找表s

32

相同,将序列a0输入至第一子查找表s

30

,同时将序列a1输入至第一子查找表s

31

,对应得到n/4比特长度的序列b0、序列b1,再将序列a2输入至第一子查找表s

30

,同时将序列a3输入至第二子查找表s

31

,对应得到n/4比特长度的序列b2、序列b3,对b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b2循环左移n/8位,b3循环左移n/8位。

[0100]

可以理解的是,上面仅示意出了同时查询两个不同的子查找表的组合中的两种情况,其他组合的原理类似,对应的移位可以参考示例a1-a4,此处不再赘述。

[0101]

示例c:查询三个子查找表

[0102]

该示例中查询的三个子查找表可以是同一类型的子查找表,也可以是不同类型的子查找表,如三个子查找表为一个第一子查找表s

30

和两个第二子查找表s

31

,或三个子查找表为三个第四子查找表s

33

,或三个子查找表为一个第二子查找表s

31

、一个第三子查找表s

32

和一个第四子查找表s

33

等。

[0103]

具体查询时,可以将合成置换输入序列a0、序列a1、序列a2、序列a3中的两个输入序列分为一组,将其他两个输入序列每个单独作为一组,将三组输入序列分别输入至三个子查找表进行查询。

[0104]

需要说明的是,加密过程中同时使用4个子查找表时,资源占用将会大幅增加,因此在本技术中不推荐同时使用4个子查找表进行加密过程的做法,以下仅给出m0+m1+m2+m3=4时的几种示例性的例子:

[0105]

示例d1:仅查询四个相同的子查找表

[0106]

可选地,当同时查询四个第一子查找表s

30

时(即m0=4,m1=0,m2=0,m3=0),将序列a0、序列a1、序列a2、序列a3同时输入至四个第一子查找表s

30

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b1、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b1循环左移n/16位,b2循环左移n/8位,b3循环左移3n/16位;

[0107]

可以理解的是,当同时查询四个第二子查找表s

31

、第三子查找表s

32

和第四子查找表s

33

时,其原理与上述查询四个第一子查找表s

30

相同,对应的移位操作可参考示例a2-a4,此处不再赘述。

[0108]

示例d2:查询两组共四个子查找表,其中组内两个子查找表相同,组间子查找表不同

[0109]

可选地,当同时查询第一组两个第一子查找表s

30

和第二组两个第三子查找表s

32

时(m0=2,m1=0,m2=2,m3=0),将序列a0、序列a1分别输入至第一组两个第一子查找表s

30

,对应得到n/4比特长度的序列b0、序列b1,同时将序列a2、序列a3分别输入至第二组两个第三子查找表s

32

,对应得到n/4比特长度的序列序列b2、序列b3,对b1、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b1循环左移n/16位,b3循环左移n/16位。

[0110]

示例d3:查询四个不同的子查找表

[0111]

当同时查询第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

和第四子查找表s

33

时(即m0=1,m1=1,m2=1,m3=1),将序列a0、序列a1、序列a2、序列a3分别输入至第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

和第四子查找表s

33

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b2、b3进行异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0、b1、b2、b3均不移位。

[0112]

具体而言,上述加密处理方法较传统的sm4分组密码算法加密处理的过程的区别及优点如下:

[0113]

a、从协议层面上,传统的sm4分组密码算法加密处理的软件实现需要定义1个256字节的s盒(用于输入8个比特的序列,输出8个比特的序列),本技术在加密处理时软件实现仅需要定义1个1024字节的s盒(用于输入8个比特的序列,输出32个比特的序列),虽然占用硬件资源上有所增加,但协议实现上可减少1次循环移位和1次异或处理操作,性能上存在提升。

[0114]

b、从实现角度上,传统的sm4分组密码算法加密在进行s盒查表时,是以8比特输入和8比特输出方式进行实现的,针对于32比特的加密平台,在进行s盒查表之前首先需要将32比特的序列转换成4个8比特的序列,然后针对4个8比特的序列进行查表,查表输出4个8比特的序列,而后需要将查表输出的4个8比特的序列通过循环运算、与运算及或运算将4个8比特的序列合并成32比特的序列,以便进行后续的运算,而本技术中提供的s盒结构为,输入8比特序列输出32比特序列的s盒,因此在进行4次查表结束后,因其输出即为32比特的序列,可不涉及关于8比特序列到32比特序列的转换过程,减少了多步循环运算、与运算及或运算操作,因而性能上存在提升。

[0115]

本技术实施例中提供一种信息解密处理方法,可以将预先获取的查找表s3应用在本实施例的方法中,该方法可以应用于上述采用sm4分组密码算法进行解密处理的场景中,如图2所示,具体包括以下步骤:

[0116]

步骤s201,利用输入模块获取输入的n比特长度的密文输入序列x’。

[0117]

步骤s202,利用输入模块获取输入的k轮非线性迭代过程中使用的n/4比特长度解密密钥rki,其中,每轮使用一个解密密钥rki,k为自然数,i的取值为0~k-1。

[0118]

步骤s203,利用解密处理模块基于上述密文输入序列x’及解密密钥rki进行k轮非线性迭代运算:将上述密文输入序列x’划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的解密密钥rk

k-1-i

得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,上述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到。

[0119]

作为一种实施例,在步骤s203中根据x

i+1

、x

i+2

、x

i+3

与对应的解密密钥rk

k-1-i

得到合成置换的输入序列a时,可以将x

i+1

、x

i+2

、x

i+3

与对应的rk

k-1-i

进行异或运算得到合成置换的输入序列a。

[0120]

步骤s204,利用反序模块将第k-4轮至第k-1轮的输出结果进行反序运算,得到上述密文输入序列x’进行解密的明文输出序列。

[0121]

作为一种实施例,上述步骤s201至步骤s204中,n可以为128,k为32,s表为256字节元素组成的表,上述查找表s3包括至少一个子查找表,上述子查找表为1024字节元素组成的表。

[0122]

本技术实施例中查找表s3包括第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一、任二或任三,在利用预先获取的查找表s3实现sm4分组密码算法解密过程时,可以利用上述第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一个、任二个或任三个子查找表实现;即,本技术实施例在解密过程中通过查询上述m0s

30

+m1s

31

+m2s

32

+m3s

33

(m0≥0,m1≥0,m2≥0,m3≥0,0<m0+m1+m2+m3<4)的方式,完成解密过程中的合成置换处理;其中子查找表s

30

、s

31

、s

32

、s

33

之间的关系与加密处理方法中子查找表s

30

、s

31

、s

32

、s

33

之间的关系相同。

[0123]

作为一种实施例,在步骤s203中可以通过如下方式,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta:

[0124]

将序列a划分为n/16比特长度的序列a0、序列a1、序列a2、序列a3;

[0125]

将序列a0、序列a1、序列a2、序列a3分别输入至查找表s3进行查表操作,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,并基于移位原则对查表操作结果进行处理;对处理后的查表操作结果进行异或运算得到合成置换输出序列ta;其中,移位原则包括,若序列b0是序列a0通过对第一子查找表s

30

进行查表操作的方式获得的,则不对序列b0进行移位处理;若序列b1是序列a1通过第二子查找表s

31

进行查表操作的方式获得的,则不对序列b1进行移位处理;若序列b2是序列a2通过第三子查找表s

32

进行查表操作的方式获得的,则不对序列b2进行移位处理;若序列b3是序列a3通过第四子查找表s

33

进行查表操作的方式获得的,则不对序列b3进行移位处理。

[0126]

作为一种实施例,解密过程中将序列a0、序列a1、序列a2、序列a3分别输入至查找表s3进行查表操作,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,并基于移位原则对查表操作结果进行处理;对处理后的查表操作结果进行异或运算得到合成置换输出序列ta的过程的具体实施方式,可以参照上述加密处理过程中的示例a1至a4、示例b1至b2以及示例c的内容,此处不再重复描述。

[0127]

具体而言,上述解密处理方法较传统的sm4分组密码算法解密处理的过程的区别及优点如下:

[0128]

a、从协议层面上,传统的sm4分组密码算法解密处理的软件实现需要定义1个256字节的s盒(用于输入8个比特的序列,输出8个比特的序列),本技术在解密处理时软件实现仅需要定义1个1024字节的s盒(用于输入8个比特的序列,输出32个比特的序列),虽然占用硬件资源上有所增加,但协议实现上可减少1次循环移位和1次异或处理操作,性能上存在提升。

[0129]

b、从实现角度上,传统的sm4分组密码算法解密在进行s盒查表时,是以8比特输入和8比特输出方式进行实现的,针对于32比特的解密平台,在进行s盒查表之前首先需要将32比特的序列转换成4个8比特的序列,然后针对4个8比特的序列进行查表,查表输出4个8比特的序列,而后需要将查表输出的4个8比特的序列通过循环运算、与运算及或运算将4个8比特的序列合并成32比特的序列,以便进行后续的运算,而本技术中提供的s盒结构为,输入8比特序列输出32比特序列的s盒,因此在进行4次查表结束后,因其输出即为32比特的序

列,可不涉及关于8比特序列到32比特序列的转换过程,减少了多步循环运算、与运算及或运算操作,因而性能上存在提升。

[0130]

在上述步骤s101至步骤s104的加密处理过程中以及上述步骤s201至步骤s204的解密处理过程中,获取查找表s3时,首先根据sm4分组密码算法加密算法和解密算法中的合成置换特性,确定反映合成置换输入序列和输出序列间比特位变换关系的s0变换、s1变换、s2变换,进而可应用于加密处理的设备和解密处理的设备,根据s0变换、s1变换、s2变换合成表s0、表s1、表s2,进而根据表s0、表s1、表s2合成查找表s3,以下对此进行详细说明:

[0131]

(一)基于sm4分组密码算法加密算法和解密算法中的合成置换特性,确定合成置换输入序列和输出序列之间比特位的变换关系:

[0132]

步骤1)将32比特长度的查找表输出序列b划分为8比特长度的序列b0、b1、b2、b3;

[0133]

其中,传统的sm4分组密码算法加密处理或解密处理时,由于b=τ(a),b0、b1、b2、b3分别为合成置换输入序列a0、a1、a2、a3的s盒查询结果,即b0=sbox(a0),b1=sbox(a1),b2=sbox(a2),b3=sbox(a3);

[0134]

上述序列a为32比特长度的合成置换的输入序列,上述输入序列a0、a1、a2、a3是上述a按照8比特长度进行划分的序列;

[0135]

其中:

[0136]

b0={bit7,bit6,bit5,bit4,bit3,bit2,bit1,bit0};

[0137]

b1={bit15,bit14,bit13,bit12,bit11,bit10,bit9,bit8};

[0138]

b2={bit23,bit22,bit21,bit20,bit19,bit18,bit17,bit16};

[0139]

b3={bit31,bit30,bit29,bit28,bit27,bit26,bit25,bit24}。

[0140]

在本实施例中,每个bitj(j为0~31的整数)表示一个比特位;

[0141]

在本实施例中,采用简化比特形式表示上述序列b为下表2:

[0142]

表2

[0143]

313029282726252423222120191817161514131211109876543210

[0144]

在本实施例中,采用简化比特形式表示上述序列b循环左移2位(b《《《2)的结果为下表3:

[0145]

表3

[0146]

292827262524232221201918171615141312111098765432103130

[0147]

在本实施例中,采用简化比特形式表示上述序列b循环左移10位(b《《《10)的结果为下表4:

[0148]

表4

[0149]

212019181716151413121110987654321031302928272625242322

[0150]

在本实施例中,采用简化比特形式表示上述序列b循环左移18位(b《《《18)为下表5:

[0151]

表5

[0152]

131211109876543210313029282726252423222120191817161514

[0153]

在本实施例中,采用简化比特形式表示上述序列b循环左移24位(b《《《24)为下表6:

[0154]

表6

[0155]

765432103130292827262524232221201918171615141312111098

[0156]

步骤2)针对b进行循环移位及异或获得lb;

[0157]

其中lb=b

⊕

(b《《《2)

⊕

(b《《《10)

⊕

(b《《《18)

⊕

(b《《《24),在本实施例中,采用简化比特形式表示上述序列如下表7,其中每列对应各比特位进行异或运算:

[0158]

表7

[0159]

313029282726252423222120191817161514131211109876543210292827262524232221201918171615141312111098765432103130212019181716151413121110987654321031302928272625242322131211109876543210313029282726252423222120191817161514765432103130292827262524232221201918171615141312111098

[0160]

步骤3)将lb针对b0、b1、b2、b3比特位进行分类划分,获得简化后的lb表示如下表8:

[0161]

其中,由于lb为仅针对b进行循环移位及异或,因此简化比特形式表示的lb中各bit位均为b中相应bit位,因此可将lb针对b0、b1、b2、b3比特位进行分类划分,获得变换后的简化比特形式的lb表示;

[0162]

表8

[0163][0164]

步骤4)对变换后的简化比特形式表示的lb进行分析,获知针对b0、b1、b2、b3的各行对应的变换;

[0165]

其中,针对b0={bit7,bit6,bit5,bit4,bit3,bit2,bit1,bit0},其包含关于比特位的下述三种变换:

[0166]

表9

[0167][0168]

表10

[0169]

54321076

[0170]

表11

[0171][0172]

针对b1={bit15,bit14,bit13,bit12,bit11,bit10,bit9,bit8},其包含关于比特位的下述三种变换:

[0173]

表12

[0174]

13121110981514

[0175]

表13

[0176][0177]

表14

[0178][0179]

针对b2={bit23,bit22,bit21,bit20,bit19,bit18,bit17,bit16},其包含关于比特位的下述三种变换:

[0180]

表15

[0181]

2120191817162322

[0182]

表16

[0183][0184]

表17

[0185][0186]

针对b3={bit31,bit30,bit29,bit28,bit27,bit26,bit25,bit24},其包含关于bit位的下述三种变换:

[0187]

表18

[0188][0189]

表19

[0190]

[0191]

表20

[0192]

2928272625243130

[0193]

步骤5)对b0、b1、b2、b3对应的三种变换分析,获得针对b0、b1、b2、b3各字节内比特位进行的变换;

[0194]

通过分析可知,针对b0、b1、b2、b3各字节内比特位进行的三种变换,其形式完全相同,包括下述的s0变换、s1变换、s2变换;

[0195]

其中,上述s0变换、s1变换、s2变换分别如下表21、表22、表23;

[0196]

表21

[0197][0198]

表22

[0199]

54321076

[0200]

表23

[0201][0202]

根据上述s0变换、s1变换、s2变换,可获知上述则lb的b0、b1、b2、b3的各字节对应的变换布局如下表24:

[0203]

表24

[0204]b3 s2s0s1s1b

2 s1s2s0s1b

1 s1s1s2s0b

0 s0s1s1s2[0205]

(二)获取反映合成置换输入序列和输出序列间比特位的变换关系的表s0、表s1、表s2[0206]

根据上述(一)中获知的s0变换、s1变换、s2变换,获得s盒内各字节进行相应变换的表s0、表s1、表s2;

[0207]

由于上述s0变换、s1变换、s2变换均是针对b0、b1、b2、b3各字节相应比特位的变换,而b0、b1、b2、b3分别对应a0、a1、a2、a3针对sbox(s盒)的查表输出,如果将sbox表内各字节进行相应的s0变换、s1变换、s2变换,针对a0、a1、a2、a3进行查找,即可获得b0、b1、b2、b3相应变换后的结果,且sbox表内各字节进行相应的s0变换、s1变换、s2变换,其输出分别对应表s0、表s1、表s2;

[0208]

即针对预设s盒中的每个元素的8个比特位进行预设的s0变换生成表s0中对应的一个元素的8个比特位;

[0209]

针对预设s盒中的每个元素的8个比特位进行预设的s1变换生成表s1中对应的一个元素的8个比特位;

[0210]

针对预设s盒中的每个元素的8个比特位进行预设的s2变换生成表s2中对应的一个元素的8个比特位;

[0211]

上述s盒中每个元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit1、bit0,对应表s0中元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit7

⊕

bit1、bit6

⊕

bit0,对应表s1中元素的8个比特位的值为bit5、bit4、bit3、bit2、bit1、bit0、bit7、bit6,对应s2中元素的8个比特位的值为bit7

⊕

bit5、bit6

⊕

bit4、bit5

⊕

bit3、bit4

⊕

bit2、bit3

⊕

bit1、bit2

⊕

bit0、bit1、bit0;

[0212]

其中,每个上述bitp(p为0~7的整数)表示一个比特。

[0213]

上述表s0、表s1、表s2的具体内容分别参见下述表25、表26、表27:

[0214]

表25

[0215] 0123456789abcdef0d592eafdcfe23db516b414c128f82c0512b6698772abc04c0a84513264884069b29e4351f793ec9a7b33550b42eeccae633e7b11cabca08eb9782dc96f9748d3fa444607a5fff07217b881583c19e5874eaa5696a83b07065d989fbe80f4a71579f3561e240e5f6259d2a025227d3b012179857d70047569dd027534d3602e4a2c7cb9c8e9bd88d141c438b7a1f4f1cdfa6015a39e3ac5ca699341a54af913230f68eb3e0a1df5e12e8067c961c32923a90d524f6ebd6d83744ddfe8c2f03fc6b736c6d5a50c8f1bad90b9debe7e11da5d401f105bdbd0ac2318aa7ce7abf2d75d312bae6b6b2e8b68954b0c94767f64bbf209c66fc586f18f37cef3adf4c2078ed5e3ed4c83949

[0216]

表26

[0217] 0123456789abcdef05b42a7fb3387f4de58da500ba0efb0141ac9d6ad9a8fa100faa114c98251a18662720941d346bf62e9cc512c0db73fb289393ce70a62720a356027f52ebd53efc9a41d1c9ef3cfcd5cea0e65f0649b163da25a1ad06cac5916b2ee3af3c2dc15976d46789038798d61478a9488f1ec0484e11e75300195d7e4f9c4931d8089f8213237a8abfe2a4b011fe0d68edfcb3be7855486983ba75926ed06855b64ec8c0d732c68fa74db8bb80a992b8103a48cae344d39bdb576fdc157bf73abc0cffa9c9b5b16d45

c366cbe4aee77f2fd446771057c406963d2807c4229637edf6b4d14348e297d2c2e26a55e29305addf995e6c72417b91b12f60c3f5b3e8733580e5bb7df85f2fe421

[0218]

表27

[0219] 0123456789abcdef08ed04d06fc65c96b4e6e44ca88179c11187fbf2ae824614cf02545fbe6d9e1efd2ec4a1024d553f892ff04274f59f31cea3747f6c0ded2848c180a3c412a1b3c33e45b1b3b0c3fbf4b528f3dcc7de9173085c8c7857ab5f4b2a718473367b00ee9e1666b43626ef38952ab1aa8cd705a5989b784005e0be39fbb1acee0a7b20d4e8e684243a29a40dbd8612f2b3af61de54125960162934f7e4720119dffaf021bc756fa692e6a968afee2e0c08daf07391f76d3b81b7eb51a609b6930f03c2bad9dc3715cb97713da57a94c8355bd2c45635032b8d22c5f5a831f9974999a4905a58716470eadcdcb623cceab86f15d352dd1d6de94f7830895cd2ac79a09d5623c68be7dd68

[0220]

上述表25、表26和表27中的数据均采用16进制表示。

[0221]

(三)根据表s0、表s1、表s2获得查找表s3[0222]

可选地,将表s0、表s1、表s2按照预设方式组合得到查找表s3;

[0223]

上述将表s0、表s1、表s2按照预设方式组合得到查找表s3包括:

[0224]

将表s0、表s1、表s2,按照表s0、表s1、表s1、表s2的顺序组合得到第一子查找表s

30

;和/或

[0225]

将表s0、表s1、表s2,按照表s1、表s1、表s2、表s0的顺序组合得到第二子查找表s

31

;和/或

[0226]

将表s0、表s1、表s2,按照表s1、表s2、表s0、表s1的顺序组合得到第三子查找表s

32

;和/或

[0227]

将表s0、表s1、表s2,按照表s2、表s0、表s1、表s1的顺序组合得到第四子查找表s

33

。

[0228]

查找表s3可以包括上述第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一、任二或任三;在利用预先获取的查找表s3实现sm4分组密码算法加密过程和解密过程时,可以利用上述第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一个、任二个或任三个子查找表实现加密过程和解密过程;即,在加密过程和解密过程中通过查询上述m0s

30

+m1s

31

+m2s

32

+m3s

33

(m0≥0,m1≥0,m2≥0,m3≥0,0<m0+m1+m2+m3<4)的方式,完成加密过程和解密过程中的合成置换处理。

[0229]

其中,上述表s0、表s1、表s2均是8比特输入8比特输出的查找表,而第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

均是8比特输入32比特输出的查找表,第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

均为1024字节元素组成的表。

[0230]

下面的表28给出了第一子查找表s

30

的具体内容,其他第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

仅是s0、表s1、表s2组合方式上的不同,这里不再给出具体的表格。

[0231]

表28

[0232] 012......ef0d55b5b8e924242d0eaa7a74d......2cb0b09c0514141112bacac87669d9dfb986a6af2......0618181e9b6666fd29e7272ec4309094a51414110......aeb2b21c638989ea3e7939374b1cece7f1c70706c......3ffcfcc3a49a9a3e4461d1d5b071c1c1ba59e9e3b......4e3d3d73aaa2a208569a1 a1c86aadadc783060685......9f7676e935d4d4e161e787866249090b40e383836......79e1e198851e1e9b7d7535384000000004719195e......cb2323e89c7a7ae68e9abab42bdfefe43882a2aa2......15545441a38686259e3838360acbaba165c757529......b3c6c675e08f8f6fa1d747469f5dbdb2ee18b8b6a......4f3939766ebdbdd3bd6575781d86f6fb737dcdceb......5a6d6d3750454515c8f3636b91b6c6c77adbebe13......5b696932db6363b8d0a282822c20707c531c4c4f5......b6d2d264b2c2c270e8b2626ad68a5a5cd955e5ecb......c51b1bde86121294f18606078f3c3c3307cf5f589......39e4e4dd49212168

[0233]

上述表28中的数据均采用16进制表示。

[0234]

实施例2

[0235]

基于上述实施例1,本技术实施例给出一个以查询查找表s3的方式进行sm4分组密码算法加密过程或解密过程中的合成置换t运算的流程,其中上述查找表s3由上述实施例1获取的第一查找表s

30

构成:

[0236]

如图3所示,其为合成置换t的一种实施原理框图,其中包含1个第一子查找表s

30

,序列a=(a0、a1、a2、a3)作为合成置换t的输入序列,t(a)作为合成置换t输出序列,其中a为32比特数据,a0、a1、a2和a3均为8比特数据,其合成置换t的的具体实施步骤如下:

[0237]

步骤s301,将8比特数据a0、a1、a2和a3针对第一子查找表s

30

依次进行查表,查表操作共分为四轮,其中:

[0238]

第一轮s

30

查表,针对a0进行s

30

查表,输出为b0;

[0239]

第二轮s

30

查表,针对a1进行s

30

查表,输出为b1;

[0240]

第三轮s

30

查表,针对a2进行s

30

查表,输出为b2;

[0241]

第四轮s

30

查表,针对a3进行s

30

查表,输出为b3;

[0242]

步骤s302,查表结果依据b0⊕

(b1《《《8)

⊕

(b2《《《16)

⊕

(b3《《《24)构成ta,即合成置

换t的输出。

[0243]

实施例3

[0244]

如图4所示,基于相同的发明构思,本技术实施例提供一种信息加密处理的加密装置,该装置包括:

[0245]

输入模块401,用于获取输入的n比特长度的明文输入序列x;以及用于获取输入的k轮非线性迭代过程中使用的n/4比特长度加密密钥rki,其中,每轮使用一个加密密钥rki,k为自然数,i的取值为0~k-1;

[0246]

加密处理模块402,用于基于上述明文输入序列x及加密密钥rki进行k轮非线性迭代运算:将上述明文序列x划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的加密密钥rki得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,上述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

[0247]

反序模块403,用于将第k-4轮至第k-1轮的输出结果进行反序运算,得到上述明文输入序列x进行加密的密文输出序列。

[0248]

作为一种实施例,上述n可以为128,k为32,s表为256字节元素组成的表,上述查找表s3包括至少一个子查找表,上述子查找表为1024字节元素组成的表。

[0249]

作为一种实施例,上述查找表s3包括第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一、任二或任三,其中:

[0250]

第一子查找表s

30

通过将表s0、表s1、表s2,按照表s0、表s1、表s1、表s2的顺序组合得到;

[0251]

第二子查找表s

31

通过将表s0、表s1、表s2,按照表s1、表s1、表s2、表s0的顺序组合得到;

[0252]

第三子查找表s

32

通过将表s0、表s1、表s2,按照表s1、表s2、表s0、表s1的顺序组合得到;

[0253]

第四子查找表s

33

通过将表s0、表s1、表s2,按照表s2、表s0、表s1、表s1的顺序组合得到。

[0254]

作为一种实施例,加密处理模块402具体用于将x

i+1

、x

i+2

、x

i+3

与对应的rki进行异或运算得到合成置换的输入序列a。

[0255]

作为一种实施例,加密处理模块402具体用于将序列a划分为n/16比特长度的序列a0、序列a1、序列a2、序列a3;

[0256]

将序列a0、序列a1、序列a2、序列a3分别输入至查找表s3进行查表操作,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,并基于移位原则对查表操作结果进行处理;对处理后的查表操作结果进行异或运算得到合成置换输出序列ta;其中,移位原则包括,若序列b0是序列a0通过第一子查找表s

30

进行查表操作获得的,则不对序列b0进行移位处理;若序列b1是序列a1通过第二子查找表s

31

进行查表操作获得的,则不对序列b1进行移位处理;若序列b2是序列a2通过第三子查找表s

32

进行查表操作获得的,则不对序列b2进行移位处理;若序列b3是序列a3通过第四子查找表s

33

进行查表操作获得的,则不对序列b3进行移位处理。

[0257]

作为一种实施例,加密处理模块402具体用于将序列a0、序列a1、序列a2、序列a3分别输入至第一子查找表s

30

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b1、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b1循环左移n/16位,b2循环左移n/8位,b3循环左移3n/16位;或者

[0258]

将序列a0、序列a1、序列a2、序列a3分别输入至第二子查找表s

31

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移3n/16位,b2循环左移n/16位,b3循环左移n/8位;或者

[0259]

将序列a0、序列a1、序列a2、序列a3分别输入至第三子查找表s

32

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/8位,b1循环左移3n/16位,b3循环左移n/16位;或者

[0260]

将序列a0、序列a1、序列a2、序列a3分别输入至第四子查找表s

33

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b2进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/16位,b1循环左移n/8位,b2循环左移3n/16位。

[0261]

作为一种实施例,在构建查找表s3时,通过如下方式获得表s0、表s1、表s2,包括:

[0262]

针对预设s盒中的每个元素的8个比特位进行预设的s0变换生成表s0中对应的一个元素的8个比特位;

[0263]

针对预设s盒中的每个元素的8个比特位进行预设的s1变换生成表s1中对应的一个元素的8个比特位;

[0264]

针对预设s盒中的每个元素的8个比特位进行预设的s2变换生成表s2中对应的一个元素的8个比特位;

[0265]

上述s盒中每个元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit1、bit0,对应表s0中元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit7

⊕

bit1、bit6

⊕

bit0,对应表s1中元素的8个比特位的值为bit5、bit4、bit3、bit2、bit1、bit0、bit7、bit6,对应s2中元素的8个比特位的值为bit7

⊕

bit5、bit6

⊕

bit4、bit5

⊕

bit3、bit4

⊕

bit2、bit3

⊕

bit1、bit2

⊕

bit0、bit1、bit0。

[0266]

作为一种实施例,反序模块403具体用于将第k-4轮至第k-1轮的输出结果xk、x

k+1

、x

k+2

、x

k+3

,变换为x

k+3

、x

k+2

、x

k+1

、xk的序列顺序,构成上述输入序列x进行加密的密文输出序列。

[0267]

如图5所示,基于相同的发明构思,本技术实施例提供一种信息加密设备,该设备包括处理器501和存储器502,上述存储器502用于存储可执行程序,上述可执行程序被执行时,上述处理器501实现如下过程:

[0268]

获取输入的n比特长度的明文输入序列x;

[0269]

获取输入的k轮非线性迭代过程中使用的n/4比特长度加密密钥rki,其中,每轮使用一个加密密钥rki,k为自然数,i的取值为0~k-1;

[0270]

基于上述明文输入序列x及加密密钥rki进行k轮非线性迭代运算:将上述明文输入序列x划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的加密密钥rki得到合成置换的输入序列a,将序列a输入至

查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,上述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

[0271]

将第k-4轮至第k-1轮的输出结果进行反序运算,得到上述明文输入序列x进行加密的密文输出序列。

[0272]

作为一种实施例,n可以为128,k为32,s表为256字节元素组成的表,上述查找表s3包括至少一个子查找表,上述子查找表为1024字节元素组成的表。

[0273]

作为一种实施例,上述查找表s3包括第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一、任二或任三,其中:

[0274]

第一子查找表s

30

通过将表s0、表s1、表s2,按照表s0、表s1、表s1、表s2的顺序组合得到;

[0275]

第二子查找表s

31

通过将表s0、表s1、表s2,按照表s1、表s1、表s2、表s0的顺序组合得到;

[0276]

第三子查找表s

32

通过将表s0、表s1、表s2,按照表s1、表s2、表s0、表s1的顺序组合得到;

[0277]

第四子查找表s

33

通过将表s0、表s1、表s2,按照表s2、表s0、表s1、表s1的顺序组合得到。

[0278]

作为一种实施例,处理器501具体用于将x

i+1

、x

i+2

、x

i+3

与对应的rki进行异或运算得到合成置换的输入序列a。

[0279]

作为一种实施例,处理器501具体用于将序列a划分为n/16比特长度的序列a0、序列a1、序列a2、序列a3;

[0280]

将序列a0、序列a1、序列a2、序列a3分别输入至查找表s3进行查表操作,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,并基于移位原则对查表操作结果进行处理;对处理后的查表操作结果进行异或运算得到合成置换输出序列ta;其中,移位原则包括,若序列b0是序列a0通过第一子查找表s

30

进行查表操作获得的,则不对序列b0进行移位处理;若序列b1是序列a1通过第二子查找表s

31

进行查表操作获得的,则不对序列b1进行移位处理;若序列b2是序列a2通过第三子查找表s

32

进行查表操作获得的,则不对序列b2进行移位处理;若序列b3是序列a3通过第四子查找表s

33

进行查表操作获得的,则不对序列b3进行移位处理。

[0281]

作为一种实施例,处理器501具体用于,将序列a0、序列a1、序列a2、序列a3分别输入至第一子查找表s

30

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b1、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b1循环左移n/16位,b2循环左移n/8位,b3循环左移3n/16位;或者

[0282]

将序列a0、序列a1、序列a2、序列a3分别输入至第二子查找表s

31

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移3n/16位,b2循环左移n/16位,b3循环左移n/8位;或者

[0283]

将序列a0、序列a1、序列a2、序列a3分别输入至第三子查找表s

32

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/8位,b1循环左移3n/16位,b3循环左移n/16位;或

者

[0284]

将序列a0、序列a1、序列a2、序列a3分别输入至第四子查找表s

33

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b2进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/16位,b1循环左移n/8位,b2循环左移3n/16位。

[0285]

作为一种实施例,在构建查找表s3时,通过如下方式获得表s0、表s1、表s2,包括:

[0286]

针对预设s盒中的每个元素的8个比特位进行预设的s0变换生成表s0中对应的一个元素的8个比特位;

[0287]

针对预设s盒中的每个元素的8个比特位进行预设的s1变换生成表s1中对应的一个元素的8个比特位;

[0288]

针对预设s盒中的每个元素的8个比特位进行预设的s2变换生成表s2中对应的一个元素的8个比特位;

[0289]

上述s盒中每个元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit1、bit0,对应表s0中元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit7

⊕

bit1、bit6

⊕

bit0,对应表s1中元素的8个比特位的值为bit5、bit4、bit3、bit2、bit1、bit0、bit7、bit6,对应s2中元素的8个比特位的值为bit7

⊕

bit5、bit6

⊕

bit4、bit5

⊕

bit3、bit4

⊕

bit2、bit3

⊕

bit1、bit2

⊕

bit0、bit1、bit0。

[0290]

作为一种实施例,处理器501具体用于将第k-4轮至第k-1轮的输出结果xk、x

k+1

、x

k+2

、x

k+3

,变换为x

k+3

、x

k+2

、x

k+1

、xk的序列顺序,构成上述输入序列x进行加密的密文输出序列。

[0291]

实施例4

[0292]

如图6所示,基于相同的发明构思,本技术实施例提供一种信息解密处理的解密装置,该装置包括:

[0293]

输入模块601,用于获取输入的n比特长度的密文输入序列x’;以及用于获取输入的k轮非线性迭代过程中使用的n/4比特长度解密密钥rki,其中,每轮使用一个解密密钥rki,k为自然数,i的取值为0~k-1;

[0294]

解密处理模块602,用于基于上述密文输入序列x’及解密密钥rki进行k轮非线性迭代运算:将上述密文输入序列x’划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的解密密钥rk

k-1-i

得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,上述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

[0295]

反序模块603,用于将第k-4轮至第k-1轮的输出结果进行反序运算,得到上述密文输入序列x’进行解密的明文输出序列。

[0296]

作为一种实施例,n可以为128,k为32,s表为256字节元素组成的表,上述查找表s3包括至少一个子查找表,上述子查找表为1024字节元素组成的表。

[0297]

作为一种实施例,上述查找表s3包括第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一、任二或任三,其中:

[0298]

第一子查找表s

30

通过将表s0、表s1、表s2,按照表s0、表s1、表s1、表s2的顺序组合得

到;

[0299]

第二子查找表s

31

通过将表s0、表s1、表s2,按照表s1、表s1、表s2、表s0的顺序组合得到;

[0300]

第三子查找表s

32

通过将表s0、表s1、表s2,按照表s1、表s2、表s0、表s1的顺序组合得到;

[0301]

第四子查找表s

33

通过将表s0、表s1、表s2,按照表s2、表s0、表s1、表s1的顺序组合得到。

[0302]

作为一种实施例,解密处理模块602具体用于将x

i+1

、x

i+2

、x

i+3

与对应的rk

k-1-i

进行异或运算得到合成置换的输入序列a。

[0303]

作为一种实施例,解密处理模块602具体用于:

[0304]

将序列a划分为n/16比特长度的序列a0、序列a1、序列a2、序列a3;

[0305]

将序列a0、序列a1、序列a2、序列a3分别输入至查找表s3进行查表操作,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,并基于移位原则对查表操作结果进行处理;对处理后的查表操作结果进行异或运算得到合成置换输出序列ta;其中:若序列b0是序列a0通过对第一子查找表s

30

进行查表操作的方式获得的,则不对序列b0进行移位处理;若序列b1是序列a1通过第二子查找表s

31

进行查表操作的方式获得的,则不对序列b1进行移位处理;若序列b2是序列a2通过第三子查找表s

32

进行查表操作的方式获得的,则不对序列b2进行移位处理;若序列b3是序列a3通过第四子查找表s

33

进行查表操作的方式获得的,则不对序列b3进行移位处理。

[0306]

作为一种实施例,解密处理模块602具体用于:

[0307]

将序列a0、序列a1、序列a2、序列a3分别输入至第一子查找表s

30

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b1、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b1循环左移n/16位,b2循环左移n/8位,b3循环左移3n/16位;或者

[0308]

将序列a0、序列a1、序列a2、序列a3分别输入至第二子查找表s

31

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移3n/16位,b2循环左移n/16位,b3循环左移n/8位;或者

[0309]

将序列a0、序列a1、序列a2、序列a3分别输入至第三子查找表s

32

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/8位,b1循环左移3n/16位,b3循环左移n/16位;或者

[0310]

将序列a0、序列a1、序列a2、序列a3分别输入至第四子查找表s

33

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b2进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/16位,b1循环左移n/8位,b2循环左移3n/16位。

[0311]

作为一种实施例,在构建查找表s3时,通过如下方式获得表s0、表s1、表s2,包括:

[0312]

针对预设s盒中的每个元素的8个比特位进行预设的s0变换生成表s0中对应的一个元素的8个比特位;

[0313]

针对预设s盒中的每个元素的8个比特位进行预设的s1变换生成表s1中对应的一个

元素的8个比特位;

[0314]

针对预设s盒中的每个元素的8个比特位进行预设的s2变换生成表s2中对应的一个元素的8个比特位;

[0315]

上述s盒中每个元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit1、bit0,对应表s0中元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit7

⊕

bit1、bit6

⊕

bit0,对应表s1中元素的8个比特位的值为bit5、bit4、bit3、bit2、bit1、bit0、bit7、bit6,对应s2中元素的8个比特位的值为bit7

⊕

bit5、bit6

⊕

bit4、bit5

⊕

bit3、bit4

⊕

bit2、bit3

⊕

bit1、bit2

⊕

bit0、bit1、bit0。

[0316]

作为一种实施例,反序模块603具体用于将第k-4轮至第k-1轮的输出结果xk、x

k+1

、x

k+2

、x

k+3

,变换为x

k+3

、x

k+2

、x

k+1

、xk的序列顺序,构成上述输入序列x’进行解密的明文输出序列。

[0317]

如图7所示,基于相同的发明构思,本技术实施例提供一种信息解密设备,该设备包括处理器701和存储器702,上述存储器702用于存储可执行程序,上述可执行程序被执行时,上述处理器701实现如下过程:

[0318]

获取输入的n比特长度的密文输入序列x’;

[0319]

获取输入的k轮非线性迭代过程中使用的n/4比特长度解密密钥rki,其中,每轮使用一个解密密钥rki,k为自然数,i的取值为0~k-1;

[0320]

基于上述密文输入序列x’及解密密钥rki进行k轮非线性迭代运算:将上述密文输入序列x’划分为n/4比特长度的序列x0、序列x1、序列x2、序列x3,其中在第i轮非线性迭代运算中,根据x

i+1

、x

i+2

、x

i+3

与对应的解密密钥rk

k-1-i

得到合成置换的输入序列a,将序列a输入至查找表s3进行查表操作,得到合成置换输出序列ta,将ta与xi进行异或运算得到第i轮非线性迭代运算的输出结果x

i+4

;其中,上述查找表s3通过针对预设s表中的每一个元素进行预设的s0变换、s1变换、s2变换生成表s0、表s1、表s2,将表s0、表s1、表s2按照预设方式组合得到;

[0321]

将第k-4轮至第k-1轮的输出结果进行反序运算,得到上述密文输入序列x’进行解密的明文输出序列。

[0322]

作为一种实施例,n可以为128,k为32,s表为256字节元素组成的表,上述查找表s3包括至少一个子查找表,上述子查找表为1024字节元素组成的表。

[0323]

作为一种实施例,上述查找表s3包括第一子查找表s

30

、第二子查找表s

31

、第三子查找表s

32

、第四子查找表s

33

中的任一、任二或任三,其中:

[0324]

第一子查找表s

30

通过将表s0、表s1、表s2,按照表s0、表s1、表s1、表s2的顺序组合得到;

[0325]

第二子查找表s

31

通过将表s0、表s1、表s2,按照表s1、表s1、表s2、表s0的顺序组合得到;

[0326]

第三子查找表s

32

通过将表s0、表s1、表s2,按照表s1、表s2、表s0、表s1的顺序组合得到;

[0327]

第四子查找表s

33

通过将表s0、表s1、表s2,按照表s2、表s0、表s1、表s1的顺序组合得到。

[0328]

作为一种实施例,处理器701具体用于将x

i+1

、x

i+2

、x

i+3

与对应的rk

k-1-i

进行异或运

算得到合成置换的输入序列a。

[0329]

作为一种实施例,处理器701具体用于:

[0330]

将序列a划分为n/16比特长度的序列a0、序列a1、序列a2、序列a3;

[0331]

将序列a0、序列a1、序列a2、序列a3分别输入至查找表s3进行查表操作,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,并基于移位原则对查表操作结果进行处理;对处理后的查表操作结果进行异或运算得到合成置换输出序列ta;其中,移位原则包括,若序列b0是序列a0通过对第一子查找表s

30

进行查表操作的方式获得的,则不对序列b0进行移位处理;若序列b1是序列a1通过第二子查找表s

31

进行查表操作的方式获得的,则不对序列b1进行移位处理;若序列b2是序列a2通过第三子查找表s

32

进行查表操作的方式获得的,则不对序列b2进行移位处理;若序列b3是序列a3通过第四子查找表s

33

进行查表操作的方式获得的,则不对序列b3进行移位处理。

[0332]

作为一种实施例,处理器701具体用于:

[0333]

将序列a0、序列a1、序列a2、序列a3分别输入至第一子查找表s

30

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b1、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b1循环左移n/16位,b2循环左移n/8位,b3循环左移3n/16位;或者

[0334]

将序列a0、序列a1、序列a2、序列a3分别输入至第二子查找表s

31

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b2、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移3n/16位,b2循环左移n/16位,b3循环左移n/8位;或者

[0335]

将序列a0、序列a1、序列a2、序列a3分别输入至第三子查找表s

32

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b3进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/8位,b1循环左移3n/16位,b3循环左移n/16位;或者

[0336]

将序列a0、序列a1、序列a2、序列a3分别输入至第四子查找表s

33

,对应得到n/4比特长度的序列b0、序列b1、序列b2、序列b3,对b0、b1、b2进行移位及异或运算得到n/4比特长度的合成置换输出序列ta,其中,b0循环左移n/16位,b1循环左移n/8位,b2循环左移3n/16位。

[0337]

作为一种实施例,在构建查找表s3时,通过如下方式获得表s0、表s1、表s2,包括:

[0338]

针对预设s盒中的每个元素的8个比特位进行预设的s0变换生成表s0中对应的一个元素的8个比特位;

[0339]

针对预设s盒中的每个元素的8个比特位进行预设的s1变换生成表s1中对应的一个元素的8个比特位;

[0340]

针对预设s盒中的每个元素的8个比特位进行预设的s2变换生成表s2中对应的一个元素的8个比特位;

[0341]

上述s盒中每个元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit1、bit0,对应表s0中元素的8个比特位的值为bit7、bit6、bit5、bit4、bit3、bit2、bit7

⊕

bit1、bit6

⊕

bit0,对应表s1中元素的8个比特位的值为bit5、bit4、bit3、bit2、bit1、bit0、bit7、bit6,对应s2中元素的8个比特位的值为bit7

⊕

bit5、bit6

⊕

bit4、bit5

⊕

bit3、bit4

⊕

bit2、bit3

⊕

bit1、bit2

⊕

bit0、bit1、bit0。

[0342]

作为一种实施例,处理器701具体用于将第k-4轮至第k-1轮的输出结果xk、x

k+1

、x

k+2

、x

k+3

,变换为x

k+3

、x

k+2

、x

k+1

、xk的序列顺序,构成上述输入序列x’进行解密的明文输出序列。

[0343]

以上参照示出根据本技术实施例的方法、装置(系统)和/或计算机程序产品的框图和/或流程图描述本技术。应理解,可以通过计算机程序指令来实现框图和/或流程图示图的一个块以及框图和/或流程图示图的块的组合。可以将这些计算机程序指令提供给通用计算机、专用计算机的处理器和/或其它可编程数据处理装置,以产生机器,使得经由计算机处理器和/或其它可编程数据处理装置执行的指令创建用于实现框图和/或流程图块中所指定的功能/动作的方法。

[0344]

相应地,还可以用硬件和/或软件(包括固件、驻留软件、微码等)来实施本技术。更进一步地,本技术可以采取计算机可使用或计算机可读存储介质上的计算机程序产品的形式,其具有在介质中实现的计算机可使用或计算机可读程序代码,以由指令执行系统来使用或结合指令执行系统而使用。在本技术上下文中,计算机可使用或计算机可读介质可以是任意介质,其可以包含、存储、通信、传输、或传送程序,以由指令执行系统、装置或设备使用,或结合指令执行系统、装置或设备使用。

[0345]

显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1