视频数据熵编码硬件实现方法、设备、介质及程序产品

1.本技术涉及视频数据处理技术领域,尤其涉及一种视频数据熵编码硬件实现方法、设备、介质及程序产品。

背景技术:

2.随着计算机技术的发展,图像的应用越来越广泛。当前,为了对图像文件进行高效的存储和传输,针对图像数据的处理越来越重要,视频图像压缩与解压成为重要数据处理手段,目前,现有的视频熵编码方法中,通常包括二进制化、上下文分配、概率预测和二进制算术编码等处理过程,然而上述数据处理过程中,数据依赖性强,相互等待时间较长,导致熵编码器的编码吞吐率较低,进而导致视频数据熵编码的效率较低。

技术实现要素:

3.本技术的主要目的在于提供一种视频数据熵编码硬件实现方法、设备、介质及程序产品,旨在解决现有技术中的视频数据熵编码效率低的技术问题。

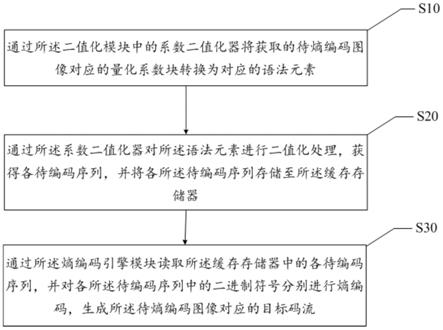

4.为实现上述目的,本技术提供一种视频数据熵编码硬件实现方法,所述视频数据熵编码硬件实现方法应用于视频数据熵编码硬件实现设备,所述视频数据熵编码硬件实现方法包括:

5.通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素;

6.通过所述系数二值化器对所述语法元素进行二值化处理,获得各待编码序列,并将各所述待编码序列存储至所述缓存存储器;

7.通过所述熵编码引擎模块读取所述缓存存储器中的各待编码序列,并对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流。

8.本技术还提供一种视频数据熵编码硬件实现装置,所述视频数据熵编码硬件实现装置为虚拟装置,且所述视频数据熵编码硬件实现装置应用于视频数据熵编码硬件实现设备,所述视频数据熵编码硬件实现装置包括:

9.转换模块,用于通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素;

10.二值化处理模块,用于通过所述系数二值化器对所述语法元素进行二值化处理,获得各待编码序列,并将各所述待编码序列存储至所述缓存存储器;

11.熵编码模块,用于通过所述熵编码引擎模块读取所述缓存存储器中的各待编码序列,并对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流。

12.本技术还提供一种视频数据熵编码硬件实现设备,所述视频数据熵编码硬件实现设备为实体设备,所述视频数据熵编码硬件实现设备包括:存储器、处理器以及存储在所述存储器上并可在所述处理器上运行的所述视频数据熵编码硬件实现方法的程序,所述视频

数据熵编码硬件实现方法的程序被处理器执行时可实现如上述的视频数据熵编码硬件实现方法的步骤。

13.本技术还提供一种介质,所述介质为可读存储介质,所述可读存储介质上存储有实现视频数据熵编码硬件实现方法的程序,所述视频数据熵编码硬件实现方法的程序被处理器执行时实现如上述的视频数据熵编码硬件实现方法的步骤。

14.本技术还提供一种计算机程序产品,包括计算机程序,所述计算机程序被处理器执行时实现如上述的视频数据熵编码硬件实现方法的步骤。

15.本技术提供了一种视频数据熵编码硬件实现方法、设备、介质及程序产品,相比于现有技术采用的数据依赖性强的编码处理流程的技术手段,本技术首先通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素,进而通过所述系数二值化器对所述语法元素进行二值化处理,获得各待编码序列,并将各所述待编码序列存储至所述缓存存储器,进而通过所述熵编码引擎模块读取所述缓存存储器中的各待编码序列,并对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流,进而实现了通过所述缓存存储器接收所述二值化模块发送的各待编码序列,也能通过所述熵编码引擎模块读取缓存的各待编码序列,从而降低所述二值化模块和所述熵编码引擎模块之间工作频率的差距,并行发送各所述待编码序列和读取各所述待编码序列的目的,所以,实现通过所述缓存存储器对所述待编码序列进行并行处理,缩短所述二值化模块和所述熵编码引擎模块之间相互等待时间的目的,克服了现有技术中编码数据处理过程中,数据依赖性强,相互等待时间较长,导致熵编码器的编码吞吐率较低,进而导致视频数据熵编码的效率较低的技术缺陷,从而提高了视频数据熵编码的效率。

附图说明

16.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本技术的实施例,并与说明书一起用于解释本技术的原理。

17.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,对于本领域普通技术人员而言,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

18.图1为本技术视频数据熵编码硬件实现方法第一实施例的流程示意图;

19.图2为本技术视频数据熵编码硬件实现方法中系数二值化器的流程示意图;

20.图3为本技术视频数据熵编码硬件实现方法第二实施例的流程示意图;

21.图4为本技术视频数据熵编码硬件实现方法中熵编码引擎模块中数据处理的流程示意图的流程示意图;

22.图5为本技术视频数据熵编码硬件实现方法中视频数据熵编码硬件实现设备的内部结构示意图;

23.图6为本技术实施例中视频数据熵编码硬件实现方法涉及的硬件运行环境的设备结构示意图。

24.本技术目的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

25.应当理解,此处所描述的具体实施例仅用以解释本技术,并不用于限定本技术。

26.本技术实施例提供一种视频数据熵编码硬件实现方法,在本技术视频数据熵编码硬件实现方法的第一实施例中,参照图1,所述视频数据熵编码硬件实现方法包括:

27.步骤s10,通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素;

28.在本实施例中,需要说明的是,所述视频数据熵编码硬件实现方法应用于熵编码器,所述熵编码器包括二值化模块、熵编码引擎模块和缓存存储器,所述待熵编码图像为从视频数据中抽取的图像,所述语法元素为所述待熵编码图像进行二值化处理的各种编码信息,所述二值化处理为将所述语法元素转化为二进制符号序列的方式,所述语法元素包括量化后的变换系数、划分信息、预测模式和所述待熵编码的序列头信息、帧头信息等标志位。

29.通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素,具体地,通过所述二值化模块中的系数二值化器读取存储在变换块寄存器中待熵编码图像对应的量化系数块,并对所述量化系数块中的量化系数进行游程编码,获得待熵编码图像的语法元素,其中,所述变换块寄存器为预先存储待熵编码图像对应的量化系数块的寄存器。

30.其中,所述熵编码器至少包括一具备所述二值化模块、所述熵编码引擎模块和所述缓存存储器的熵编码硬件单元,

31.在通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素的步骤之前,所述视频数据熵编码硬件实现方法包括:

32.步骤a10,获取目标视频图像帧,并对所述视频图像帧进行分割,获得所述视频图像帧对应的各待熵编码图像,并将各所述待熵编码图像并行输入各自对应的熵编码硬件单元;

33.在本实施例中,需要说明的是,所述目标视频图像帧为从视频数据中抽取的一帧图像,所述熵编码器至少包括一熵编码硬件单元,所述熵编码硬件单元包括一所述二值化模块、一所述熵编码引擎模块和一所述缓存存储器,且可设置多个所述熵编码硬件单元共用一所述缓存存储器。

34.获取目标视频图像帧,并对所述视频图像帧进行分割,获得所述视频图像帧对应的各待熵编码图像,并将各所述待熵编码图像并行输入各自对应的熵编码硬件单元,具体地,将所述目标视频图像帧分割为多个预设尺寸大小的各待熵编码图像,其中,所述预设尺寸大小可以设置为4*4、8*8和16*16等尺寸大小,进而将各所述待熵编码图像并行输入各自对应的熵编码硬件单元,以在各所述熵编码硬件单元中对各所述待熵编码图像并行进行所述二值化处理和熵编码处理等,从而提高视频数据熵编码的效率。

35.步骤a20,在所述对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流的步骤之后,所述视频编码方法还包括:

36.将所述目标视频图像帧对应的各目标码流分别重建为对应的待熵编码图像,并各所述待熵编码图像组合为所述目标视频图像帧。

37.在本实施例中,将所述目标视频图像帧对应的各目标码流分别重建为对应的待熵

编码图像,并各所述待熵编码图像组合为所述目标视频图像帧,具体地,在生成各所述待熵编码图像对应的目标码流之后,分别对各所述目标码流进行重建为各目标码流对应的待熵编码图像,进而将各所述待熵编码图像进行组合,获得所述目标视频图像帧。

38.其中,所述熵编码器至少包括一具备所述二值化模块、所述熵编码引擎模块和所述缓存存储器的熵编码硬件单元,

39.在所述通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素的步骤之前,所述视频编码方法还包括:

40.步骤b10,获取目标视频图像序列,并将所述目标视频图像序列中各目标视频图像子序列并行输入各自对应的熵编码硬件单元,其中,所述目标视频图像子序列至少包括一待熵编码图像;

41.在本实施例中,获取目标视频图像序列,并将所述目标视频图像序列中各目标视频图像子序列并行输入各自对应的熵编码硬件单元,其中,所述目标视频图像子序列至少包括一待熵编码图像,具体地,在所述目标视频图像序列中选取多个连续的待熵编码图像或者多个预设间隔帧数的待熵编码图像,并将各所述待熵编码图像组成所述目标视频图像子序列,进而将所述各目标视频图像子序列并行输入各自对应的熵编码硬件单元,以在各所述熵编码硬件单元并行地对各所述各目标视频图像子序列中的各待熵编码图像进行二值化处理、熵编码处理等。

42.步骤b20,在所述对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流的步骤之后,所述视频编码方法还包括:

43.将所述目标视频图像序列对应的各图像子序列码流分别重建为对应的目标视频图像子序列,并各所述目标视频图像子序列组合为各所述目标视频图像序列,其中,所述图像子序列码流至少包括一所述待熵编码图像对应的目标码流。

44.在本实施例中,将所述目标视频图像序列对应的各图像子序列码流分别重建为对应的目标视频图像子序列,并各所述目标视频图像子序列组合为各所述目标视频图像序列,其中,所述图像子序列码流至少包括一所述待熵编码图像对应的目标码流,具体地,在生成所述待熵编码图像对应的目标码流之后,通过各所述目标码流重建为对应的目标视频图像子序列,进而将各所述目标视频图像子序列进行组合,获得所述目标视频图像序列。

45.其中,所述通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素的步骤包括:

46.步骤s11,通过所述系数二值化器中的有限状态机生成所述待熵编码图像对应的量化系数块的寻址索引;

47.在本实施例中,需要说明的是,所述量化系数块是通过将所述待熵编码图像进行系数变换处理和量化处理获得的系数块,所述系数变换处理为将各所述待熵编码图像从时域信号变换到频域信号的处理方式,所述系数变换处理包括离散傅立叶变换和离散余弦变换等方式,所述量化系数块至少包括一量化系数,所述量化系数为量化系数块中的数值,所述寻址索引为与量化系数块大小相等的序列的索引,用于查找所述量化系数的访问地址,其中,所述访问地址为用于访问存储在所述变换块寄存器中的量化系数的地址。

48.通过所述系数二值化器中的有限状态机生成所述待熵编码图像对应的量化系数块的寻址索引,具体地,在变换块寄存器中确定所述待熵编码图像对应的量化系数块,通过

所述系数二值化器中有限状态机根据所述量化系数块的尺寸大小生成一维索引数组,并将所述一维索引数组作为所述寻址索引,例如,当所述量化系数块为具备64个系数值的二维矩阵时,对应的寻址索引则为[0,1,2,

…

,63]的一维序列,进而可通过计数器,每周期输出一个所述寻址索引。

[0049]

步骤s12,基于所述寻址索引,提取变换块寄存器中的量化系数块;

[0050]

在本实施例中,基于所述寻址索引,提取变换块寄存器中的量化系数块,具体地,根据所述寻址索引,在顺序查找表进行扫描寻址,获得所述量化系数块中各量化系数的访问地址,例如,当获取尺寸为8*8的视频图像帧,顺序查找表根据所述视频图像帧的尺寸生成64位的地址数组表,所述地址数组表为[0,1,2,

…

,63]的一维数组,进而根据所述寻址索引进行寻址扫描,获得所述访问地址,进而根据所述访问地址,当在所述变换块寄存器的各所述量化系数对应的地址中查询与所述访问地址一致的目标访问地址,获得所述目标访问地址对应的量化系数,其中,所述目标访问地址为所述访问地址和所述变换块寄存器中的量化系数地址一致的地址。

[0051]

步骤s13,对所述量化系数块中的量化系数进行游程编码,获得所述语法元素。

[0052]

在本实施例中,需要说明的是,所述游程编码为用于以不同的标志记录所述量化变换系数中的信息的方式。

[0053]

对所述量化系数块中的量化系数进行游程编码,获得所述语法元素,具体地,对各所述量化系数进行扫描,根据扫描的结果计算游程,获得所述语法元素,在计算游程过程中可获得(run,level)符号对、sign和last flag等中间变量,其中,所述run表示当前非零系数前连续出现零的个数,所述level表示非零系数的绝对值,所述sign表示非零系数的正负值,若当前非零系数为正数,则为0,若为负数,则为1,所述last flag为判断当前非零系数是否为量化系数块中最后一个非零系数的标志,若当前非零系数为最后一个非零系数,则记为1,若否,则为0,例如,对所述量化系数块进行zig

‑

zag型扫描,获得一维的扫描结果为(16,0,0,

‑

3,5,6,0,0,0,0,

‑

7,...),将所述扫描结果计算游程,可获得的(run,level)符号对为(0,16),(2,

‑

3),(0,5),(0,6),(4,

‑

7)...。

[0054]

步骤s20,通过所述系数二值化器对所述语法元素进行二值化处理,获得各待编码序列,并将各所述待编码序列存储至所述缓存存储器;

[0055]

在本实施例中,需要说明的是,所述二值化处理包括一元码二值化、截断一元码二值化或k阶指数哥伦布二值化等,所述待编码序列包括将各所述语法元素进行二值化获得的二进制符号序列和二进制符号序列中的各二进制符号对应的上下文模型序号等,所述缓存存储器为存储所述待编码序列的存储器,所述缓存存储器包括fifo存储器和其他存储信息的存储器。

[0056]

通过所述系数二值化器对所述语法元素进行二值化处理,获得各待编码序列,并将各所述待编码序列存储至所述缓存存储器,具体地,通过各所述系数二值化器分别对所述语法元素并行进行二值化,获得系数二值化结果,进而通过所述二值化模块的信息二值化器,对所述待熵编码图像的待编码信息进行二值化处理,获得信息二值化结果,其中,所述信息二值化器包括划分信息二值化器、预测模式二值化器和标志位二值化器等二值化器,所述待编码信息包括划分信息、预测模式信息和标志位信息等信息,进一步地,分别将互相对应的每一所述系数二值化结果和每一所述信息二值化结果进行合并,获得各所述待

编码序列,进一步地,当所述缓存存储器不为饱和状态时,将各所述待编码序列存储至所述缓存存储器,所述饱和状态为所述缓存存储器无法接收所述待编码序列的状态,以供通过所述熵编码引擎模块读取所述缓存存储器的各所述待编码序列,通过使用所述缓存存储器进行数据交换,使得通过所述二值化模块发送各所述待编码序列和所述熵编码引擎模块读取各所述待编码序列的请求都能够被立即响应,进而缩短了所述二值化模块和所述熵编码引擎模块之间相互等待的时间,例如,通过所述划分信息二值化器对所述待熵编码图像进行划分,得到划分信息,进而将所述划分信息进行二值化,获得划分二值化结果,进一步地,通过所述预测模式二值化器对所述待熵编码图像进行帧内预测和帧间预测,获得所述预测信息,其中所述预测信息包括大小信息、方向信息和运动矢量等信息,进而对所述预测信息进行二值化,获得预测二值化结果,其中,所述帧内预测为通过调用率失真优化接口对所述待熵编码图像计算率失真代价获得率失真代价最小对应的方向信息等信息的处理方式,所述帧间预测为对所述待熵编码图像进行运动估计获得运动矢量等信息的处理方式,进而通过所述标志位二值化器对所述待熵编码图像的标志位信息进行二值化处理,获得标志二值化结果,其中,所述标志位信息包括记录所述待熵编码图像的序列头信息和帧头信息等标志位信息,进一步地,将所述系数二值化结果、所述划分二值化结果、所述预测二值化结果和所述标志二值化结果进行合并,即可获得所述待编码序列。

[0057]

另外地,在现有技术中,二值化过程和编码过程通常封装为一个模块,其中,二值化过程和编码过程一对一的直接串行连接,进而通常需等待通过所述二值化过程对所述语法元素进行二值化处理后得到待编码序列之后,才能通过所述编码过程对所述待编码序列进行熵编码处理,进而假设在现有技术基础之上,即使设置多个所述二值化过程分别对所述语法元素进行二值化处理,由于所述编码过程在同一时间内只能对一个待编码序列进行熵编码,当所述编码过程正在被占用执行时,所述二值化过程需要暂停等待所述编码过程完成,而当所述编码过程执行完毕后,又需要等到所述二值化过程完成二值化得到二值化的输出后才能继续进行下一编码过程,所以,即使设置多个所述二值化过程,依然存在所述二值化过程与所述编码过程互相等待的问题,无法提高整体的视频编码效率。

[0058]

而本技术实施例中由于在所述二值化模块和所述熵编码引擎模块之间增加了所述缓存存储器,使得所述二值化模块与所述熵编码引擎模块互相分离,所述二值化过程与所述编码过程不会互相等待,也即可在所述二值化模块设置多个系数二值化器并行运行,可提高二值化过程的效率,使得所述缓存存储器中始终存在所述二值化模块的输出结果,进而所述熵编码引擎模块可不间断的从所述缓存存储器中提取所述待编码序列作为输入,使得所述熵编码引擎模块不会处于空闲等待状态,进而使得所述熵编码引擎模块始终处于最大工作效率的工作状态,所以,提升了整体的视频编码效率。

[0059]

其中,所述熵编码器至少包括一所述二值化模块和一所述熵编码引擎模块,

[0060]

在所述将各所述待编码序列存储至所述缓存存储器的步骤之前,所述视频数据熵编码硬件实现方法还包括:

[0061]

步骤d10,获取所述二值化模块对应的第一工作频率和所述熵编码引擎模块对应的第二工作频率;

[0062]

在本实施例中,需要说明的是,所述第一工作频率为所述二值化模块进行二值化处理输出所述待编码序列的频率,所述第二工作频率为所述熵编码引擎模块进行熵编码生

成目标码流的频率。

[0063]

获取所述二值化模块对应的第一工作频率和所述熵编码引擎模块对应的第二工作频率,具体地,将所述二值化模块的平均吞吐率作为所述第一工作频率,并将所述熵编码引擎模块的平均吞吐率作为所述第二工作频率。

[0064]

步骤d20,根据所述第一工作频率、所述第二工作频率和各所述二值化模块共同对应的内部并行规模信息和各所述熵编码引擎模块共同对应的内部并行规模信息,设置所述缓存存储器的缓存容量。

[0065]

在本实施例中,需要说明的是,所述内部并行规模信息为所述二值化模块和所述熵编码引擎模块之间并行的内部规模信息,可以为所述二值化模块对应的数量和所述熵编码引擎模块对应的数量。

[0066]

根据所述第一工作频率、所述第二工作频率和各所述二值化模块共同对应的内部并行规模信息和各所述熵编码引擎模块共同对应的内部并行规模信息,设置所述缓存存储器的缓存容量,具体地,根据各所述二值化模块的吞吐总量和各所述熵编码引擎模块的吞吐总量之间的差值,设置所述缓存存储器的缓存容量,进而使得所述缓存存储器中始终存在所述二值化模块的输出结果,进而所述熵编码引擎模块可不间断的从所述缓存存储器中提取所述待编码序列作为输入,使得所述熵编码引擎模块不会处于空闲等待状态。

[0067]

步骤s30,通过所述熵编码引擎模块读取所述缓存存储器中的各待编码序列,并对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流。

[0068]

在本实施例中,需要说明的是,所述熵编码的方式包括二进制算术编码和哈夫曼编码等编码方式,所述目标码流为将各所述待编码序列进行熵编码后生成的比特流。

[0069]

通过所述熵编码引擎模块读取所述缓存存储器中的各待编码序列,并对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流,具体地,通过所述熵编码引擎模块读取所述缓存存储器中的各待编码序列,进而匹配每一所述待编码序列对应的上下文模型,基于所述上下文模型,预测每一所述待编码序列中的各二进制符号的概率,获得每一所述待编码序列中各二进制符号对应的概率结果,进一步地,根据各二进制符号对应的上下文模型序号选择算术编码模式,进而基于各所述概率结果和每一所述待编码序列中的各二进制符号,在所述算术编码模式对应的硬件单元中对各所述待编码序列进行算术编码,生成所述待熵编码图像对应的目标码流,其中,在获得每一概率结果之后,可根据对应的二进制符号,将所述上下文模型进行更新,以超前更新所述上下文模型,提高硬件资源的利用率。

[0070]

进一步地,图2为本技术视频数据熵编码硬件实现方法中系数二值化器的流程示意图,其中,索引为所述寻址索引,扫描顺序查找表为所述在顺序查找表进行扫描寻址,地址为所述访问地址,变换系数存储器为所述变换块寄存器,系数为所述量化系数,二值符号串为所述待编码序列,fifo为所述缓存存储器,run、level、sign和last flag均为所述中间变量,其中,run表示当前非零系数前连续出现零的个数,level表示非零系数的绝对值,sign表示非零系数的正负值,若当前非零系数为正数,则为0,若为负数,则为1,last flag为判断当前非零系数是否为量化系数块中最后一个非零系数的标志,若当前非零系数为最后一个非零系数,则记为1,若否,则为0。

[0071]

本技术实施例提供了一种视频数据熵编码硬件实现方法,相比于现有技术采用的数据依赖性强的编码处理流程的技术手段,本技术首先通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素,进而通过所述系数二值化器对所述语法元素进行二值化处理,获得各待编码序列,并将各所述待编码序列存储至所述缓存存储器,进而通过所述熵编码引擎模块读取所述缓存存储器中的各待编码序列,并对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流,进而实现了通过所述缓存存储器接收所述二值化模块发送的各待编码序列,也能通过所述熵编码引擎模块读取缓存的各待编码序列,从而降低所述二值化模块和所述熵编码引擎模块之间工作频率的差距,并行发送各所述待编码序列和读取各所述待编码序列的目的,所以,实现通过所述缓存存储器对所述待编码序列进行并行处理,缩短所述二值化模块和所述熵编码引擎模块之间相互等待时间的目的,克服了现有技术中编码数据处理过程中,数据依赖性强,相互等待时间较长,导致熵编码器的编码吞吐率较低,进而导致视频数据熵编码的效率较低的技术缺陷,从而提高了视频数据熵编码的效率。

[0072]

进一步地,参照图3,基于本技术中第一实施例,在本技术的另一实施例中,所述目标码流至少包括一所述待编码序列对应的算术编码值,所述待编码序列至少包括一二进制符号,

[0073]

所述对各所述待编码序列中的二进制符号分别进行熵编码,生成所述目标视频图像帧对应的目标码流的步骤包括:

[0074]

步骤e10,基于所述待编码序列对应的上下文模型,预测所述待编码序列中各二进制符号为预设二进制符号的概率,获得概率预测结果;

[0075]

在本实施例中,需要说明的是,所述上下文模型为用于统计概率较高的二进制符号、概率较低的二进制符号和较高概率符号的出现次数等信息的模型,所述预设二进制符号为根据所述上下文模型进行预测获得的二进制符号,所述概率预测结果为根据上下文模型对各二进制符号进行预测概率的结果。

[0076]

基于所述待编码序列对应的上下文模型,预测所述待编码序列中各二进制符号为预设二进制符号的概率,获得概率预测结果,具体地,通过所述熵编码引擎模块读取所述缓存存储器的待编码序列,匹配所述待编码序列的对应的上下文模型,进而基于所述待编码序列中对应的上下文模型,分别预测所述待编码序列中各二进制符号为预设二进制符号的概率,获得各所述二进制符号对应的概率预测结果。

[0077]

其中,所述概率预测结果至少包括一目标概率值,

[0078]

所述基于所述待编码序列对应的上下文模型,预测所述待编码序列中各二进制符号为预设二进制符号的概率,获得概率预测结果:

[0079]

步骤e11,提取所述待编码序列中的二进制符号;

[0080]

在本实施例中,提取所述待编码序列中的二进制符号,具体地,所述待编码序列中存在多个二进制符号,分别读取所述待编码序列中的各二进制符号。

[0081]

步骤e12,基于所述待编码序列对应的上下文模型,预测所述二进制符号为所述预设二进制符号的目标概率值;

[0082]

在本实施例中,需要说明的是,所述目标概率值为所述二进制符号对应的概率。

[0083]

基于所述待编码序列对应的上下文模型,预测所述二进制符号为所述预设二进制

符号的目标概率值,具体地,通过所述熵编码引擎模块读取所述缓存存储器的待编码序列,匹配所述待编码序列的对应的上下文模型,进而基于所述上下文模型,预测所述二进制符号为预设二进制符号的目标概率值。

[0084]

步骤e13,基于所述二进制符号,更新所述上下文模型,并返回执行所述提取所述待编码序列中的二进制符号的步骤,直至无法在所述待编码序列中提取所述二进制符号。

[0085]

在本实施例中,基于所述二进制符号,更新所述上下文模型,并返回执行所述提取所述待编码序列中的二进制符号的步骤,直至无法在所述待编码序列中提取所述二进制符号,具体地,根据所述二进制符号,对所述上下文模型进行更新,例如,所述上下文模型中概率较高的二进制符号1出现的概率为80/100,而概率较低的二进制符号0出现的概率为20/100,当读取到二进制符号为1时,进而将所述上下文模型二进制符号出现的概率进行更新,更新后二进制符号1出现的概率为81/101,进而返回执行所述提取所述待编码序列中的二进制符号的步骤,直至无法在所述待编码序列中提取到二进制符号,实现超前更新所述上下文模型,无需等待将所述将所述待编码序列进行编码后再进行更新所述上下文模型,进而提高了硬件资源的利用率。

[0086]

步骤e20,基于所述概率预测结果和各所述二进制符号,对所述述待编码序列进行算术编码,生成所述算术编码值。

[0087]

在本实施例中,基于所述概率预测结果和各所述二进制符号,对所述述待编码序列进行算术编码,生成所述算术编码值,具体地,根据所述上下文模型序号,其中,所述上下文模型序号最多为2个,最少为0个,获得上下文模型序号对应的算术编码模式,其中,所述算术编码模式包括单上下文模型、双上下文模型和无上下文模型等模式,进而基于所述概率预测结果和各所述二进制符号,在所述算术编码模式对应的编码单元中,分别对各所述二进制符号进行算术编码,例如,在使用算术编码时,初始的概率区间为0到1,根据所述待编码序列中的二进制符号和其对应的概率进行编码,更新初始化的概率区间,进而对下一个二进制符号进行编码,已更新的概率区间会进一步进行更新,直至编码完成所述待编码序列,进而生成待编码序列对应的算术编码值。

[0088]

进一步地,图4为本技术视频数据熵编码硬件实现方法中熵编码引擎模块中数据处理的流程示意图,其中,所述读fifo存储器为所述通过所述熵编码引擎模块读取所述缓存存储器中的待编码序列,上下文解析与更新为所述匹配所述待编码序列的对应的上下文模型并更新所述上下文模型,率失真优化量化为所述率失真优化接口,图5为本技术视频数据熵编码硬件实现方法中视频数据熵编码硬件实现设备的内部结构示意图,其中,所述语法元素二值化器为所述系数二值化器,fifo存储器为所述缓存存储器,统一熵编码引擎为所述熵编码引擎模块,变换系数为所述将所述待熵编码图像进行系数变换处理和量化处理的过程,划分信息为所述对所述待熵编码图像进行图像分割的信息,预测模式为所述对所述待熵编码图像进行帧内预测或者帧间预测获得预测信息的模式,其他标志位为所述目标视频图像帧的序列头信息、帧头信息等标志位,上下文建模为所述匹配所述待编码序列对应的上下文模型,二进制算术编码为所述各所述待编码序列中的二进制符号分别进行熵编码。

[0089]

本技术实施例提供了一种算术编码的方法,也即,基于所述待编码序列对应的上下文模型,预测所述待编码序列中各二进制符号为预设二进制符号的概率,获得概率预测

结果,进而基于所述概率预测结果和各所述二进制符号,对所述述待编码序列进行算术编码,生成所述算术编码值,实现了无需等到在编码处理单元中对所述二进制符号进行编码完成后才更新所述上下文模型,超前更新所述上下文模型的目的,进而提高了硬件处理单元的利用率。

[0090]

参照图6,图6是本技术实施例方案涉及的硬件运行环境的设备结构示意图。

[0091]

如图6所示,该视频数据熵编码硬件实现设备可以包括:处理器1001,例如cpu,存储器1005,通信总线1002。其中,通信总线1002用于实现处理器1001和存储器1005之间的连接通信。存储器1005可以是高速ram存储器,也可以是稳定的存储器(non

‑

volatile memory),例如磁盘存储器。存储器1005可选的还可以是独立于前述处理器1001的存储设备。

[0092]

可选地,该视频数据熵编码硬件实现设备还可以包括矩形用户接口、网络接口、摄像头、rf(radio frequency,射频)电路,传感器、音频电路、wifi模块等等。矩形用户接口可以包括显示屏(display)、输入子模块比如键盘(keyboard),可选矩形用户接口还可以包括标准的有线接口、无线接口。网络接口可选的可以包括标准的有线接口、无线接口(如wi

‑

fi接口)。

[0093]

本领域技术人员可以理解,图6中示出的视频数据熵编码硬件实现设备结构并不构成对视频数据熵编码硬件实现设备的限定,可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。

[0094]

如图6所示,作为一种计算机存储介质的存储器1005中可以包括操作系统、网络通信模块以及视频编码程序。操作系统是管理和控制视频数据熵编码硬件实现设备硬件和软件资源的程序,支持视频编码程序以及其它软件和/或,程序的运行。网络通信模块用于实现存储器1005内部各组件之间的通信,以及与编码系统中其它硬件和软件之间通信。

[0095]

在图6所示的视频数据熵编码硬件实现设备中,处理器1001用于执行存储器1005中存储的视频编码程序,实现上述任一项所述的视频数据熵编码硬件实现方法的步骤。

[0096]

本技术视频数据熵编码硬件实现设备具体实施方式与上述视频数据熵编码硬件实现方法各实施例基本相同,在此不再赘述。

[0097]

本技术实施例还提供一种视频数据熵编码硬件实现装置,所述视频数据熵编码硬件实现装置应用于视频数据熵编码硬件实现设备,所述视频数据熵编码硬件实现装置包括:

[0098]

转换模块,用于通过所述二值化模块中的系数二值化器将获取的待熵编码图像对应的量化系数块转换为对应的语法元素;

[0099]

二值化处理模块,用于通过所述系数二值化器对所述语法元素进行二值化处理,获得各待编码序列,并将各所述待编码序列存储至所述缓存存储器;

[0100]

熵编码模块,用于通过所述熵编码引擎模块读取所述缓存存储器中的各待编码序列,并对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流。

[0101]

可选地,所述视频数据熵编码硬件实现装置还用于:

[0102]

获取目标视频图像帧,并对所述目标视频图像帧进行分割,获得所述目标视频图像帧对应的各待熵编码图像,并将各所述待熵编码图像并行输入各自对应的熵编码硬件单

元;

[0103]

在所述对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流的步骤之后,所述视频编码方法还包括:

[0104]

将所述目标视频图像帧对应的各目标码流分别重建为对应的待熵编码图像,并各所述待熵编码图像组合为所述目标视频图像帧。

[0105]

可选地,所述视频数据熵编码硬件实现装置还用于:

[0106]

获取目标视频图像序列,并将所述目标视频图像序列中各目标视频图像子序列并行输入各自对应的熵编码硬件单元,其中,所述目标视频图像子序列至少包括一待熵编码图像;

[0107]

在所述对各所述待编码序列中的二进制符号分别进行熵编码,生成所述待熵编码图像对应的目标码流的步骤之后,所述视频编码方法还包括:

[0108]

将所述目标视频图像序列对应的各图像子序列码流分别重建为对应的目标视频图像子序列,并各所述目标视频图像子序列组合为各所述目标视频图像序列,其中,所述图像子序列码流至少包括一所述待熵编码图像对应的目标码流。

[0109]

可选地,所述转换模块还用于:

[0110]

通过所述系数二值化器中的有限状态机生成所述待熵编码图像对应的量化系数块的寻址索引;

[0111]

基于所述寻址索引,提取变换块寄存器中的量化系数块;

[0112]

对所述量化系数块中的量化系数进行游程编码,获得所述语法元素。

[0113]

可选地,所述视频数据熵编码硬件实现装置还用于:

[0114]

获取所述二值化模块对应的第一工作频率和所述熵编码引擎模块对应的第二工作频率;

[0115]

根据所述第一工作频率、所述第二工作频率和各所述二值化模块共同对应的内部并行规模信息和各所述熵编码引擎模块共同对应的内部并行规模信息,设置所述缓存存储器的缓存容量。

[0116]

可选地,所述熵编码模块还用于:

[0117]

基于所述待编码序列对应的上下文模型,预测所述待编码序列中各二进制符号为预设二进制符号的概率,获得概率预测结果;

[0118]

基于所述概率预测结果和各所述二进制符号,对所述述待编码序列进行算术编码,生成所述算术编码值。

[0119]

可选地,所述熵编码模块还用于:

[0120]

提取所述待编码序列中的二进制符号;

[0121]

基于所述待编码序列对应的上下文模型,预测所述二进制符号为所述预设二进制符号的目标概率值;

[0122]

基于所述二进制符号,更新所述上下文模型,并返回执行所述提取所述待编码序列中的二进制符号的步骤,直至无法在所述待编码序列中提取所述二进制符号。

[0123]

本技术视频数据熵编码硬件实现装置的具体实施方式与上述视频数据熵编码硬件实现方法各实施例基本相同,在此不再赘述。

[0124]

本技术实施例提供了一种介质,所述介质为可读存储介质,且所述可读存储介质

存储有一个或者一个以上程序,所述一个或者一个以上程序还可被一个或者一个以上的处理器执行以用于实现上述任一项所述的视频数据熵编码硬件实现方法的步骤。

[0125]

本技术可读存储介质具体实施方式与上述视频数据熵编码硬件实现方法各实施例基本相同,在此不再赘述。

[0126]

本技术实施例提供了一种计算机程序产品,且所述计算机程序产品包括有一个或者一个以上计算机程序,所述一个或者一个以上计算机程序还可被一个或者一个以上的处理器执行以用于实现上述任一项所述的视频数据熵编码硬件实现方法的步骤。

[0127]

本技术计算机程序产品具体实施方式与上述视频数据熵编码硬件实现方法各实施例基本相同,在此不再赘述。

[0128]

以上仅为本技术的优选实施例,并非因此限制本技术的专利范围,凡是利用本技术说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利处理范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1