应用于量子图像传感器领域的高速低功耗读出电路

1.本发明涉及基于cmos工艺技术的量子图像传感器技术领域,特别是涉及一种基于电荷传输放大器的高速低功耗读出电路结构,具体涉及应用于量子图像传感器领域的高速低功耗读出电路。

背景技术:

2.与ccd图像传感器相比,cmos图像传感器(cis)能利用标准cmos器件工艺平台,具有工艺兼容性,这为cis的发展提供了巨大的工艺和成本优势。随着微电子工艺技术的发展,器件特征尺寸越来越小,从而使cis的像素单元尺寸小型化成为可能,这有利于提高cis的像素填充因子。对于亚衍射极限(sub

‑

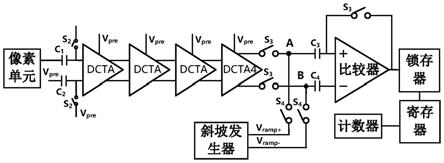

diffraction

‑

limit,sdl)像素cis,由于其像素单元尺寸远小于图像传感器镜头的衍射极限,因此能降低图像传感器的制造成本,是cis未来的发展趋势。但是,随着像素单元尺寸变小,其相应的曝光面积和满阱容量也会减小,这会降低cis的信噪比和动态范围,从而导致图像质量下降。为解决这一难题,基于单光子计数的量子图像传感器(quanta image sensors,qis)被提出。对于单光子计数图像传感器,为获得高信噪比,读出电路及信号放大很关键。单光子计数图像传感器读出电路结构如图1所示,主要由预放大电路和多比特adc等构成。预放大电路和多比特adc负责对光电子信号进行放大和量化,是qis读出电路的重要组成部分。

3.基于电荷转换原理的电荷传输放大器(charge transfer amplifier,cta)由于能够对较小的光电子信号进行放大,且具有低输入失调、高速及低功耗等优点,因此能用于qis预放大电路。cta主要有单端型和差分型两种结构,相对于单端型cta,差分型cta(dcta)输入失调更低。dcta能通过源极跟随器的电压转换和电容的充放电技术将输入电压的跳变值进行差分型放大。目前对qis读出电路的研究仍处于初步探索阶段。

4.qis的工作方式是通过多比特模数转换器(adc)以较高的速度对光电子信号进行读出,然后再对所读出的数据进行累加。目前具有高速的多比特adc是qis读出电路面临的主要挑战。由于预放大有利于qis获得高信噪比、高速低功耗多比特adc有利于qis实现时间过采样,因此,预放大和高速读出电路逐渐成为qis领域的关键课题。

技术实现要素:

5.为克服现有技术的不足,针对qis读出电路需具有单光子计数能力和时间过采样的要求,本发明旨在采用对像素信号差分放大以及双向斜坡快速比较的方法,提出一种基于dcta的新型读出电路结构。在保证读出电路面积小、结构简单的前提下,把光电子信号进行差分放大,同时显著提高单斜模数转换器(ss adc)的转换速度,并降低了读出电路的功耗。为此,本发明采取的技术方案是,应用于量子图像传感器领域的高速低功耗读出电路,由四个级联的dcta、斜坡发生器、比较器、锁存器、寄存器和计数器构成,四个级联dcta的两个输入端均通过开关s2与预充电电压v

pre

连接,同时分别与电容c1和c2的下极板连接,电容c1的上极板与像素单元的输出端连接,电容c2的上极板与预充电电压v

pre

连接,第四个dcta

的两个输出端通过开关s3分别与耦合电容c3和c4的上极板连接,耦合电容c3上极板处为dcta的放大节点a,耦合电容c4的上极板处为dcta的放大节点b;同时,a节点由开关s4与斜坡发生器的正向输出端连接,b节点由开关s4与斜坡发生器的反向输出端连接,耦合电容c3和c4的下极板分别与比较器的正输入端和负输入端连接,比较器的正输入端经开关s3与比较器的输出端连接,所述比较器的输出端还与锁存器的输入端连接,锁存器和计数器的输出端均与寄存器连接。

6.dcta电路主要由pmos管mp1和mp2、nmos管mn1和mn2、开关s1和s2、传输电容c

t1

和c

t2

、负载电容c

load

构成,mp1的源极经开关

‑

s1与电容c

t1

的上极板连接,同时电容c

t1

的上极板经开关s1与电源vdd连接,mp1和mn1的栅极均连接到dcta的输入节点in1,mp1和mn1的漏极均通过开关s2与预充电电压v

pre

连接,并经负载电容接地,mn1的源极经开关

‑

s1与电容c

t2

的上极板连接,电容c

t2

的上极板经开关s1接地,由于dcta是差分结构,mn2和mp2与开关s1和s2、电容c

t1

和c

t2

以及c

load

的连接方法和上述mn1和mp1的连接方法相同。

7.第四个dcta的负载电容是比较器输入端的耦合电容。

8.工作过程可以分为四个阶段:

9.阶段(1):开关s1、s3接通,s2断开,dcta和比较器均处于复位状态;

10.阶段(2):开关s1断开,s2接通,dcta进入预充电阶段,输出节点a和b的电压均保持在预充电电压v

pre

;

11.阶段(3):开关s1、s2同时断开,此时像素单元产生的光电子信号经过级联的dcta进行放大,使节点a的电压从预充电电压上升,节点b的电压从预充电电压下降,完成对像素信号的预放大过程;

12.阶段(4):开关s3断开,s1、s4接通,dcta的放大阶段和比较器的复位阶段结束,同时放大节点a和b分别接入反向斜坡和正向斜坡,比较器进入比较阶段,完成翻转,计数器输出电压信号对应的数字码值。

13.本发明的特点及有益效果是:

14.本发明提出了一种应用于qis领域的新型读出电路结构,通过将比较器输入端的耦合电容作为dcta的负载电容,实现了对光电子信号的低噪声放大;通过将两个相反方向的斜坡信号同时接入dcta的输出节点,使比较器翻转所需要的时间减小为原来的一半,大大提高了adc的转换速度,同时降低了读出电路的功耗。

附图说明:

15.图1qis读出电路的结构简图。

16.图2基于dcta的新型读出电路结构图。

17.图3dcta的电路结构图。

18.图4基于dcta的新型读出电路的时序简图。

19.图5双向斜坡adc与传统单斜adc在时间上相比较的变化示意图。

具体实施方式

20.本发明所述的一种应用于qis领域的高速低功耗读出电路,其电路结构如图2所示。与传统ss adc相比,本设计增加了4个级联的dcta对光电子信号进行差分型放大;其中

第四个dcta(dcta4)与前三个dcta的区别在于:dcta4以比较器输入端的两个耦合电容作为自身的负载电容。级联的dcta将光电子信号进行放大,在dcta的放大阶段和比较器的复位阶段同时结束时,根据电容充放电的原理,放大节点a的电压将由预充电电压v

pre

增大到v

pre

+v

sig

/2,放大节点b将由预充电电压降低为v

pre

‑

v

sig

/2。与传统斜坡相比,本设计在dcta的放大阶段完成后,将同一个斜坡所产生的两个相反方向的斜坡分别接入节点a和b,直至比较器翻转。双向斜坡同时接入比较器的方法使adc在转换阶段能更快地完成,并能同时降低读出电路的功耗。假定v

ramph

是斜坡信号的最大值,该过程将实现对v

ramph

‑

v

sig

信号的量化,随后通过对计数器中的每一个计数单元进行取反操作,实现对v

sig

信号的量化。

21.本发明所设计的一种应用于qis的高速、低功耗读出电路结构如图2所示:核心电路由四个级联的dcta、斜坡发生器、比较器、锁存器、寄存器和计数器构成。四个级联dcta的两个输入端均通过开关s2与预充电电压v

pre

连接,同时分别与电容c1和c2的下极板连接。电容c1的上极板与像素单元的输出端连接,电容c2的上极板与预充电电压v

pre

连接。dcta4的两个输出端通过开关s3分别与耦合电容c3和c4的上极板连接(即dcta的放大节点a和b);同时,a节点由开关s4与斜坡发生器的正向输出端连接,b节点由开关s4与斜坡发生器的反向输出端连接。耦合电容c3和c4的下极板分别与比较器的正输入端和负输入端连接。比较器的正输入端经开关s3与比较器的输出端连接,所述比较器的输出端还与锁存器的输入端连接,锁存器和计数器的输出端均与寄存器连接。

22.本发明核心电路中的dcta详细原理图如图3所示。dcta电路主要由pmos管(mp1和mp2)、nmos管(mn1和mn2)、开关(s1和s2)、传输电容(c

t1

和c

t2

)和负载电容c

load

构成。mp1的源极经开关

‑

s1与电容c

t1

的上极板连接,同时电容c

t1

的上极板经开关s1与电源vdd连接。mp1和mn1的栅极均连接到dcta的输入节点in1,mp1和mn1的漏极均通过开关s2与预充电电压v

pre

连接,并经负载电容接地。mn1的源极经开关

‑

s1与电容c

t2

的上极板连接,电容c

t2

的上极板经开关s1接地。由于dcta是差分结构,mn2和mp2与开关s1和s2、电容c

t1

和c

t2

以及c

load

的连接方法和上述mn1和mp1的连接方法相同。

23.本发明通过在比较器处于复位阶段时,将其输入端的耦合电容作为dcta负载电容的方法,提出了一种新型读出电路结构。与现有的qis读出电路相比,本发明在新型读出电路结构的基础上,通过两个方向相反的斜坡同时接入比较器(即dcta差分输出节点),使adc的转换时间缩短为原来的一半。在斜坡的斜率相同的条件下,双向斜坡量化的速度比传统单斜坡的量化速度提升了一倍,大大提高了adc的转换速度。同时在dcta仅消耗很小一部分动态功耗的前提下,转换时间的缩短使整个读出电路的功耗大大降低,实现了一种应用于qis的高速、低功耗读出电路。

24.由上述技术方案可知,在图2中前三个dcta的结构均如图3所示,与前三个dcta不同的是,第四个dcta(dcta4)的负载电容是比较器输入端的耦合电容。因此,在dcta的放大阶段,放大节点a和b将从预充电电压v

pre

分别升高和下降,下一阶段双向斜坡分别接入节点a和b,使adc快速量化出v

ramph

‑

v

sig

的值。在计数器的值保存到寄存器之前,将计数器的每一个计数单元取反,使adc量化的电压信号为v

sig

。

25.图4为基于dcta的高速低功耗读出电路的时序图,图5为本发明与传统单斜adc在时间上相比较的变化示意图。由于dcta的放大节点与比较器的输入端相连接,并且同一个斜坡发生器可以同时产生两个相反方向的斜坡,因此本发明专利能够在面积小、结构简单

的条件下,实现对光电子信号的预放大,提高读出电路的速度,降低读出电路的功耗。本发明中电路的工作过程可以分为四个阶段:

26.阶段(1):开关s1、s3接通,s2断开,dcta和比较器均处于复位状态。

27.阶段(2):开关s1断开,s2接通,dcta进入预充电阶段,输出节点a和b的电压均保持在预充电电压v

pre

。

28.阶段(3):开关s1、s2同时断开,此时像素单元产生的光电子信号经过级联的dcta进行放大,使节点a的电压从预充电电压上升,节点b的电压从预充电电压下降,完成对像素信号的预放大过程。

29.阶段(4):开关s3断开,s1、s4接通,dcta的放大阶段和比较器的复位阶段结束,同时放大节点a和b分别接入反向斜坡和正向斜坡,比较器进入比较阶段,完成翻转,计数器输出电压信号对应的数字码值。

30.以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明披露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1