一种适用于DLMS/COSEM通信协议的加解密模块和抄表系统的制作方法

一种适用于dlms/cosem通信协议的加解密模块和抄表系统

技术领域

1.本发明属于电力领域,尤其涉及一种适用于dlms/cosem通信协议的加解密模块和抄表系统。

背景技术:

2.dlms/cosem(dlms:device language message specification,设备语言报文规范,cosem:companion specification for energy metering,能源计量配套规范)通信协议是国际电工委员会为解决自动抄表系统和计量系统中的数据采集,仪表安装、维护,系统集成等问题提出的新的电能表通信标准。它以良好的系统互连性和互操作性成为迄今为止较为完善的电表通信协议标准。

3.为了安全,一般在通信中数据都会进行加密处理,在实际应用中,会根据安全级别的不同,会对数据进行不同级别的安全加密。电能表在获取数据时,需要对数据进行解密才能使用,同样,电能表返回给抄读设备的数据,也需要先进行加密处理,再通过通信通道传输给抄读设备。

4.如图1所示,在现有的抄表系统设计中,抄读设备发出来的加密数据(密文)通过通信接口电路进行物理层转换之后,进入到电能表的主控芯片(mcu,microcontroller unit)。在电能表主控芯片中固件程序通过调用加解密函数来对数据进行解密,固件程序对解密的数据进行相应的处理之后返回数据,同样,固件程序调用加解密函数对数据进行加密,再通过通信接口将密文返回给抄读设备。抄读设备中的处理方式与电能表部分相同。

5.如上所述,在现有系统设计中,数据的加解密模块在设计中并未独立出来,而是集成在应用软件中,由软件开发人员开发和维护,这样的设计思路显然存在安全隐患。

技术实现要素:

6.发明目的:本发明所要解决的技术问题是针对现有技术的不足,提供一种适用于dlms/cosem通信协议的加解密模块和抄表系统。

7.为了解决上述技术问题,第一方面,公开了一种适用于dlms/cosem通信协议的加解密模块,应用于抄表系统中的电能表和抄读设备,包括加解密主控芯片、加解密接口电路、加解密电源电路和运行指示灯,

8.所述加解密主控芯片是所述加解密模块的核心器件,用于完成数据的加解密运算;

9.所述加解密接口电路,用于加解密模块与外部模块进行数据及信号交互,所述外部模块指电能表和抄读设备中除加解密模块以外的模块;

10.所述加解密电源电路,用于将加解密接口电路输入的电源电平转换成加解密模块需要的电平;

11.所述运行指示灯,用于显示加解密模块的运行状态。

12.结合第一方面,可选地,所述加解密接口电路的管脚包括输入输出管脚vdd、模拟

与数字地管脚gnd、输入管脚mosi(master output slave input,主设备数据输出,从设备数据输入)、输出管脚miso(master input slave output,主设备数据输入,从设备数据输出)、输入管脚sclk(serial clock,串行时钟)、输入管脚cs(chip select,片选)、输出管脚sta(state,状态)和输入管脚rst(reset,复位),

13.所述输入输出管脚vdd,用于加解密模块电源输入;

14.所述模拟与数字地管脚gnd,用于加解密模块接地,与电能表地或者抄读设备地相连;

15.所述输入管脚mosi是标准串行接口,用于加解密模块数据输入;所述标准串行接口包括spi、uart(universal asynchronous receiver/transmitter,异步收发传输器)和iic(inter-integrated circuit,集成电路总线)中的任一种;

16.所述输出管脚miso是标准串行接口,用于加解密模块数据输出;

17.所述输入管脚sclk是标准串行接口,用于时钟输入;

18.所述输入管脚cs是标准串行接口,用于输入片选信号;

19.所述输出管脚sta,用于加解密模块的运行状态指示,如果输出高电平表示加解密模块工作异常或者正在加解密,电能表主控芯片或者抄读设备主控芯片不要对加解密模块进行读写操作;如果输出低电平表示加解密模块处于待机状态;

20.所述输入管脚rst,用于加解密模块复位控制输入。

21.结合第一方面,可选地,所述运行指示灯状态和加解密模块的运行状态之间的关系包括:

22.运行指示灯常亮:加解密模块电源正常,加解密主控芯片正常供电;

23.运行指示灯亮0.5秒,灭0.5秒,周期性闪烁:加解密模块处于正常运行状态;

24.运行指示灯亮0.2秒,灭0.2秒,周期性快速闪烁:加解密模块处于通信及加解密运行状态;

25.运行指示灯亮1秒,灭1秒,周期性慢速闪烁:加解密模块处于异常工作状态,所述异常工作状态包括程序自检异常和通信长时间错。

26.结合第一方面,可选地,所述加解密接口电路还是加解密模块与外部模块电路板的安装或焊接接口,接口形式对应为接插件接口或者贴片焊接口。

27.结合第一方面,可选地,出于功能考虑,所述加解密主控芯片需要选用计算能力比较强的mcu。考虑到成本,加解密主控芯片的尺寸不宜太大,管脚不需要太多,所述加解密主控芯片的参数要求如下:

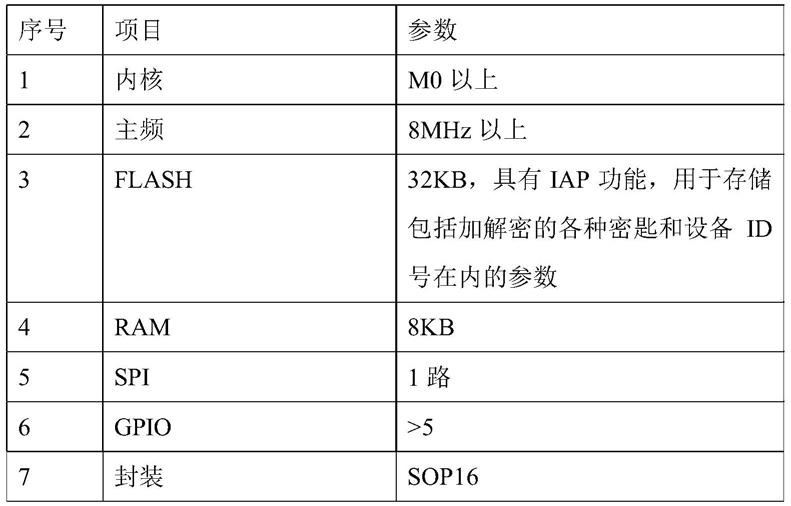

28.内核:m0以上;主频:8mhz以上;flash:32kb,具有iap(in application programming,应用编程)功能,用于存储参数;ram(random access memory,随机存取存储器):8kb;spi(serial peripheral interface,串行外设接口):1路;gpio(general-purpose input/output,通用型之输入输出):大于5个;封装:sop16(small out-line package 16,小外形封装16)。

29.结合第一方面,可选地,所述运行指示灯采用贴片式的发光二极管,即led(light-emitting diode)灯,颜色选用绿色。

30.第二方面,公开了一种适用于dlms/cosem通信协议的抄表系统,包括电能表和抄读设备,电能表包括电能表主控芯片和电能表加解密模块,抄读设备包括抄读设备主控芯

片和抄读设备加解密模块,所述电能表加解密模块和抄读设备加解密模块相同,为上述的加解密模块,电能表主控芯片和抄读设备主控芯片统称为第一主控芯片;

31.电能表的数据加解密处理方式包括:

32.抄读设备发出来的加密数据通过通信接口电路进行物理层转换之后,进入到电能表主控芯片;电能表主控芯片将加密数据发送给电能表加解密模块,电能表加解密模块对数据进行解密,将解密好的数据回传给电能表主控芯片;电能表主控芯片根据明文完成dlms/cosem协议处理,再将需要加密的数据发送给电能表加解密模块;电能表加解密模块对数据进行加密处理,将加密后的密文返回给电能表主控芯片;电能表主控芯片再通过通信接口将密文返回给抄读设备;

33.抄读设备的数据加解密处理方式与电能表的数据加解密处理方式相同。

34.结合第二方面,可选地,加解密模块工作流程包括:

35.步骤1,加解密模块上电之后输出管脚sta输出高电平,运行指示灯常亮,进行自检;如果自检异常,运行指示灯周期性慢速闪烁;如果自检正常,执行步骤2;

36.步骤2,加解密模块自检初始化完毕,输出管脚sta输出低电平,运行指示灯周期性闪烁,处于待机状态;

37.步骤3,第一主控芯片侦测到输出管脚sta为低电平,向加解密模块发送数据,进行操作;所述操作包括加密、解密和读写;

38.步骤4,加解密模块根据加解密模块与第一主控芯片之间的通信协议解析接收到的数据,若为加解密操作,执行步骤5,若为读操作,执行步骤6;

39.步骤5,加解密操作:第一主控芯片将需要加解密的数据发给加解密模块,加解密模块根据加解密类型进行加解密操作,在加解密过程中,输出管脚sta输出高电平;加解密结束后,输出管脚sta输出低电平;第一主控芯片通过判断输出管脚sta的状态是否由低电平变为高电平来判断加解密模块是否收到正确数据并开始进行加解密操作;

40.步骤6,读操作:主控芯片读取到输出管脚sta从高电平变为低电平,发送读取命令来读取加解密的结果。

41.结合第二方面,可选地,为了规范本发明的模块与电能表或者抄录设备主控芯片之间的数据交互,加解密模块和第一主控芯片之间的通信协议包括物理层和协议层,所述物理层通过加解密接口电路的输入管脚mosi和输出管脚miso进行数据输入输出,加解密模块为从机,第一主控芯片为主机;

42.所述协议层包括主机发给从机的通信帧和从机返回给主机的通信帧,主机发给从机的通信帧依次包括帧头、长度len、命令ctr、类型type、主机发送帧数据date1、校验位crc和帧尾字段,

43.从机返回给主机的通信帧依次包括帧头、长度len、标识flg、从机回应帧数据date2、校验位crc和帧尾字段。

44.结合第二方面,可选地,所述帧头和帧尾用于标识完整的一个通信帧,

45.所述长度len为一个通信帧中不包括帧头和帧尾的总长度,长度len是一个字节,一个通信帧的总长度不能超过256个字节,否则请分两次做发送;

46.所述命令ctr,用于主机向从机发送操作命令;

47.所述类型type,用于根据命令ctr的取值,设置不同操作命令对应的操作类型;

48.所述主机发送帧数据date1,用于根据命令ctr的取值,向从机发送不同操作命令对应的数据;

49.所述标识flg,用于标识从机读取数据的有效性;

50.所述从机回应帧数据date2,用于根据标识flg,从机返回给主机的数据;

51.所述校验位crc,采用crc(cyclic redundancy check,循环冗余校验)校验,用于校验一个通信帧中除帧头、帧尾和校验位自身之外所有数据。

52.有益效果:

53.1、本技术提供的抄表系统中的电能表和抄读设备将加密算法与业务程序分开,使用单独的加解密模块,使得加密算法运行在独立的mcu中,加密更加安全可靠。

54.2、密匙存贮在加解密模块中,有效防止密匙被盗取。

55.3、加解密模块集成dlms/cosem通信中各种加密算法,系统开发人员不必再去开发,减轻开发人员的负担,加快产品开发周期。

附图说明

56.下面结合附图和具体实施方式对本发明做更进一步的具体说明,本发明的上述和/或其他方面的优点将会变得更加清楚。

57.图1为现有技术抄表系统结构示意图。

58.图2为本技术实施例提供的一种适用于dlms/cosem通信协议的抄表系统结构示意图。

59.图3为本技术实施例提供的一种适用于dlms/cosem通信协议的加解密模块结构示意图。

60.图4为本技术实施例提供的加解密模块的接口电路管脚示意图。

61.图5为本技术实施例提供的一种适用于dlms/cosem通信协议的抄表系统工作流程示意图。

具体实施方式

62.下面将结合附图,对本发明的实施例进行描述。

63.本技术第一实施例公开一种适用于dlms/cosem通信协议的加解密模块,应用于抄表系统中的电能表和抄读设备,如图3所示,包括加解密主控芯片、加解密接口电路、加解密电源电路和运行指示灯1,

64.所述加解密主控芯片是所述加解密模块的核心器件,用于完成数据的加解密运算;

65.所述加解密接口电路,用于加解密模块与外部模块进行数据及信号交互,所述外部模块指电能表和抄读设备中除加解密模块以外的模块;

66.所述加解密电源电路,用于将加解密接口电路输入的电源电平转换成加解密模块需要的电平;

67.所述运行指示灯1,用于显示加解密模块的运行状态。

68.所述加解密主控芯片的参数要求如表1所示:

69.表1

[0070][0071]

所述加解密接口电路的管脚包括输入输出管脚vdd、模拟与数字地管脚gnd、输入管脚mosi、输出管脚miso、输入管脚sclk、输入管脚cs、输出管脚sta和输入管脚rst,管脚定义如图4和表2所示,

[0072]

表2

[0073][0074]

[0075]

上表中,i:输入管脚;o:输出管脚;p:电源管脚;g:模拟与数字地。

[0076]

所述运行指示灯1状态和加解密模块的运行状态之间的关系如表3所示:

[0077]

表3

[0078][0079]

所述运行指示灯1采用贴片式的发光二极管,即led灯,颜色选用绿色。

[0080]

所述加解密接口电路还是加解密模块与外部模块电路板的安装或焊接接口,接口形式对应为接插件接口或者贴片焊接口。接插件接口可以是单排插针或双排插针等,贴片焊接口可以是邮票孔等形式的。

[0081]

本技术第二实施例公开一种适用于dlms/cosem通信协议的抄表系统,如图2所示,包括电能表和抄读设备,电能表包括电能表主控芯片和电能表加解密模块,抄读设备包括抄读设备主控芯片和抄读设备加解密模块,所述电能表加解密模块和抄读设备加解密模块相同,为上述的加解密模块,电能表主控芯片和抄读设备主控芯片统称为第一主控芯片;

[0082]

电能表的数据加解密处理方式包括:

[0083]

抄读设备发出来的加密数据通过通信接口电路进行物理层转换之后,进入到电能表主控芯片;电能表主控芯片将加密数据发送给电能表加解密模块,电能表加解密模块对数据进行解密,将解密好的数据回传给电能表主控芯片;电能表主控芯片根据明文完成dlms/cosem协议处理,再将需要加密的数据发送给电能表加解密模块;电能表加解密模块对数据进行加密处理,将加密后的密文返回给电能表主控芯片;电能表主控芯片再通过通信接口将密文返回给抄读设备;

[0084]

抄读设备的数据加解密处理方式与电能表的数据加解密处理方式相同。

[0085]

如图5所示,加解密模块工作流程包括:

[0086]

步骤1,加解密模块上电之后输出管脚sta输出高电平,运行指示灯1常亮,进行自检;如果自检异常,运行指示灯1周期性慢速闪烁;如果自检正常,执行步骤2;

[0087]

步骤2,加解密模块自检初始化完毕,输出管脚sta输出低电平,运行指示灯1周期性闪烁,处于待机状态;

[0088]

步骤3,第一主控芯片侦测到输出管脚sta为低电平,向加解密模块发送数据,进行操作;所述操作包括加密、解密和读写;

[0089]

步骤4,加解密模块根据加解密模块与第一主控芯片之间的通信协议解析接收到

的数据,若为加解密操作,执行步骤5,若为读操作,执行步骤6;

[0090]

步骤5,加解密操作:第一主控芯片将需要加解密的数据发给加解密模块,加解密模块根据加解密类型进行加解密操作,在加解密过程中,输出管脚sta输出高电平;加解密结束后,输出管脚sta输出低电平;第一主控芯片通过判断输出管脚sta的状态是否由低电平变为高电平来判断加解密模块是否收到正确数据并开始进行加解密操作;

[0091]

步骤6,读操作:主控芯片读取到输出管脚sta从高电平变为低电平,发送读取命令来读取加解密的结果。

[0092]

加解密模块和第一主控芯片之间的通信协议包括物理层和协议层,所述物理层通过加解密接口电路的输入管脚mosi和输出管脚miso进行数据输入输出,加解密模块为从机,第一主控芯片为主机;

[0093]

所述协议层包括主机发给从机的通信帧和从机返回给主机的通信帧,主机发给从机的通信帧格式如表4所示,其中n表示主机发送帧数据date1和从机回应帧数据date2的长度,n《128字节:

[0094]

表4

[0095][0096]

从机返回给主机的通信帧格式如表5所示,

[0097]

表5

[0098][0099]

所述帧头和帧尾用于标识完整的一个通信帧,本实施例中,设置为0x7e;

[0100]

所述长度len为一个通信帧中不包括帧头和帧尾的总长度,长度len是一个字节,一个通信帧的总长度不能超过256个字节,否则请分两次做发送。

[0101]

所述命令ctr,用于主机向从机发送操作命令,定义如表6所示;

[0102]

表6

[0103]

命令字符定义0x00对加解密模块进行写操作,从机无回应帧0x01对加解密模块进行读操作0x02对通信帧数据部分做加密操作,从机无回应帧0x03对通信帧数据部分做解密操作,从机无回应帧

[0104]

所述类型type,用于根据命令ctr的取值,设置不同操作命令对应的操作类型;

[0105]

当ctr为0x00时,类型字符定义如表7所示,

[0106]

表7

[0107]

类型字符定义0x00对模块进行参数写操作

[0108]

当ctr为0x01时,类型字符定义如表8所示,

[0109]

表8

[0110]

类型字符定义0x00对模块的参数进行读操作0x01对模块上次加解密数据结果进行读操作

[0111]

当ctr为0x02、0x03时,类型type表示加密类型,类型字符定义如表9所示,

[0112]

表9

[0113][0114]

所述主机发送帧数据date1,用于根据命令ctr的取值,向从机发送不同操作命令对应的数据,定义如表10所示;

[0115]

表10

[0116][0117][0118]

所述标识flg,用于标识从机读取数据的有效性,定义如表11所示;

[0119]

表11

[0120]

标识字符定义0x00读取的数据有效0x01读取的数据无效,此时date2区域没有数据。

[0121]

所述从机回应帧数据date2,用于根据标识flg,从机返回给主机的数据;

[0122]

所述校验位crc,采用crc校验,用于校验一个通信帧中除帧头、帧尾和校验位自身之外所有数据。

[0123]

本发明提供了一种适用于dlms/cosem通信协议的加解密模块和抄表系统的思路及方法,具体实现该技术方案的方法和途径很多,以上所述仅是本发明的具体实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。本实施例中未明确的各组成部分均可用现有技术加以实现。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1