一种基于波形缩减同步头的帧同步捕获方法、设备及存储介质与流程

本发明属于数字信号处理,具体是涉及一种基于波形缩减同步头的帧同步捕获方法、设备及存储介质。

背景技术:

1、短波通信以其抗摧毁能力强、灵活性高、设备简单及造价低廉等特点,成为世界各国中、远程通信的主要手段。但是,在实时的短波通信过程中由于短波信道时变特性的影响,发射时刻、时隙分配、信道时延均处于未知状态,为了保证突发通信信号的实时接收,并尽可能为后续干扰预留响应时间,快速和高精度的帧同步与符号定时估计是至关重要的,它会很大程度的影响后续信道参数估计性能。

2、现有的波形同步技术为了首要保证通信的可靠性与信道估计结果的准确性,通常会采用较长的同步头进行同步捕获,同时考虑内插探针序列的设计方式。但采用较长同步头序列在工程实际应用中可能带来一些弊端,包括等待接收完整同步头序列带来的时延、在同步头序列阶段处理较多采样点导致的计算量增加等,而这些弊端将会影响通信接收端的处理响应速度,减少预留给通信信号携带比特信息的处理时间余量。

技术实现思路

1、因为了解决现有波形帧同步捕获方法所存在信号处理时延较大、难以为后续信号处理流程预留更多处理响应时间的问题,本发明提供一种克服上述问题或者至少部分地解决上述问题的一种基于波形缩减同步头的帧同步捕获方法。

2、根据本发明的一个方面,本发明提供一种基于波形缩减同步头的帧同步捕获方法,其特征在于,

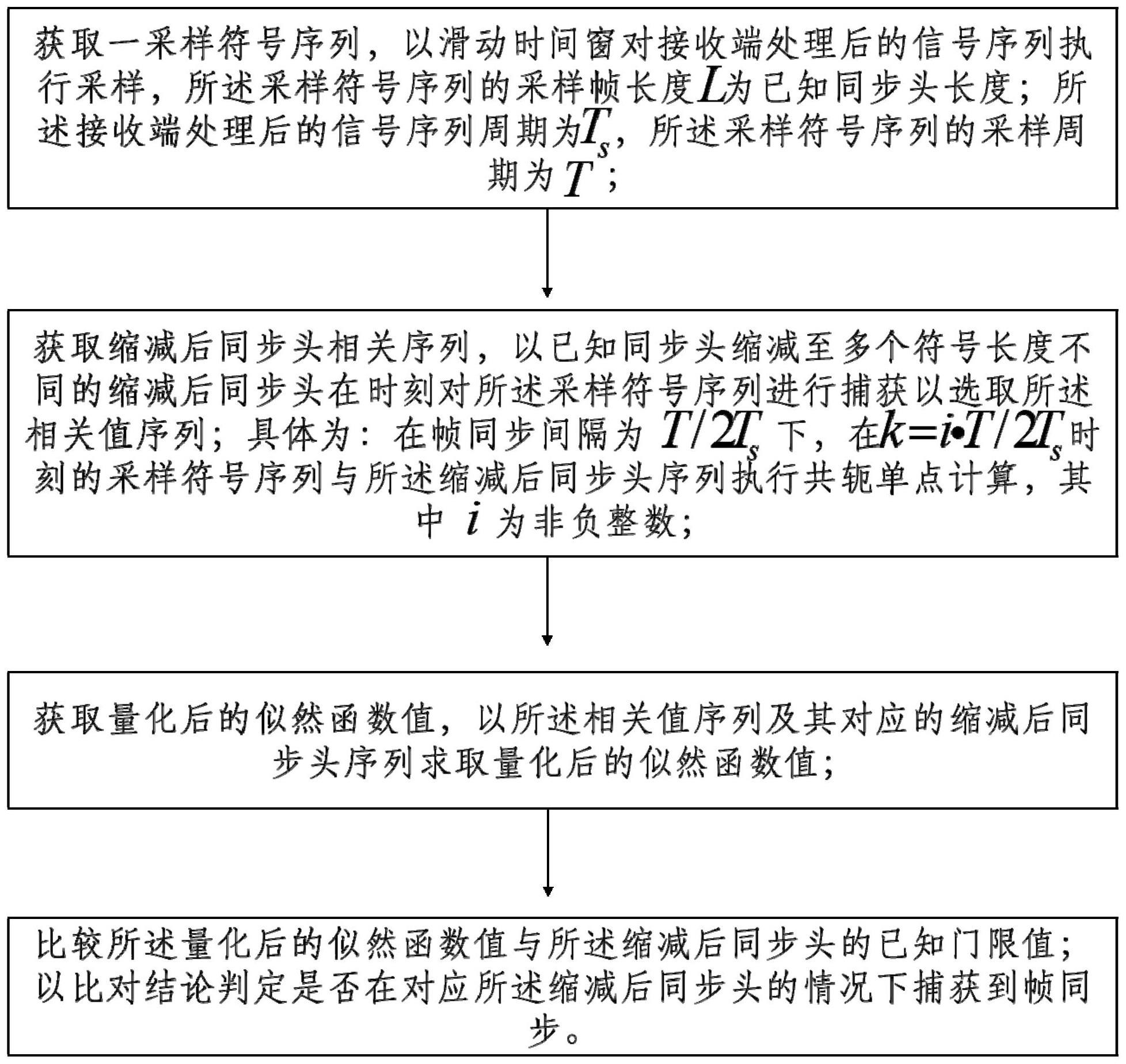

3、所述帧同步捕获方法包括如下步骤:

4、获取一采样符号序列,以滑动时间窗对接收端处理后的信号序列执行采样,所述采样符号序列的采样帧长度l为已知同步头长度;所述接收端处理后的信号序列周期为ts,所述采样符号序列的采样周期为t;

5、获取缩减后同步头相关序列,以已知同步头缩减至多个符号长度不同的缩减后同步头对所述采样符号序列进行捕获以选取所述相关值序列;具体为:在帧同步间隔为t/(2ts)下,在k=i·t(2ts)时刻的采样符号序列与所述缩减后同步头序列执行共轭单点计算,其中i为非负整数;

6、获取量化后的似然函数值,以所述相关值序列及其对应的缩减后同步头序列求取量化后的似然函数值;

7、比较所述量化后的似然函数值与所述缩减后同步头的已知门限值;以比对结论判定是否在对应所述缩减后同步头的情况下捕获到帧同步。

8、进一步地,所述缩减后同步头的已知门限值,为在所述已知同步头及已知多个缩减符号长度下,经由随机信号仿真计算后获取的对应每个缩减符号长度下的已知门限值。

9、进一步地,所述多个符号长度不同的缩减后同步头为所述已知同步头序列长度1/8的倍数或32、64的倍数。

10、进一步地,所述相关值序列的计算方法为:

11、ri(n)=y(kts)·x(n),k=i·t/(2ts),i=0,1,2,...

12、其中,x(n)表示所述已经同步头序列中的缩减后同步头序列元素,0≤n<nsln,ns为1~ns之间的整数,l=ln·ns。

13、进一步地,所述相关值序列的计算中,选取当i>2(nsln-1)时的所述相关值序列来计算所述似然函数值。

14、进一步地,

15、所述似然函数值的计算方法为:

16、

17、其中[*]表示共轭运算,其中y为所述相关值序列,xs为对应的缩减后同步头序列。

18、进一步地,对所述采样符号序列y执行频偏修正获取经过修正后的相关值序列。

19、进一步地,在确定捕获到帧同步的情况下,依据确定的帧同步位置确定下一步符号定时同步的搜索区间的起始位置。

20、本发明还公开了一种计算机设备,包括存储器和处理器,所述存储器存储有计算机程序,其特征在于,所述处理器执行所述计算机程序时实现上述方法的步骤。

21、本发明还公开了一种计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现上述方法的步骤。

22、总体而言,通过本发明构思的以上技术方案与现有技术相比,能够取得下列有益效果:

23、采用缩减同步头的捕获方式来进行帧同步捕获,能够显著减少同步头的捕获时间和计算量,从而给后续的信号计算留下足够的处理时间,以放置信号丢帧;

24、并且采用先执行同步头缩减的方式获取仿真的门限值,在信号序列采样中采用滑动时间窗执行采样,并且跟多个缩减后的同步头执行相关值的计算,从而获取是否获得帧同步捕获的结论,有效减少帧同步捕获的计算长度,减少同步头的计算时间。

技术特征:

1.一种基于波形缩减同步头的帧同步捕获方法,其特征在于,

2.根据权利要求1所述的基于波形缩减同步头的帧同步捕获方法,其特征在于,所述缩减后同步头的已知门限值,为在所述已知同步头及已知多个缩减符号长度下,经由随机信号仿真计算后获取的对应每个缩减符号长度下的已知门限值。

3.根据权利要求1所述的基于波形缩减同步头的帧同步捕获方法,其特征在于,所述多个符号长度不同的缩减后同步头为所述已知同步头序列长度1/8的倍数或32、64的倍数。

4.根据权利要求1所述的基于波形缩减同步头的帧同步捕获方法,其特征在于,所述相关值序列的计算方法为:

5.根据权利要求4所述的基于波形缩减同步头的帧同步捕获方法,其特征在于,所述相关值序列的计算中,选取当i>2(nsln-1)时的所述相关值序列来计算所述似然函数值。

6.根据权利要求5所述的基于波形缩减同步头的帧同步捕获方法,其特征在于,

7.根据权利要求6所述的基于波形缩减同步头的帧同步捕获方法,其特征在于,

8.根据权利要求1所述的基于波形缩减同步头的帧同步捕获方法,其特征在于,

9.一种计算机设备,包括存储器和处理器,所述存储器存储有计算机程序,其特征在于,所述处理器执行所述计算机程序时实现权利要求1至8中任一项所述方法的步骤。

10.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现权利要求1至8中任一项所述方法的步骤。

技术总结

本发明公开了一种基于波形缩减同步头的帧同步捕获方法、设备及存储介质,包括获取一采样符号序列,以滑动时间窗对接收端处理后的信号序列执行采样,采样符号序列的采样帧长度为已知同步头长度;获取缩减后同步头相关序列,以已知同步头缩减至多个符号长度不同的缩减后同步头对采样符号序列进行捕获以选取相关值序列;获取量化后的似然函数值,以相关值序列及其对应的缩减后同步头序列求取量化后的似然函数值;比较量化后的似然函数值与缩减后同步头的已知门限值;以比对结论判定是否在对应缩减后同步头的情况下捕获到帧同步。按照本发明的帧同步捕获方法,改善同步头捕获的时延、为后续信号处理流程预留更多处理响应时间。

技术研发人员:王纪东,李川,虞鑫,梁增毅,丁昊成,付睿,游行远,刘晓玲

受保护的技术使用者:武汉船舶通信研究所(中国船舶重工集团公司第七二二研究所)

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!