一种基于BLVDS总线数据通信的降功耗通信的电路的制作方法

一种基于blvds总线数据通信的降功耗通信的电路

技术领域

1.本实用新型涉及一种基于blvds总线数据通信的降功耗通信的电路,属于数据通信技术领域。

背景技术:

2.blvds总线作为一种高速差分总线,往往应用在工业数据通信领域。blvds总线发送端将数据发送至数据总线,接收端解析数据,以此达到数据通信的目的。为了保证通信的实时性,通信的双方要不停进行数据查询和通信。由于这种不停地查询通信,造成了整个装能耗的增加。

3.blvds总线数据通信是双向的,主板和从板通过blvds总线进行数据通信时,为了保证数据的实时性,要不间断的进行数据交互,但数据从发送到对侧接收,再到数据有效往往需要一定的时间,在这段时间进行数据交互是没有意义的,既占用了blvds总线的带宽,也增加了整个装置的能耗。

技术实现要素:

4.本实用新型的目的在于克服现有技术中的不足,提出了一种基于blvds总线数据通信的降功耗通信的电路,能够节省blvds总线带宽,减少了在blvds总线上的无效查询,降低整个装置的能耗。

5.为达到上述目的,本实用新型提供了一种基于blvds总线数据通信的降功耗通信的电路,包括:两块插件、blvds总线和数据状态线;

6.所述插件包括fpga、blvds芯片和mosfet管,所述mosfet管的一端连接fpga,所述mosfet管的另一端连接数据状态线,通过调节数据状态线的电平状态输出本侧fpga的数据状态;所述fpga连接数据状态线获取对侧fpga的数据状态;

7.所述fpga连接blvds芯片,blvds芯片之间通过blvds总线进行数据通信。

8.进一步地,所述blvds总线包括背板差分线p和背板差分线n,所述背板差分线p和背板差分线n的两端分别通过1块100ω的终端电阻进行连接。

9.进一步地,所述blvds芯片包括用于传输模拟信号的a管脚和b管脚,所述a管脚连接背板差分线p,所述b管脚连接背板差分线n。

10.进一步地,所述blvds芯片包括用于传输数字信号的r管脚、de管脚和d管脚,所述r管脚、de管脚和d管脚连接所述fpga。

11.进一步地,所述fpga包括输出端口do2、输出端口do3和输入端口di1,所述输出端口do2连接blvds芯片的de管脚用于确定数据传输方向,所述输出端口do3连接blvds芯片的d管脚用于输出fpga的数据至blvds芯片,所述输入端口di1连接blvds芯片的r管脚用于接收blvds芯片输出的数据。

12.优选地,所述de管脚确定的数据传输方向包括方向1和方向0;所述方向1为通过fpga输出端口do3输出fpga的数据至blvds芯片d管脚,通过blvds芯片传输数据至blvds总

线;所述方向0为总线传输数据至blvds芯片,通过blvds芯片的r管脚将数据传输至fpga输入端口di1。

13.进一步地,所述数据状态线通过一个4.7k上拉电阻与3.3v电源相连,以使数据状态线默认状态为高电平状态。

14.进一步地,所述mosfet管包括s端、d端和g端,所述s端接地,所述g端连接所述fpga获取状态信号,所述d端连接所述数据状态线,所述mosfet管根据fpga的状态信号调节d端和s端的连接,通过调节数据状态线的电平输出本侧fpga的数据状态。

15.进一步地,所述fpga包括输出端口do1,所述输出端口do1与mosfet管的g管脚相连,且与一个4.7k下拉电阻相连,将fpga的状态信号输出至所述mosfet管。

16.进一步地,所述fpga包括输入端口di2,所述输入端口di2连接数据状态线以获取对侧fpga的数据状态。

17.进一步地,所述数据状态线的状态包括低电平状态0和高电平状态1,所述高电平状态1表示对侧fpga的数据未准备完毕,所述低电平状态0表示对侧fpga的数据准备完毕,通过blvds总线进行数据通信。

18.与现有技术相比,本实用新型所达到的有益效果:

19.本实用新型提供了一种基于blvds总线数据通信的降功耗通信的电路,包括:两块插件、blvds总线和数据状态线;插件包括fpga、blvds芯片和mosfet管,所述mosfet管的一端连接fpga,所述mosfet管的另一端连接数据状态线,通过调节数据状态线的电平状态输出本侧fpga的数据状态;所述fpga连接数据状态线获取对侧fpga的数据状态;所述fpga连接blvds芯片,blvds芯片之间通过blvds总线进行数据通信。本实用新型增加了基于mosfet的数据状态信号的设置,通过对数据状态总线的监控,能够在数据状态总线空闲时,停止数据的交互,能够节省blvds总线带宽,能够减少了在blvds总线上的无效查询,从而降低整个装置的能耗。

附图说明

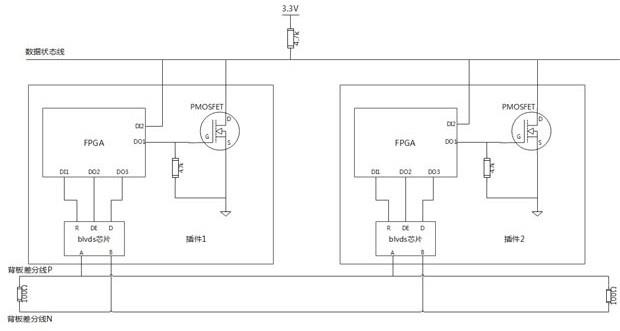

20.图1是本实用新型实施例提供的一种基于blvds总线数据通信的降功耗通信的电路的连接示意图。

具体实施方式

21.下面结合附图对本实用新型作进一步描述。以下实施例仅用于更加清楚地说明本实用新型的技术方案,而不能以此来限制本实用新型的保护范围。

22.在本实用新型的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。此外,术语“第一”、“第二”、“第三”等仅用于描述区分,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。

23.如图1所示,本实用新型提供了一种基于blvds总线数据通信的降功耗通信的电路,包括两块插件、blvds总线和数据状态线。插件包括fpga、blvds芯片和mosfet管。

24.fpga包括输出端口do1、输出端口do2、输出端口do3、输入端口di1和输入端口di2。blvds芯片包括用于传输模拟信号的a管脚、b管脚,以及用于传输数字信号的r管脚、de管脚和d管脚。mosfet管包括s端、d端和g端。

25.blvds总线包括背板差分线p和背板差分线n。背板差分线p和背板差分线n的两端分别通过1块100ω的终端电阻进行连接。blvds芯片包括用于传输模拟信号的a管脚连接背板差分线p,用于传输模拟信号的b管脚连接背板差分线n。

26.fpga输出端口do2连接blvds芯片的de管脚,用于确定数据传输方向。输出端口do3连接blvds芯片的d管脚,用于输出fpga的数据至blvds芯片,输入端口di1连接blvds芯片的r管脚用于接收blvds芯片输出的数据。

27.具体的,de管脚确定的数据传输方向包括方向1和方向0;所述方向1为通过fpga输出端口do3输出fpga的数据至blvds芯片d管脚,通过blvds芯片传输数据至blvds总线;所述方向0为总线传输数据至blvds芯片,通过blvds芯片的r管脚将数据传输至fpga输入端口di1。

28.mosfet管的s端接地。mosfet管的g端连接fpga输出端口do1获取fpga的状态信号,输出端口do1与mosfet管的g管脚相连同时,与一个4.7k下拉电阻相连。mosfet管的d端连接数据状态线, mosfet管根据fpga的状态信号调节d端和s端的连接,通过调节数据状态线的电平输出本侧fpga的数据状态。数据状态线通过一个4.7k上拉电阻与3.3v电源相连,以使数据状态线默认状态为高电平状态。

29.具体的,数据状态线的状态包括低电平状态0和高电平状态1,所述高电平状态1表示对侧fpga的数据未准备完毕,所述低电平状态0表示对侧fpga的数据准备完毕,通过blvds总线进行数据通信。

30.fpga输入端口di2连接数据状态线以获取对侧fpga的数据状态。

31.一种基于blvds总线数据通信的降功耗通信的电路的工作原理为:本侧插件中fpga通过blvds总线发送数据完毕后,通过输入端口di2实时监控数据状态线的状态。若数据状态线的状态为高电平状态1,表示对侧插件中fpga的数据未准备完毕,则等待对侧插件中fpga的数据准备完毕。当对侧插件中fpga的数据准备完毕后,会通过对侧插件中fpga输出端口do1输出状态信号至mosfet管,mosfet管d端和s端的导通,所示数据状态线的状态为低电平状态0。当本侧插件fpga输入端口di2监控数据状态线的状态为低电平状态0时,表示对侧插件fpga的数据准备完毕,此时开始通过blvds总线继续进行数据通信。

32.本实用新型将mosfet管与blvds总线进行结合,能够节省blvds总线带宽,减少了在blvds总线上的无效查询,降低整个装置的能耗。通过mosfet管与fpga管脚相连,即使有多个插件同时拉低数据状态线的电平,也不会导致fpga管脚损坏。

33.以上所述仅是本实用新型的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本实用新型技术原理的前提下,还可以做出若干改进和变形,这些改进和变形也应视为本实用新型的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1