一种多路视频数据处理装置的制作方法

1.本实用新型涉及视频处理技术领域,尤其公开了一种多路视频数据处理装置。

背景技术:

2.在多路视频同时输入的场景中,需要对多路视频接收并进行处理,对于多路信号的显示,现有技术中往往需要多台显示设备,而如果在一台显示设备上同时播放多路信号,则需要同时对多路视频进行处理,存在着多路视频显示时存在实时性差的问题。

3.因此,现有多路视频处理时存在的上述缺陷,是目前亟待解决的技术的问题。

技术实现要素:

4.本实用新型提供了一种多路视频数据处理装置,旨在解决现有多路视频处理时存在的上述缺陷的技术问题。

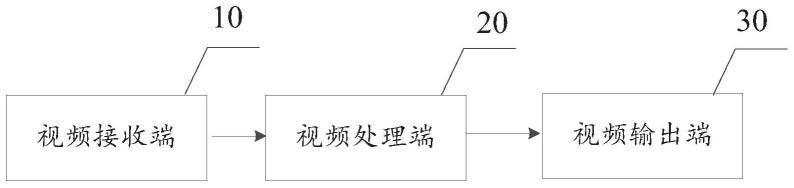

5.本实用新型涉及一种多路视频数据处理装置,包括视频接收端、视频处理端和视频输出端,其中,

6.视频接收端,用于接收多路视频数据;

7.视频处理端分别与视频接收端和视频输出端电连接,用于收集视频接收端接收的多路视频数据,对多路视频数据进行处理,并将处理后的多路视频数据传送给视频输出端;

8.视频输出端与视频处理端电连接,用于接收视频处理端传送过来的多路视频数据,将接收的多路视频数据发送给外部显示器进行显示。

9.进一步地,视频接收端包括串行通道电路和视频解码电路,

10.串行通道电路与视频处理端电连接,用于将接收的多路视频中的串行数据转换成并行数据;

11.视频解码电路与串行通道电路电连接,用于解码串行通道电路转换后的并行数据。

12.进一步地,串行通道电路包括视频输入接口和视频处理模块,

13.视频输入接口,用于接入多路视频串行数据;

14.视频处理模块与视频输入接口电连接,用于将视频输入接口接入的多路视频串行数据转换成并行数据。

15.进一步地,视频输入接口采用hdmi接口。

16.进一步地,视频处理模块采用fpga芯片,fpga芯片的型号为jfm7k325t。

17.进一步地,视频解码电路包括视频解码芯片,视频解码芯片的型号为it6801fn。

18.进一步地,视频处理端包括数据缓存器,数据缓存器用于缓存视频解码电路解码的并行数据。

19.进一步地,视频输出端包括视频编码电路和视频输出电路,

20.视频编码电路与数据缓存器电连接,用于将数据缓存器缓存的并行数据进行编码;

21.视频输出电路与视频编码电路电连接,用于将视频编码电路编码的并行数据以串行方式发送到外部显示器进行显示。

22.进一步地,视频编码电路包括视频编码芯片,视频编码芯片的型号为a912。

23.进一步地,视频输出电路包括串行发送模块。

24.本实用新型所取得的有益效果为:

25.本实用新型提供一种多路视频数据处理装置,采用频接收端、视频处理端和视频输出端,通过视频接收端接收多路视频数据;视频处理端收集视频接收端接收的多路视频数据,对多路视频数据进行处理,并将处理后的多路视频数据传送给视频输出端;视频输出端接收视频处理端传送过来的多路视频数据,将接收的多路视频数据发送给外部显示器进行显示。本实用新型提供一种多路视频数据处理装置,设计简单、延时小;抗干扰能力强、实时性好。

附图说明

26.图1为本实用新型提供的多路视频数据处理装置一实施例的功能框图;

27.图2为图1中所示的视频接收端一实施例的功能模块示意图;

28.图3为图2中所示的串行通道电路一实施例的功能模块示意图;

29.图4为图1中所示的视频处理端一实施例的功能模块示意图;

30.图5为图1中所示的视频输出端一实施例的功能模块示意图。

31.附图标号说明:

32.10、视频接收端;20、视频处理端;30、视频输出端;11、串行通道电路;12、视频解码电路;111、视频输入接口;112、视频处理模块;21、数据缓存器;31、视频编码电路;32、视频输出电路。

具体实施方式

33.为了更好的理解上述技术方案,下面将结合说明书附图以及具体的实施方式对上述技术方案做详细的说明。

34.如图1和图2所示,本实用新型第一实施例提出一种多路视频数据处理装置,包括视频接收端10、视频处理端20和视频输出端30,其中,视频接收端10,用于接收多路视频数据;视频处理端20分别与视频接收端10和视频输出端30电连接,用于收集视频接收端10接收的多路视频数据,对多路视频数据进行处理,并将处理后的多路视频数据传送给视频输出端30;视频输出端30与视频处理端20电连接,用于接收视频处理端20传送过来的多路视频数据,将接收的多路视频数据发送给外部显示器进行显示。

35.进一步地,请见图2,图2为图1中所示的视频接收端一实施例的功能模块示意图,在本实施例中,视频接收端10包括串行通道电路11和视频解码电路12,其中,串行通道电路11与视频处理端20电连接,用于将接收的多路视频中的串行数据转换成并行数据;视频解码电路12与串行通道电路11电连接,用于解码串行通道电路11转换后的并行数据。具体地,视频解码电路12包括视频解码芯片,视频解码芯片采用的型号为it6801fn。本实施例提供的多路视频数据处理装置,通过串行通道电路11将接收的多路视频中的串行数据转换成并行数据,然后由视频解码电路12解码串行通道电路11转换后的并行数据,电路设计简单、延

时小;抗干扰能力强、实时性好。

36.优选地,参见图3,图3为图2中所示的串行通道电路一实施例的功能模块示意图,在本实施例中,串行通道电路11包括视频输入接口111和视频处理模块112,其中,视频输入接口111,用于接入多路视频串行数据;视频处理模块112与视频输入接口111电连接,用于将视频输入接口111接入的多路视频串行数据转换成并行数据。具体地,视频输入接口111采用hdmi接口。视频处理模块112采用fpga芯片,fpga芯片采用的型号为jfm7k325t。本实施例提供的多路视频数据处理装置,通过视频输入接口111接入多路视频串行数据,然后由视频处理模块112将视频输入接口111接入的多路视频串行数据转换成并行数据,电路设计简单、延时小;抗干扰能力强、实时性好。

37.进一步地,参见图4,图4为图1中所示的视频处理端一实施例的功能模块示意图,在本实施例中,视频处理端20包括数据缓存器21,数据缓存器21用于缓存视频解码电路12解码的并行数据。本实施例提供的多路视频数据处理装置,通过数据缓存器21缓存视频解码电路12解码的并行数据,电路设计简单、延时小;抗干扰能力强、实时性好。

38.优选地,请见图5,图5为图1中所示的视频输出端一实施例的功能模块示意图,在本实施例中,视频输出端30包括视频编码电路31和视频输出电路32,其中,视频编码电路31与数据缓存器21电连接,用于将数据缓存器21缓存的并行数据进行编码;视频输出电路32与视频编码电路31电连接,用于将视频编码电路31编码的并行数据以串行方式发送到外部显示器进行显示。具体地,视频编码电路31包括视频编码芯片,视频编码芯片采用的型号为a912。视频输出电路32包括串行发送模块。本实施例提供的多路视频数据处理装置,通过视频编码电路31将数据缓存器21缓存的并行数据进行编码,再由视频输出电路32将视频编码电路31编码的并行数据以串行方式发送到外部显示器进行显示,电路设计简单、延时小;抗干扰能力强、实时性好。

39.如图1至图5所示,本实施例提供的多路视频数据处理装置,其工作原理为:

40.hdmi接口接入多路视频串行数据,fpga芯片jfm7k325t将hdmi接口接入的多路视频串行数据转换成并行数据。视频解码芯片it6801fn解码fpga芯片jfm7k325t转换后的并行数据。数据缓存器21缓存视频解码芯片it6801fn解码的并行数据。视频编码芯片a912将数据缓存器21缓存的并行数据进行编码;串行发送模块将视频编码芯片a912编码的并行数据以串行方式发送到外部显示器进行显示。

41.本实施例提供的多路视频数据处理装置,同现有技术相比,采用频接收端、视频处理端和视频输出端,通过视频接收端接收多路视频数据;视频处理端收集视频接收端接收的多路视频数据,对多路视频数据进行处理,并将处理后的多路视频数据传送给视频输出端;视频输出端接收视频处理端传送过来的多路视频数据,将接收的多路视频数据发送给外部显示器进行显示。本实施例提供的多路视频数据处理装置,设计简单、延时小;抗干扰能力强、实时性好。

42.尽管已描述了本实用新型的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本实用新型范围的所有变更和修改。显然,本领域的技术人员可以对本实用新型进行各种改动和变型而不脱离本实用新型的精神和范围。这样,倘若本实用新型的这些修改和变型属于本实用新型权利要求及其等同技术的范围之内,则本实用新型

也意图包含这些改动和变型在内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1