一种电源分配网络阻抗优化的M.2接口的5G通信模块的制作方法

一种电源分配网络阻抗优化的m.2接口的5g通信模块

技术领域

1.本实用新型涉及通信技术领域,具体涉及一种电源分配网络阻抗优化的m.2接口的5g通信模块。

背景技术:

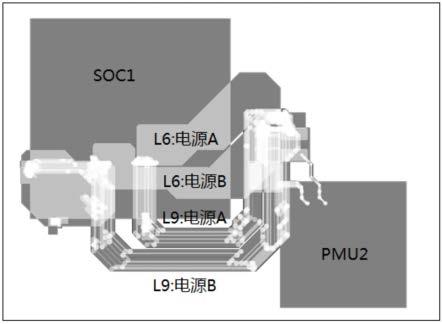

2.在5g移动通信技术快速发展的时代,电路系统向着高速度、高密度、高功耗、低电压和大电流的趋势发展。电路系统工作的可靠性和稳定性成为高速电路发展的关键。电源分配网络(pdn)由电源、地走线、平面以及去耦电容等构成,由于电容、回路电阻、回路电感等因素的共同作用,pdn阻抗随频率而变化,随着频率的增加,回路电感对于pdn阻抗的影响逐渐占据主要地位。因此,降低回路电感对优化电源分配网络的阻抗有着很好的效果,主要有以下几种常用的优化方法:1)增加电源孔、地孔的数量;2)增加电源走线的线宽,且电源走线尽量短、直;3)对去耦电容的容值、数量进行反复配置。目前在这种pin间距越小,出线越密集的bga芯片下方,增加电源孔和地孔难度会很大,在一些苛刻的条件下,增加电源孔和地孔是不可能实现的;而对去耦电容的容值和数量进行反复配置、仿真、调整迭代,工作量较大且效率不高,如果增加电容会带来成本的增加,此外,m.2接口的5g通信模块尺寸小,且pcb布局采用的是单面布局,给bga芯片四周增加去耦电容也带来了非常大的难度。以下以实际用例说明现有技术的缺点,如图1所示,soc1的供电电源a和电源b,由pmu2的两个dc分别输出,经9层u形走线供给soc1,首次pdn仿真结果不通过。因此在现有布局和走线的情况下,在soc芯片下方,增加电源a和电源b的电源孔和地孔的数量,以及靠近soc的pin增加电容,优化后,电源a及电源b在100mhz时的交流阻抗距离目标值还是较大,实际仿真结果fail,如图2所示。

技术实现要素:

3.针对上述不足,本实用新型提供了一种电源分配网络阻抗优化的m.2接口的5g通信模块,包括印刷电路板pcb,所述印刷电路板pcb包括pcb本体,所述pcb本体为十层二阶hdi板,分为主地层和铺地层,在所述铺地层给电源增加铺铜走线,本实用新型在10层二阶pcb不加层的基础上,以在辅地层敷铜的方式给电源增加并联支路,降低电流路径上过孔的安装电感和走线的等效串联电感esl,优化电源在交流100mhz时的交流阻抗,提高pdn仿真的通过率。

4.为了实现上述目的,本实用新型采用以下技术方案:

5.一种电源分配网络阻抗优化的m.2接口的5g通信模块,包括印刷电路板pcb,所述印刷电路板pcb包括pcb本体,所述pcb本体为十层二阶hdi板,分为主地层和铺地层,在所述铺地层给电源增加铺铜走线。本实用新型提供的m.2接口的5g通信模块在满足pcb叠层和单面布局不变,保证主地层地平面完整、辅地层地平面局部完整的同时,基于电流流向,以在辅地层敷铜的方式给电源增加并联支路,降低电流路径上过孔的安装电感和走线的等效串联电感esl,优化电源在交流100mhz时的交流阻抗,提高pdn仿真的通过率。与传统做法相

比,本实用新型仅通过在辅地层增加电源走线的铺铜设计环节,即可提升电源分配网络的电源完整性,降低了pdn的阻抗值,使其小于目标阻抗,达到优化的效果,在降低设计成本的同时,极大提高了设计效率;且soc规模越大,电源分配网络的管脚数量越多,对pdn阻抗的优化效果越明显。

6.作为优选,所述5g通信模块单面布局,包括射频rf单元和基带bb单元。5g通信模块尺寸是30mm*52mm,单面布局,由rf和bb两部分组成,其中bb的有效布局面积是30mm*22mm。

7.作为优选,所述pcb本体的顶层为器件放置层。

8.作为优选,信号线主要分布在所述pcb本体的第二、三、五层。

9.作为优选,电源主要分布在所述pcb本体的第七、八、九层。

10.作为优选,所述pcb本体的顶层器件包括系统级芯片soc。

11.因此,本实用新型的优点是:在满足pcb叠层和单面布局不变,保证主地层地平面完整、辅地层地平面局部完整的同时,基于电流流向,在辅地层给电源增加铺铜走线,降低电流路径上过孔的安装电感和走线的等效串联电感esl,优化电源在交流100mhz时的交流阻抗,提高pdn仿真的通过率;在降低设计成本的同时,极大提高了设计效率;soc规模越大,电源分配网络的管脚数量越多,对pdn阻抗的优化效果越明显。

附图说明

12.图1是本实用新型背景技术中pcb本体的结构示意图。

13.图2是本实用新型背景技术中仿真结果图。

14.图3是本实用新型实施例中pcb本体的结构示意图。

15.图4是本实用新型实施例中仿真结果图。

16.图5是本实用新型实施例中一种电源分配网络阻抗优化的m.2接口的5g通信模块的结构示意图。

17.图6是本实用新型实施例中pcb本体的层次结构示意图。

18.1、soc 2、pmu 3、rf 4、bb 5、flash。

具体实施方式

19.下面结合附图与具体实施方式对本实用新型做进一步的描述。

20.一种电源分配网络阻抗优化的m.2接口的5g通信模块,包括印刷电路板pcb,印刷电路板pcb包括pcb本体,pcb本体是10层二阶hdi板,如图6所示,其中4层为主地层,6层为辅地层,顶层(1层)为器件放置层,信号线(含关键信号线)主要分布在pcb本体的2、3、5层,电源主要分布在pcb本体的7、8、9层。

21.一种电源分配网络阻抗优化的m.2接口的5g通信模块,平台器件是展锐的5g高度集成通信处理器udx710m6,主频高达1.35ghz,搭配pmu、flash,以及时钟等外围器件构成bb最小工作系统。如图5所示,模块尺寸是30mm*52mm,单面布局,由rf3和bb4两部分组成,其中bb4的有效布局面积是30mm*22mm。

22.如图3所示,soc1的供电电源a和电源b,由pmu2的两个dc分别输出,经9层u形走线供给soc1,本实施例在辅地层给电源a及电源b分别增加并联走线(6层走线),两个电源的走线均缩短了很多距离,进而减小了走线的esl,并且缩短了顶层器件(系统级芯片soc)与电

源平面之间的距离h

top

,在过孔中心间距s和过孔直径d不变的前提下,根据可得出电流路径上安装电感l

mount

随着h

top

的减小而变小;同样,根据谐振频率公式l

mount

和esl变小,f

mount

会增加,从而提高了电容的滤波效果。经过实际仿真后pdn结果pass,如图4所示。

23.本实用新型提供的m.2接口的5g通信模块在满足pcb叠层和单面布局不变,保证主地层地平面完整、辅地层地平面局部完整的同时,基于电流流向,以在辅地层敷铜的方式给电源增加并联支路,降低电流路径上过孔的安装电感和走线的等效串联电感esl,优化电源在交流100mhz时的交流阻抗,提高pdn仿真的通过率。

24.以上内容,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1