通信接口的配置方法和通信接口与流程

本发明涉及芯片技术应用领域,尤其涉及一种通信接口的配置方法和通信接口。

背景技术:

1、随着通信领域的不断发展,无线收发芯片在日常生活中的应用场景变得越来越广泛。工业界通常使用各种各样的接口协议来实现微控制单元(microcontroller unit;简称mcu)对无限收发芯片的控制。其中串行外设接口(serial peripheral interface,简称spi)由于其高速、全双工、同步的特点,成为许多mcu和无限收发芯片之间常用的接口协议。spi能够使mcu实现对无线收发芯片的各种参数与功能的配置,从而实现通信场合的应用。

2、spi接口一般使用四根线:mosi(主设备数据输出,从设备数据输入,master inputslave output),miso(主设备数据输入,从设备数据输出,master output slave input),sclk(时钟信号,由主设备产生,serial clock),片选信号csb(从设备片选信号,由主设备发出,低位0表示有效,chip select)。

3、现有mcu对无线收发芯片进行寄存器配置或fifo读写时,主机必须发送对应操作的指令,从机一侧需要对指令进行译码后才能进行数据的传输。译码功能的实现加大了无线收发芯片的复杂度,且译码和无线收发芯片内部状态的切换需要花费一定的时间,降低了数据传输的效率。同时,读写从机寄存器和fifo之间的切换也只能通过主机一侧更改要发送的指令类型来实现,读写寄存器和fifo的切换方式不够灵活。而且此种spi对接方式并不支持对寄存器或fifo的连续读写,如果想要读写32bit的寄存器,需要进行4次8bit的数据传输或2次16bit的数据传输,不够高效。

4、针对上述由于现有技术中mcu对无线收发芯片进行寄存器配置或fifo读写时在译码和读写的过程中耗时过高,导致的数据传输效率低的问题,目前尚未提出有效的解决方案。

技术实现思路

1、为解决上述技术问题,本发明实施例期望提供一种通信接口的配置方法和通信接口,以至少解决由于现有技术中mcu对无线收发芯片进行寄存器配置或fifo读写时在译码和读写的过程中耗时过高,导致的数据传输效率低的问题。

2、本发明的技术方案是这样实现的:

3、第一方面,本发明实施例提供一种通信接口,包括:通信接口通过mosi引脚、miso引脚、sclk引脚和nss引脚与无线收发芯片连接,其中,miso引脚为主设备输入/从设备输出引脚,用于在从模式下发送数据,在主模式下接收数据;mosi引脚为主设备输出/从设备输入引脚,用于在主模式下发送数据,在从模式下接收数据;sclk引脚为串口时钟,用于主设备的输出,从设备的输入;nss引脚为主设备或从设备选择引脚,用于通过设置nss[0]作为csb信号对无线收发芯片的寄存器进行片选,以及通过设置nss[1]作为fcsb信号对无线收发芯片的fifo进行片选;其中,产生时钟的一侧称为主设备,另一侧称为从设备;通信接口为单线双向模式,mosi引脚和miso引脚合并为安全数字输入输出端口。

4、可选的,通信接口还包括:发送缓冲器、移位寄存器、sts寄存器和第一ctrl寄存器,其中,发送缓冲器,用于在写操作中,数据写入发送缓冲器;当从设备接收到时钟信号,且在mosi引脚出现第一数据位时,数据发送过程开始,数据帧格式中的剩余数位存至移位寄存器;当发送缓冲器中的数据传输到移位寄存器时,设置spi_sts寄存器的te标志;若设置第一ctrl寄存器的teie位,则产生中断。

5、进一步地,可选的,通信接口还包括:接收缓冲器,其中,接收缓冲器,用于当数据接收完成时,移位寄存器中的数据传送到接收缓冲器,设置sts寄存器中的rne标志;若设置第一ctrl寄存器中的rneie位,则产生中断;在最后一个采样时钟边沿后,设置rne位为1,移位寄存器中接收到的数据字节被传送到接收缓冲器;当读dt寄存器时,通信接口返回接收缓冲器的数值,并清除rne位。

6、可选的,第一ctrl寄存器中增加rf_en位和fifo_mode位,rf_en位,用于mcu配置通信接口开启对无线收发芯片的读写寄存器模式;fifo_mode位,用于mcu配置通信接口开启对无线收发芯片的读写fifo模式。

7、进一步地,可选的,通信接口还包括:主控制电路,其中,在第一ctrl寄存器增加nss_sel位,用于在主控制电路中使能nss[0]和nss[1];当nss_sel位设置为0时,nss[0]有效,nss[0]作为csb信号对无线收发芯片中的寄存器片选;当nss_sle位设置为1时,nss[1]有效,nss[1]作为fcsb信号对无线收发芯片中的寄存器片选。

8、可选的,主控制电路包括:以总线时钟为参考时钟的定时器,其中,定时器,用于在读写寄存器模式下,定时器在拉低csb信号时开始计数,当定时器到达计数阈值时,发送第一使能信号,启动数据传输。

9、进一步地,可选的,当主控制电路检测到数据传输到预设数据时,开启定时器,定时器定时到达计数阈值时,产生第二使能信号,拉高csb信号。

10、可选的,通信接口还包括:延时计数器;其中,第一ctrl寄存器中还增加了tim_cycle位,用于配置延迟时间;延时计数器,用于从最后一个sclk的下降沿开始计数,当延时计数器计时到延迟时间时,拉高fcsb信号;当延时计数器计时到延迟时间的预设倍数时,若传输数据,则拉低fcsb信号;若不传输数据,则保持fcsb信号为高电平。

11、可选的,通信接口还包括:第二ctrl寄存器,其中,第二ctrl寄存器,用于当通信接口配置为读寄存器模式后,检测mcu发送的地址0,并在sclk的下降沿前,将第二ctrl寄存器中的bdoe位的电平信号进行切换,以使得将io口由输出切换为输入。

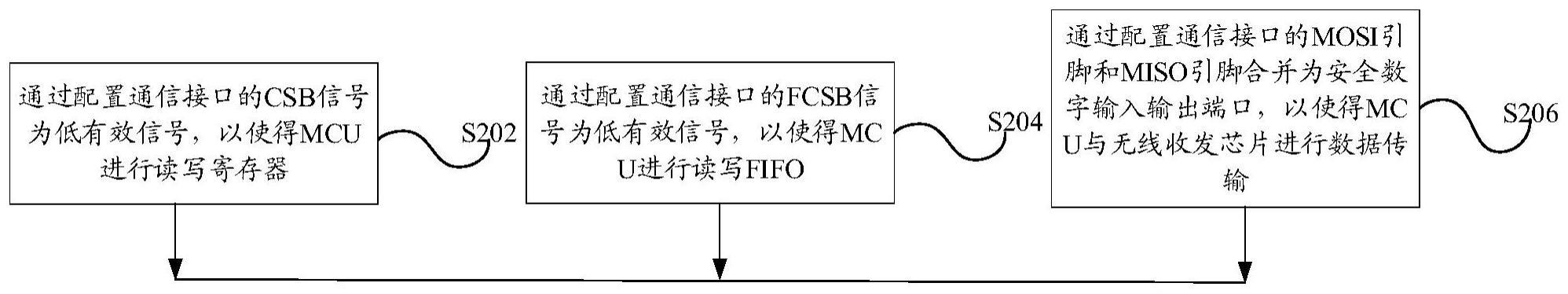

12、第二方面,本发明实施例提供一种通信接口的配置方法,应用于上述通信接口,包括:通过配置通信接口的csb信号为低有效信号,以使得mcu进行读写寄存器;通过配置通信接口的fcsb信号为低有效信号,以使得mcu进行读写fifo;通过配置通信接口的mosi引脚和miso引脚合并为安全数字输入输出端口,以使得mcu与无线收发芯片进行数据传输。

13、可选的,该方法还包括:配置通信接口为单线双向模式,并设置波特率与数据帧格式;其中,配置通信接口为单线双向模式,并设置波特率与数据帧格式包括:通过第二ctrl寄存器的mclkp位确定串行时钟波特率;通过配置第二ctrl寄存器的cpol和cpha位为0,确定数据传输和串行时钟间的相位关系,其中,相位关系为:串行时钟的下降沿发送数据,串行时钟的上升沿采样数据;通过配置第二ctrl寄存器的dff16位,确定数据帧格式为8位或16位;通过配置第二ctrl寄存器的lsben位为0,确定数据帧格式为先发送或接收最高有效位msb;如果确定csb引脚工作在输入模式,在硬件模式下,在数据帧传输期间,配置csb引脚的电平信号为高电平信号;在软件模式下,配置第二ctrl寄存器的swnssen位和iss位;如果csb引脚工作在输出模式,配置第一ctrl寄存器的nssoe位;通过配置第二ctrl寄存器的bdmode位,通信接口启用单线双向模式,其中,sclk引脚作为时钟,主设备使用mosi引脚,从设备使用miso引脚进行数据通信;传输的方向由第二ctrl寄存器里的bdoe位控制,当bdoe位为1时,数据输出;当bdoe位为0时,数据输入;通过配置dt寄存器,写入读写的无线收发芯片的地址;通过设置第二ctrl寄存器的msten位,配置通信接口为主设备。

14、可选的,该方法还包括:配置通信接口为读写无线收发寄存器模式;其中,配置通信接口为读写无线收发寄存器模式包括:通过配置第一ctrl寄存器中nss_sel位为0,选择使用csb信号作为片选信号;通过配置第一ctrl寄存器中rf_en位为1,开启读写无线收发寄存器模式;通过配置第二ctrl寄存器中en位为1,使能通信接口。

15、可选的,通过配置通信接口的fcsb信号为低有效信号,以使得mcu进行读写fifo包括:通过配置第一ctrl寄存器中nss_sel位为1,选择使用fcsb作为片选信号;通过配置第一ctrl寄存器中tim_cycle位,确定fifo模式下连续读写操作间的延迟时间;通过配置第一ctrl寄存器中fifo_mode位为1,开启fifo模式;通过配置第二ctrl寄存器中spi_en位为1,使能通信接口。

16、本发明实施例提供了一种通信接口的配置方法和通信接口。通过配置通信接口的csb信号为低有效信号,以使得mcu进行读写寄存器;通过配置通信接口的fcsb信号为低有效信号,以使得mcu进行读写fifo;通过配置通信接口的mosi引脚和miso引脚合并为安全数字输入输出端口,以使得mcu与无线收发芯片进行数据传输,从而能够实现通过mcu对寄存器的配置来实现rf模式和fifo模式的选择和切换,替代了发送命令式的通信模式,减少了无线收发芯片的译码工作和内部状态反应时间的技术效果。

- 还没有人留言评论。精彩留言会获得点赞!