statsmemory多模式报文统计的芯片实现方法及应用与流程

本发明是关于电子通信领域,特别是关于一种stats memory多模式报文统计的芯片实现方法及应用。

背景技术:

1、stats指对网络中的报文做统计,一般统计报文个数和报文字节数,基于port表、vlan表、路由表和acl(access control list,访问控制列表)等进行报文统计。当前通用的实现方法为,表项出stats memory的索引即statsptr,stats engine基于statsptr做报文个数和报文字节数统计。假设一块stats memory宽度为72bit,能存放4k个统计数据,统计数据为72个bit,其中高36个bit为报文个数,低36个bit为报文字节数,那么statsptr为12个bit,范围为0~4095。

2、该现有技术方案的限制在于,只要出了statsptr就一定会同时做报文个数统计和报文字节数统计。但是在很多实际应用或者调试场景中,只需要统计报文个数,此时统计报文字节数没有意义。然而由于该方案的实现原理,导致每个stats还会做报文字节数统计,那么报文字节数统计所占的memory也就无法空出来给其他stats用来做报文个数统计。

3、如果每个stats都只做报文个数统计,整体上stats memory资源就浪费了一半,从而无法充分利用stats memory资源。并且在现有的方案中,统计报文个数和报文字节数分别只能统计36个bit,对上百g流量的业务进行统计的时候,36bit很快就会溢出,无法精确统计大流量业务。

4、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种stats memory多模式报文统计的芯片实现方法及应用,其能够实现stats memory的灵活使用,充分利用stats memory的资源。

2、为实现上述目的,本发明的实施例提供了一种stats memory多模式报文统计的芯片实现方法。

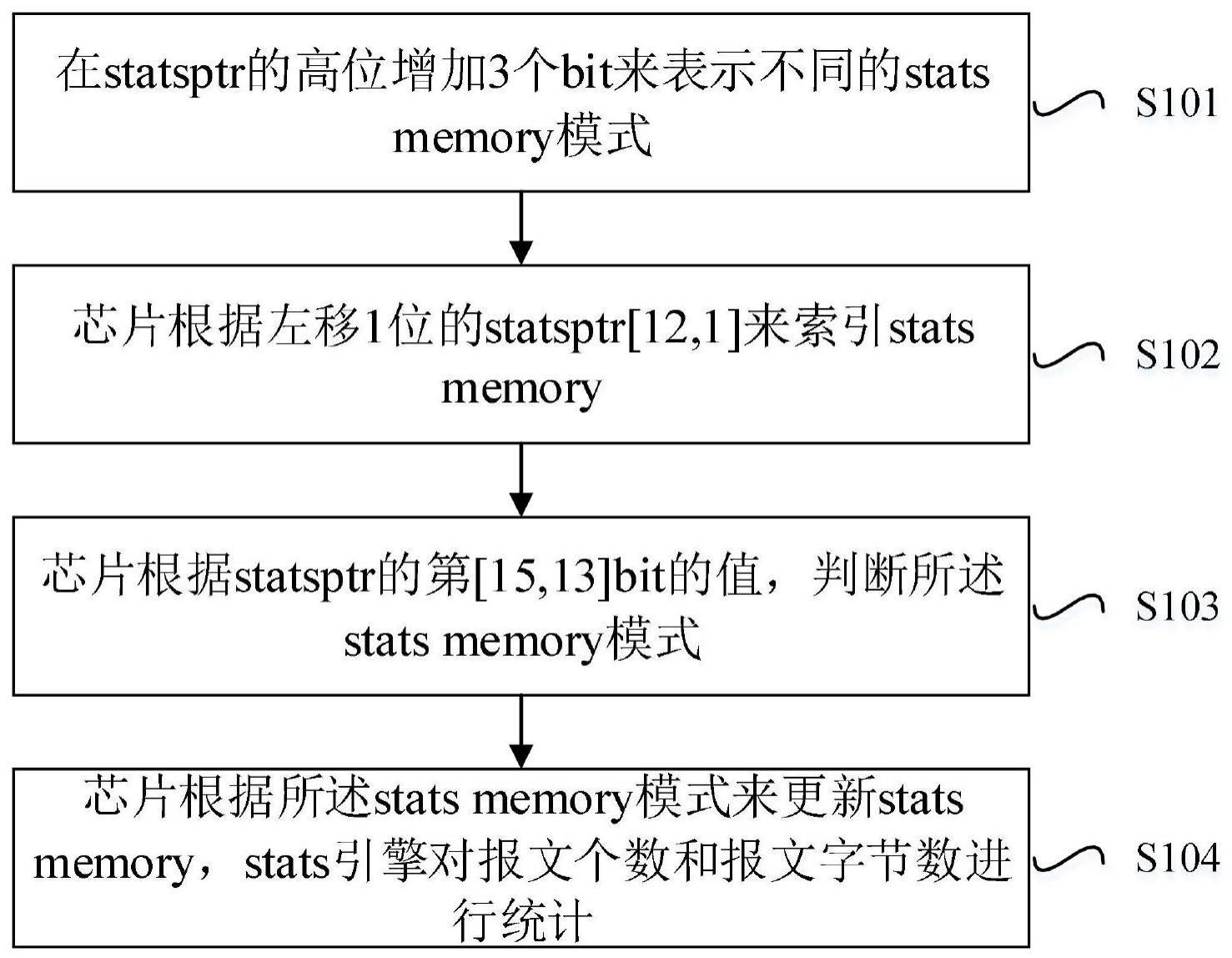

3、在本发明的一个或多个实施方式中,所述芯片实现方法包括:在statsptr的高位增加3个bit来表示不同的stats memory模式,其中所述statsptr为表项出stats memory的索引,总位数为16bit;芯片根据左移1位的statsptr[12,1]来索引stats memory,其中所述stats memory宽度为72bit;芯片根据statsptr的第[15,13]bit的值,判断所述statsmemory模式;以及芯片根据所述stats memory模式来更新stats memory,stats引擎对报文个数和报文字节数进行统计。

4、在本发明的一个或多个实施方式中,其中不同的stats memory模式包括模式0、模式3和模式4,所述芯片根据所述stats memory模式来更新stats memory,包括:若所述stats memory为模式0、模式3或模式4,则对所述stats memory中的72bit进行更新,其中:模式0,用于同时统计报文个数packetcount和报文字节数packetbyte,所述报文个数packetcount和报文字节数packetbyte分别为36bit;模式3,用于统计报文个数packetconut,所述报文个数packetcount为72bit;模式4,用于统计报文字节数packetbyte,所述报文字节数packetbyte为72bit。

5、在本发明的一个或多个实施方式中,其中不同的stats memory模式还包括模式1和模式2,所述芯片根据所述stats memory模式来更新stats memory,包括:若所述statsmemory为模式1或模式2,则对所述stats memory中的36bit进行更新,其中:模式1,用于统计报文个数packetcount,所述报文个数packetcount为36bit;模式2,用于统计报文字节数packetbyte,所述报文字节数packetbyte为36bit。

6、在本发明的一个或多个实施方式中,所述根据statsptr的第[15,13]bit的值,判断所述stats memory模式,包括:若statsptr的第[15,13]bit的值等于0,即高3bit为000,表示stats memory为模式0;若statsptr的第[15,13]bit的值等于1,即高3bit为001,表示stats memory为模式1;若statsptr的第[15,13]bit的值等于2,即高3bit为010,表示statsmemory为模式2;若statsptr的第[15,13]bit的值等于3,即高3bit为011,表示statsmemory为模式3;若statsptr的第[15,13]bit的值等于4,即高3bit为100,表示statsmemory为模式4。

7、在本发明的一个或多个实施方式中,对所述stats memory中的72bit进行更新,包括:在模式0中,芯片对stats memory中的高36bit进行报文个数packetcounts的更新,对stats memory中的低36bit进行报文字节数packetbytes的更新;在模式3中,芯片对statsmemory中的72bit进行报文个数packetcounts的更新;在模式4中,芯片对stats memory中的72bit进行报文字节数packetbytes的更新。

8、在本发明的一个或多个实施方式中,对所述stats memory中的36bit进行更新,包括:在模式1中,芯片对stats memory中的36bit进行报文个数packetcounts的更新;在模式2中,芯片对stats memory中的36bit进行报文字节数packetbytes的更新。

9、在本发明的一个或多个实施方式中,所述方法还包括:在模式1或模式2中,statsptr的低13bit是0~213中的任意值;在模式0、模式3或模式4中,statsptr的低13bit是0~213中的任意偶数值。

10、在本发明的另一个方面当中,提供了一种stats memory多模式报文统计的芯片实现装置,其包括创建模块、索引模块、判断模块和更新模块。

11、创建模块,用于在statsptr的高位增加3个bit来表示不同的stats memory模式,其中所述statsptr为表项出stats memory的索引,总位数为16bit。

12、索引模块,用于芯片根据左移1位的statsptr[12,1]来索引stats memory,其中所述stats memory宽度为72bit。

13、判断模块,用于芯片根据statsptr的第[15,13]bit的值,判断所述stats memory模式。

14、更新模块,用于芯片根据所述stats memory模式来更新stats memory,stats引擎对报文个数和报文字节数进行统计。

15、在本发明的一个或多个实施方式中,所述创建模块还用于:不同的stats memory模式包括模式0、模式3和模式4,若所述stats memory为模式0、模式3或模式4,则对所述stats memory中的72bit进行更新,其中:模式0,用于同时统计报文个数packetcount和报文字节数packetbyte,所述报文个数packetcount和报文字节数packetbyte分别为36bit;模式3,用于统计报文个数packetconut,所述报文个数packetcount为72bit;模式4,用于统计报文字节数packetbyte,所述报文字节数packetbyte为72bit。

16、在本发明的一个或多个实施方式中,所述创建模块还用于:不同的stats memory模式还包括模式1和模式2,若所述stats memory为模式1或模式2,则对所述stats memory中的36bit进行更新,其中:模式1,用于统计报文个数packetcount,所述报文个数packetcount为36bit;模式2,用于统计报文字节数packetbyte,所述报文字节数packetbyte为36bit。

17、在本发明的一个或多个实施方式中,所述创建模块还用于:在模式1或模式2中,statsptr的低13bit是0~213中的任意值;在模式0、模式3或模式4中,statsptr的低13bit是0~213中的任意偶数值。

18、在本发明的一个或多个实施方式中,所述判断模块还用于:若statsptr的第[15,13]bit的值等于0,即高3bit为000,表示stats memory为模式0;若statsptr的第[15,13]bit的值等于1,即高3bit为001,表示stats memory为模式1;若statsptr的第[15,13]bit的值等于2,即高3bit为010,表示stats memory为模式2;若statsptr的第[15,13]bit的值等于3,即高3bit为011,表示stats memory为模式3;若statsptr的第[15,13]bit的值等于4,即高3bit为100,表示stats memory为模式4。

19、在本发明的一个或多个实施方式中,所述更新模块还用于:在模式0中,芯片对stats memory中的高36bit进行报文个数packetcounts的更新,对stats memory中的低36bit进行报文字节数packetbytes的更新;在模式3中,芯片对stats memory中的72bit进行报文个数packetcounts的更新;在模式4中,芯片对stats memory中的72bit进行报文字节数packetbytes的更新。

20、在本发明的一个或多个实施方式中,所述更新模块还用于:在模式1中,芯片对stats memory中的36bit进行报文个数packetcounts的更新;在模式2中,芯片对statsmemory中的36bit进行报文字节数packetbytes的更新。

21、在本发明的另一个方面当中,提供了一种电子设备,包括:至少一个处理器;以及存储器,所述存储器存储指令,当所述指令被所述至少一个处理器执行时,使得所述至少一个处理器执行如上所述的stats memory多模式报文统计的芯片实现方法。

22、在本发明的另一个方面当中,提供了一种计算机可读存储介质,所述计算机可读存储介质上存储有计算机程序,所述计算机程序被处理器执行时实现如所述的statsmemory多模式报文统计的芯片实现方法的步骤。

23、与现有技术相比,根据本发明实施方式的stats memory多模式报文统计的芯片实现方法及应用,其能够解决stats memory的资源浪费问题,通过statsptr最高的3个bit来表示多个stats memory模式,基于不同的模式来控制不同的报文内容统计以及不同的位宽统计的进行,针对不同模式来指定操作stats memory的方式,有效地实现了stats memory的灵活使用,达到充分利用stats memory的资源。

- 还没有人留言评论。精彩留言会获得点赞!