基于信息安全的数据处理加速方法、装置、设备及介质与流程

本发明涉及信息传输以及信息加密领域,特别涉及一种基于信息安全的数据处理加速方法、装置、设备及介质。

背景技术:

1、fpga(field programmable gate array)是在pal(programmable array logic,可编程阵列逻辑)、gal(generic array logic,通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(application specific integrated circuit,asic)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。随着科技的发展,fpga芯片的集成度越来越高,信息收发的速度越来越快,快速的收发要求意味着更高的主频,更高的工作频率。但相比于其他种类的芯片设计,fpga芯片通常需要设置较高门槛并且拟定严格性较强的基本设计流程。而现有的基础外设的主频难以满足对更高主频的需求,并且在信息发送的过程,信息安全也是尤其重要的一个环节,且现有技术也难以满足在保证信息安全的前提下,提高信息处理的速度。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种基于信息安全的数据处理加速方法、装置、设备及介质,可以在保证信息安全的情况下有效对数据的处理流程进行加速。其具体方案如下:

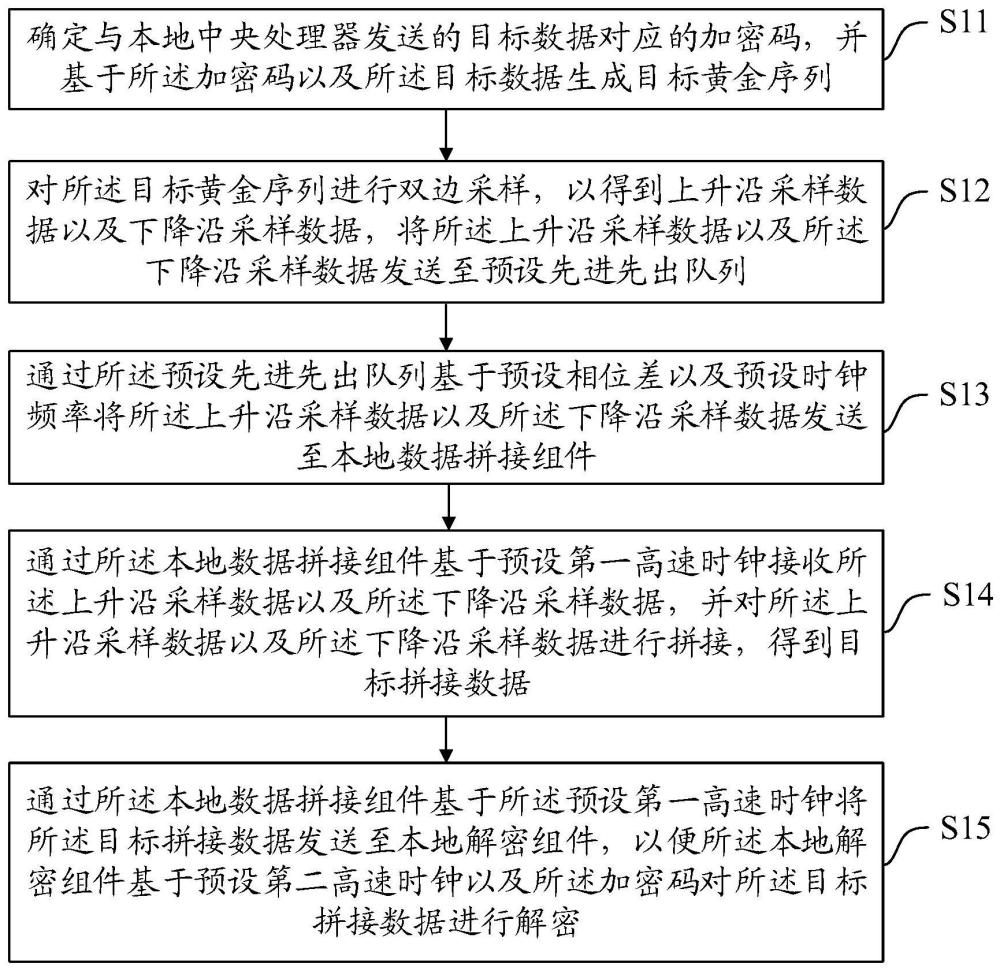

2、第一方面,本技术公开了一种基于信息安全的数据处理加速方法,应用于fpga芯片,包括:

3、确定与本地中央处理器发送的目标数据对应的加密码,并基于所述加密码以及所述目标数据生成目标黄金序列;

4、对所述目标黄金序列进行双边采样,以得到上升沿采样数据以及下降沿采样数据,将所述上升沿采样数据以及所述下降沿采样数据发送至预设先进先出队列;

5、通过所述预设先进先出队列基于预设相位差以及预设时钟频率将所述上升沿采样数据以及所述下降沿采样数据发送至本地数据拼接组件;

6、通过所述本地数据拼接组件基于预设第一高速时钟接收所述上升沿采样数据以及所述下降沿采样数据,并对所述上升沿采样数据以及所述下降沿采样数据进行拼接,得到目标拼接数据;

7、通过所述本地数据拼接组件基于所述预设第一高速时钟将所述目标拼接数据发送至本地解密组件,以便所述本地解密组件基于预设第二高速时钟以及所述加密码对所述目标拼接数据进行解密。

8、可选的,所述确定与本地中央处理器发送的目标数据对应的加密码,并基于所述加密码以及所述目标数据生成目标黄金序列,包括:

9、基于本地中央处理器发送的目标数据生成第一m序列,并确定所述目标数据对应的加密码,以基于所述加密码生成第二m序列;

10、对所述第一m序列以及所述第二m序列进行异或处理,以对所述目标数据进行加密,得到目标黄金序列。

11、可选的,所述对所述目标黄金序列进行双边采样,以得到上升沿采样数据以及下降沿采样数据,将所述上升沿采样数据以及所述下降沿采样数据发送至预设先进先出队列,包括:

12、基于预设计时器对所述目标黄金序列进行双边采样,若所述预设计时器当前数值为第一计时器数值,则通过第一通路收集上升沿采样数据,若所述预设计时器当前数值为第二计时器数值,则通过第二通路收集下降沿采样数据;

13、基于预设通信协议将所述上升沿采样数据发送至第一先进先出队列,并将所述下降沿采样数据发送至第二先进先出队列。

14、可选的,所述通过所述预设先进先出队列基于预设相位差以及预设时钟频率将所述上升沿采样数据以及所述下降沿采样数据发送至本地数据拼接组件,包括:

15、确定预设时钟频率以及预设相位差,并根据所述预设相位差确定所述第一先进先出队列对应的第一发送周期以及所述第二先进先出队列对应的第二发送周期;

16、利用所述第一先进先出队列基于所述预设时钟频率以及所述第一发送周期将所述上升沿采样数据发送至本地数据拼接组件,并利用所述第二先进先出队列基于所述预设时钟频率以及所述第二发送周期将所述下降沿采样数据发送至所述本地数据拼接组件。

17、可选的,所述通过所述本地数据拼接组件基于预设第一高速时钟接收所述上升沿采样数据以及所述下降沿采样数据,并对所述上升沿采样数据以及所述下降沿采样数据进行拼接,得到目标拼接数据,包括:

18、确定预设高速时钟对应的第一高速时钟频率,以通过所述本地数据拼接组件基于所述第一高速时钟频率接收所述上升沿采样数据以及所述下降沿采样数据,并对所述上升沿采样数据以及所述下降沿采样数据进行拼接,得到目标拼接数据。

19、可选的,所述通过所述本地数据拼接组件基于所述预设第一高速时钟将所述目标拼接数据发送至本地解密组件,以便所述本地解密组件基于预设第二高速时钟以及所述加密码对所述目标拼接数据进行解密,包括:

20、通过所述本地数据拼接组件基于所述第一高速时钟频率将所述目标拼接数据发送至本地解密组件;

21、确定预设第二高速时钟对应的第二高速时钟频率,以通过本地解密组件基于所述第二高速时钟频率以及所述加密码对所述目标拼接数据进行解密。

22、可选的,所述通过本地解密组件基于所述第二高速时钟频率以及所述加密码对所述目标拼接数据进行解密,包括:

23、通过所述加密码基于所述第二高速时钟频率对所述目标拼接数据进行解密,并对得到的解密数据进行异或运算以及逆运算,以将所述目标拼接数据还原为所述目标数据,并将所述目标数据上报至目标上位机。

24、第二方面,本技术公开了一种基于信息安全的数据处理加速装置,应用于fpga芯片,包括:

25、序列生成模块,用于确定与本地中央处理器发送的目标数据对应的加密码,并基于所述加密码以及所述目标数据生成目标黄金序列;

26、数据采样模块,对所述目标黄金序列进行双边采样,以得到上升沿采样数据以及下降沿采样数据,将所述上升沿采样数据以及所述下降沿采样数据发送至预设先进先出队列;

27、数据发送模块,用于通过所述预设先进先出队列基于预设相位差以及预设时钟频率将所述上升沿采样数据以及所述下降沿采样数据发送至本地数据拼接组件;

28、数据拼接模块,用于通过所述本地数据拼接组件基于预设第一高速时钟接收所述上升沿采样数据以及所述下降沿采样数据,并对所述上升沿采样数据以及所述下降沿采样数据进行拼接,得到目标拼接数据;

29、数据解密模块,用于通过所述本地数据拼接组件基于所述预设第一高速时钟将所述目标拼接数据发送至本地解密组件,以便所述本地解密组件基于预设第二高速时钟以及所述加密码对所述目标拼接数据进行解密。

30、第三方面,本技术公开了一种电子设备,包括:

31、存储器,用于保存计算机程序;

32、处理器,用于执行所述计算机程序以实现如前述的基于信息安全的数据处理加速方法。

33、第四方面,本技术公开了一种计算机可读存储介质,用于保存计算机程序,所述计算机程序被处理器执行时实现如前述的基于信息安全的数据处理加速方法。

34、本技术中,首先需要确定与本地中央处理器发送的目标数据对应的加密码,并基于所述加密码以及所述目标数据生成目标黄金序列;然后对所述目标黄金序列进行双边采样,以得到上升沿采样数据以及下降沿采样数据,将所述上升沿采样数据以及所述下降沿采样数据发送至预设先进先出队列;通过所述预设先进先出队列基于预设相位差以及预设时钟频率将所述上升沿采样数据以及所述下降沿采样数据发送至本地数据拼接组件;并通过所述本地数据拼接组件基于预设第一高速时钟接收所述上升沿采样数据以及所述下降沿采样数据,并对所述上升沿采样数据以及所述下降沿采样数据进行拼接,得到目标拼接数据;最后通过所述本地数据拼接组件基于所述预设第一高速时钟将所述目标拼接数据发送至本地解密组件,以便所述本地解密组件基于预设第二高速时钟以及所述加密码对所述目标拼接数据进行解密。由此可见,通过本技术的方法,在接收到fpga芯片本地的中央处理器发送的目标数据后,需要确定与目标数据对应的加密码,并基于加密码以及目标数据生成黄金序列,然后对黄金序列进行双边采样,并将采样得到的数据发送至预设的先进先出队列,以便先进先出队列基于预设相位差以及预设时钟频率将采样频率发送至本地的数据拼接组件,以便对采样数据进行拼接,并基于第一高速时钟将拼接数据发送至本地解密组件,以边本地解密组件通过第二高速时钟对数据进行解密。这样一来,可以在保证信息安全的情况下有效对数据的处理流程进行加速,提高芯片的工作频率,进而提高芯片的处理效率。

- 还没有人留言评论。精彩留言会获得点赞!