一种图像任意剪裁的装置及方法与流程

本发明涉及视频图像处理,具体涉及一种图像任意剪裁的装置及方法。

背景技术:

1、在视频图像处理领域,通常摄像头输出的图像尺寸大于显示屏的显示尺寸,如果不做处理,显示屏是不能显示出图像来的,这就需要对输入图像进行先裁剪,然后降频处理,才能在显示屏上进行显示。

2、降频处理要用到帧缓存,因为图像比较大,通常用到的缓存也比较大,在fpga处理帧缓存时,其内部bram无法存储这么大的图片,这就要借助外部存储如ddr、falsh、eerom等。

3、当fpga通过自己设计的接口来读写外部存储器时,需要用到比较复杂的设计,耗时长,稳定性需要长时间的测试。因此,现有技术难以高效地同时实现剪裁和帧缓存。

技术实现思路

1、有鉴于此,有必要提供一种图像任意剪裁的装置及方法,能够简单高效地同时实现剪裁和帧缓存。为了实现上述目的,本发明提供了如下技术方案:

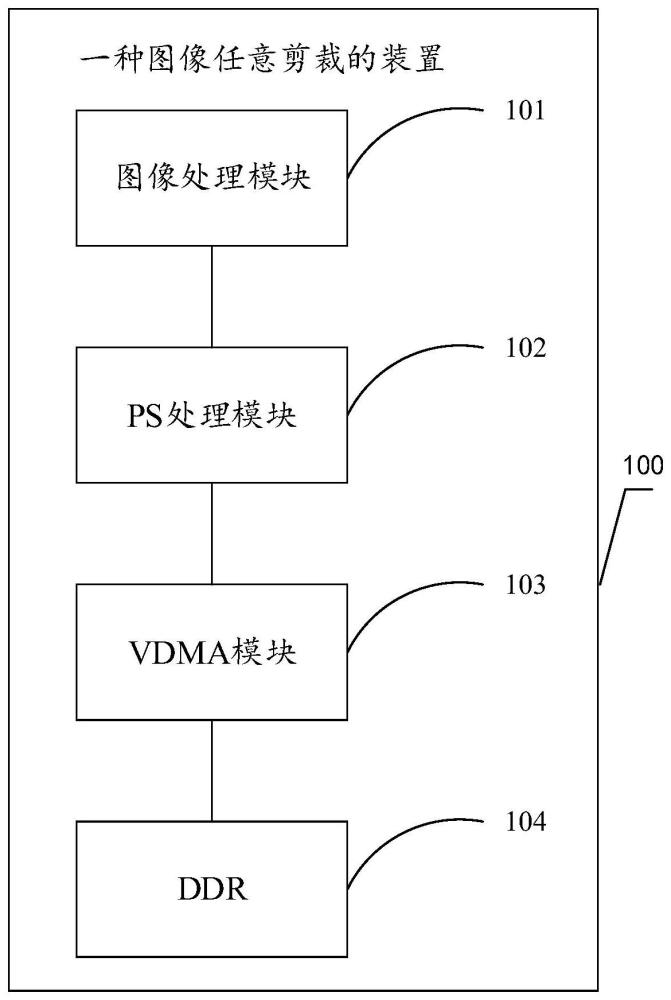

2、第一方面,本发明提供了一种图像任意剪裁的装置,包括:

3、图像处理模块,用于获取视频流数据,基于所述视频流数据得到axi4-stream数据流信号并发送;

4、ps处理模块,用于获取vdma模块的配置数据,并转发所述vdma模块的配置数据;

5、vdma模块,与所述图像处理模块和所述ps处理模块通信连接,用于接收所述axi4-stream数据流信号和所述配置数据,并对所述axi4-stream数据流信号进行数据检测和控制,得到输入二维矩阵,基于所述配置数据分别配置vdma模块的写通道和读通道,并基于配置成功的写通道将输入二维矩阵按照配置设定存入像素的起始地址发送至ddr,并基于配置成功的读通道按照配置设定像素的读取地址读取ddr中的存储数据,得到图像剪裁数据;

6、ddr,与所述vdma模块通信连接,用于降频存储所述配置成功的写通道发送的所述输入二维矩阵,得到存储数据。

7、可选的,所述装置,还包括:视频输出控制模块和外部显示屏;

8、所述视频输出控制模块,与所述vdma模块通信连接,用于对所述配置成功的读通道按照配置设定像素的读取地址读取ddr中的存储数据进行读出控制,得到图像裁剪数据并发送;

9、所述外部显示屏,与所述视频输出控制模块通信连接,用于接收所述图像剪裁数据,并基于所述图像剪裁数据通过所述外部显示屏显示。

10、可选的,所述视频输出控制模块,还用于获取所述外部显示屏的行场参数,基于所述外部显示屏的行场参数得到行场时序,基于所述行场时序对所述配置成功的读通道按照配置设定像素的读取地址读取ddr中的存储数据进行读出控制,得到图像剪裁数据并发送。

11、可选的,所述图像处理模块,包括:mipi数据接收模块和isp图像处理模块;

12、所述mipi数据接收模块,用于基于所述视频流数据进行信号处理,得到raw数据并发送;

13、所述isp图像处理模块,与所述mipi数据接收模块通信连接,用于接收raw数据,并基于所述raw数据进行解压缩、降噪处理及色调调整,得到axi4-stream数据流信号。

14、可选的,所述mipi数据接收模块,用于基于所述视频流数据进行信号分离,得到差分信号,基于所述差分信号进行同步、解码以及转换处理,得到raw数据。

15、可选的,所述vdma模块,包括缓存单元;

16、所述缓存单元,用于对所述axi4-stream数据流信号进行缓存操作,得到暂存数据。

17、可选的,所述vdma模块,还包括状态控制检测单元,所述状态检测单元,与所述缓存单元通信连接,用于接收所述暂存数据,并基于所述暂存数据进行数据检测和控制,得到输入二维矩阵。

18、可选的,所述vdma模块,还包括axi4-memory map接口;

19、所述axi4-memory map接口,用于基于所述配置成功的写通道将输入二维矩阵按照配置设定存入像素的起始地址发送至ddr。

20、可选的,所述基于配置成功的写通道将输入二维矩阵按照配置设定存入像素的起始地址发送至ddr,并基于配置成功的读通道按照配置设定像素的读取地址读取ddr中的存储数据,得到图像剪裁数据,包括:所述按照配置设定存入像素的起始地址与所述按照配置设定像素的读取地址不一致,从而得到图像剪裁数据。

21、第二方面,本发明还提供了一种图像任意剪裁的方法,所述方法包括:

22、基于图像处理模块获取视频流数据,基于所述视频流数据得到axi4-stream数据流信号;

23、基于ps处理模块获取vdma模块的配置数据,并转发所述vdma模块的配置数据;

24、基于vdma模块接收所述axi4-stream数据流信号和所述配置数据,并对所述axi4-stream数据流信号进行数据检测和控制,得到输入二维矩阵,基于所述配置数据分别配置vdma模块的写通道和读通道,并基于配置成功的写通道将输入二维矩阵按照配置设定存入像素的起始地址发送至ddr;

25、基于ddr进行降频存储所述配置成功的写通道发送的所述输入二维矩阵,得到存储数据;

26、基于vdma模块对配置成功的读通道按照配置设定像素的读取地址读取ddr中的存储数据,得到图像剪裁数据。

27、采用上述实现方式的有益效果是:本发明提供了一种图像任意剪裁的装置,装置包括:图像处理模块,用于获取视频流数据,基于所述视频流数据得到axi4-stream数据流信号并发送,ps处理模块,用于获取vdma模块的配置数据,并转发所述vdma模块的配置数据,vdma模块,与所述图像处理模块和所述ps处理模块通信连接,用于接收所述axi4-stream数据流信号和所述配置数据,并对所述axi4-stream数据流信号进行数据检测和控制,得到输入二维矩阵,基于所述配置数据分别配置vdma模块的写通道和读通道,并基于配置成功的写通道将输入二维矩阵按照配置设定存入像素的起始地址发送至ddr,并基于配置成功的读通道按照配置设定像素的读取地址读取ddr中的存储数据,得到图像剪裁数据,ddr,与所述vdma模块通信连接,用于降频存储所述配置成功的写通道发送的所述输入二维矩阵,得到存储数据。本技术通过提出一种图像任意剪裁的装置,该装置包括:图像处理模块、ps处理模块、vdma模块及ddr之间进行信息传输实现对图像的任意剪裁,具体的信息传输过程如下,图像处理模块,用于获取视频流数据,基于所述视频流数据得到axi4-stream数据流信号并发送至ps处理模块,ps处理模块,用于获取vdma模块的配置数据,并转发所述vdma模块的配置数据,vdma模块,与所述图像处理模块和所述ps处理模块通信连接,用于接收所述axi4-stream数据流信号和所述配置数据,并对所述axi4-stream数据流信号进行数据检测和控制,得到输入二维矩阵,基于所述配置数据分别配置vdma模块的写通道和读通道,并基于配置成功的写通道将输入二维矩阵按照配置设定存入像素的起始地址发送至ddr,并基于配置成功的读通道按照配置设定像素的读取地址读取ddr中的存储数据,得到图像剪裁数据,ddr,与所述vdma模块通信连接,用于降频存储所述配置成功的写通道发送的所述输入二维矩阵,得到存储数据。相比于现有技术,本技术提出了一种图像任意剪裁的装置,能够简单高效的同时实现剪裁和帧缓存。

- 还没有人留言评论。精彩留言会获得点赞!