一种基于FPGA的相对群时延测量方法及装置与流程

本发明属于跳频通信系统,尤其涉及一种基于fpga的相对群时延测量方法及装置。

背景技术:

1、目前,对于跳频通信系统,由于不同设备在不同频点信号通过发射通道或接收通道的时延不同,如果不单独进行时延补偿会导致每台套的通信设备之间通信灵敏度不一致,严重的情况下整个系统误码恶化,在接收端无法正确解调出发射机的信息,这就需要一套精度达ns级别的测量系统,来测试补偿系统的相对群时延,保证设备发射天线口及送入解调的信号各频点的相位能够对齐。

2、测量群时延常见的方法有示波器法、相位法和调制法,示波器法需要手动测试,人眼观察相位翻转转点,效率低下,测量误差取决于示波器的采样率和人为误差;相位法主要采用矢量网络分析仪,通过相位的变化得到时延,但是无法直接应用于跳频通信系统的发射通道和接收通道,需要加入混频器使输入和输出同频,成本高、校准过程繁琐、灵活性不好;调制法的原理是利用am/fm/pm调制解调,只有当调制信号频率远小于载波频率,在解调端测量包络时延即为群时延,此外,需要额外的相位求取单元,复杂程度高,应用场景有局限性,无法直接应用于多通道多频点的跳频通信系统。

技术实现思路

1、为了解决现有技术中的技术问题,本发明提供了一种基于fpga的相对群时延测量方法及装置。

2、本发明第一方面公开的基于fpga的相对群时延测量装置,包括时延校准辅助设备、设置于待测设备中的数字板卡处理单元和主控上位机;待测设备包括第一通信设备和第二通信设备;

3、所述时延校准辅助设备中设置有数字板卡处理单元,所述时延校准辅助设备的数字板卡处理单元和待测设备的数字板卡处理单元均包括fpga芯片、通信模块、adc模块和dac模块;在时延校准辅助设备、待测设备中,fpga芯片通过通信模块与主控上位机通信,dac模块输入端和adc模块输出端与fpga芯片相连;时延校准辅助设备中的dac模块输出端直接接入天线口,每一待测设备中的dac模块输出端和adc模块输入端分别与待测设备中的发射通道、接收通道相连;

4、测量待测设备接收通道的绝对群时延时,时延校准辅助设备的天线口与第一通信设备的天线口、第二通信设备的天线口通过射频交换网络内部的三通连接器相连,时延校准辅助设备处于发射状态,第一通信设备和第二通信设备处于接收状态;

5、测量待测设备发射通道的绝对群时延时,第一通信设备的天线口、第二通信设备的天线口通过射频交换网络内部的选通开关相连构成通信回路,第一通信设备和第二通信设备按时隙表的不同时刻处于发射状态或接收状态;

6、所述时延校准辅助设备的数字板卡处理单元和待测设备的数字板卡处理单元中的fpga芯片均包括参数处理模块、时延检测模块、调制模块,参数处理模块通过spi接口与对应的待测设备的发射通道、接收通道通信,配置待测设备的发射状态和接收状态;发射状态下,启动调制模块产生某一频率的bpsk多跳脉冲信号,首跳与时隙脉冲上升沿对齐,经时延校准辅助设备dac模块上变频到对应频点,或是待测设备发射通道上变频到对应频点信号,并将其功率放大;接收状态下,待测设备接收通道将对应频点信号功率放大、下变频为基带信号,并启动时延检测模块对接收到的基带信号进行处理,得到当下频点各通道的绝对群时延,遍历频点后得到各频点的绝对群时延。

7、进一步地,所述主控上位机包括参数配置模块、相对群时延计算模块和时延校准文件生成模块;所述参数配置模块用于读取参数模板文件中的频点参数、时延校准辅助设备和待测设备的ip地址及收发状态、射频交换网络参数,下发初始化配置,加载时延校准辅助设备和待测设备的状态,执行测量过程;所述相对群时延计算模块,用于对获取的测量数据进行处理,离群处理不合理的数据,计算各通道之间的时延差及各频点时延差,得到待测设备的各通道各频点相对群时延;所述时延校准文件生成模块,用于将以上处理的数据生成dat、coe、txt、ini或csv文件,应用于发射补偿与接收补偿。

8、进一步地,所述时延校准辅助设备已实现时延校准,对调制模块生成的基带信号通过dac模块及上变频后的各频点而产生的时延差进行补偿,使天线口发送出的信号各频点与时隙脉冲发射时刻以及相位对齐。

9、进一步地,所述待测设备发射通道时延为跳频通信设备的dac模块时延、信道模块的发射通道时延、功放模块的发射通道时延之和;所述待测设备接收通道时延为跳频通信设备的adc模块时延、信道模块的接收通道时延、功放模块的接收通道时延之和。

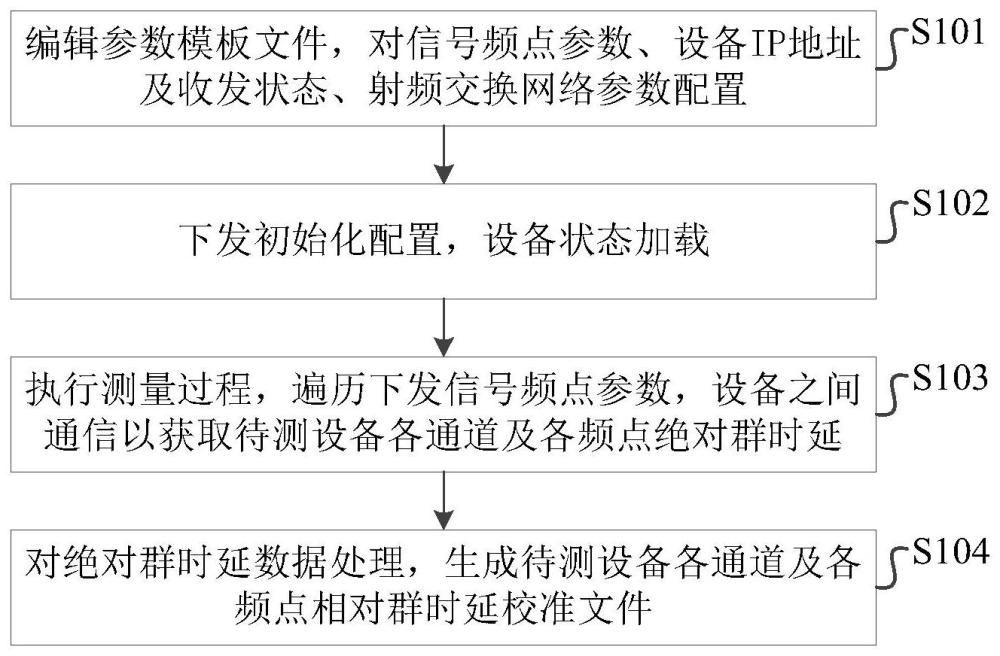

10、本发明第二方面公开的测量装置实现的相对群时延测量方法,包括以下步骤:

11、s1、在主控上位机中,编辑参数模板文件,对信号频点参数、时延校准辅助设备和待测设备的ip地址及收发状态、射频交换网络参数进行配置;

12、s2、在主控上位机中,下发初始化配置,对时延校准辅助设备和待测设备状态进行加载;

13、s3、在主控上位机中,执行测量过程,遍历下发信号频点参数,时延校准辅助设备和待测设备之间通信以获取待测设备各通道及各频点绝对群时延;

14、s4、在主控上位机中,对绝对群时延数据进行处理,生成待测设备各通道及各频点相对群时延校准文件。

15、进一步地,跳脉冲的脉冲宽度内可以为bpsk、qpsk、16qam信号,脉冲间隔内无信号输出,首跳与时隙脉冲对齐;若接收通道存在8路时,使用一个时隙发送8跳的脉冲信号波形,符号速率为100/48msps,每跳符号数510,则每跳持续时间为244.8us,脉冲宽度为219.36us,脉冲间隔为25.44us。

16、进一步地,幅度及能量归一化使用3bit量化的规则,所述3bit量化的规则为:保留符号位,符号位占1bit,剩余的2bit值为1或3;其中1和3的取值为:若基带信号实部的绝对值大于虚部的绝对值,则实部量化为3,虚部量化为1,反之亦然。

17、进一步地,当接收通道存在多路时,各通道与发射端各跳依次一一对应,利用pn序列相关的特性,将接收到的信号pn序列与本地产生的pn序列作为参考信号进行相关运算,得到一个相关函数,其表达式如下:

18、

19、其中,ω(k)表示为相关结果,u(j)为3bit量化后的基带信号,v(k―j+1)为本地pn序列,j为第几个相关序列,n为相关序列长度,k为第几个输入信号的编号;

20、相关函数的峰值位置与时隙脉冲之间的差值作为测量通道的绝对群时延,不同通道的峰值位置不一样,通过在fpga中计数得到多个通道的绝对群时延toa1~toa n,则第一通信设备接收通道绝对群时延为r1_toa 1~r1_toa n,发射通道绝对群时延为s1_toa 1~s1_toa n,其中,s1_toa 1=a12_toa 1-r2_toa 1,s1_toa n=a12_toa n-r2_toa n。

21、进一步地,发射的跳频序列有n个,对应的发射频点为f1~fn,当信号通过接收通道抵达到待测设备的数字板卡处理单元fpga芯片时,由于接收通道滤波器的不同频点时延特性不一样,存在不同的时间延迟,随着频点的频率越高时间延迟越低,总体趋于线性,这里不同接收频点的绝对群延迟值为delay1~delay n,则第一通信设备接收通道1各频点绝对群时延为r1_toa1_delay1~r1_toa1_delay n,发射通道1各频点绝对群时延为s1_toa1_delay1~s1_toa1_delayn,

22、其中s1_toa1_delay1=a12_toa1_delay1-r2_toa 1_delay1,s1_toa1_delay n=a12_toa1_delay n-r2_toa1_delay n。

23、进一步地,主控上位机计算各通道相对群时延时,以第一个通道为基准,其它通道与第一通道做差值,则第一通信设备接收通道各通道间相对群时延时△r1_toa1~△r1_toa n,

24、其中△r1_toa1=0,△r1_toa n=r1_toa n-r1_toa 1;

25、发射通道各通道间相对群时延时△s1_toa1~△s1_toa n,其中△s1_toa1=0,△s1_toa n=s1_toa n-s1_toa 1;

26、主控上位机计算各频点相对群时延时,以最后一个频点为基准,其它频点与最后一个频点做差值,则第一通信设备接收通道1各频点相对群时延△r1_toa1_delay1~△r1_toa1_delay n,其中△r1_toa1_delay n=0,△r1_toa1_delay1=r1_toa1_delay1-r1_toa1_delay n,发射通道1各频点相对群时延△s1_toa1_delay1~△s1_toa1_delay n,其中△s1_toa1_delay n=0,

27、△s1_toa1_delay1=s1_toa1_delay1-s1_toa1_delay n;

28、fpga芯片读取时延校准文件生成模块生成的校准文件对发射通道与接收通道时延补偿,信号输出至dac模块前及信号输入至adc模块后,在fpga中加入bram,bram写使能一直拉高,一直写入数据,在每一跳数据前面的保护间隔,做一次读地址的调整,读地址的调整值为延时值,不会丢失有效数据;接收通道延时调整,数据为3bit量化后,各个通道延迟调整后做相关;各频点数据延时调整,数据为主收下变频后的数据,延时调整后输出至后级解调模块。

29、与现有技术相比,本发明具有如下有益效果:

30、本发明基于可编程逻辑器件fpga,集成了参数配置与分发、信号产生和时延检测功能,以及与主控上位机通信的功能,能用于测量待测设备发射通道和接收通道的绝对群时延,并且可同时并行进行多台套的多个发射通道和接收通道测量,提高了时延测量的效率;测量精度主要取决于adc模块的采样率精度、fpga芯片调制模块的符号速率和时钟源精度,可根据需求调整相应模块以达到对应的精度,如在adc的采样率为100mhz、符号速率100/48msps、时钟源为0.1ppm下,fpga芯片时延检测模块的时钟频率为100mhz,测量精度约为10ns;采用主控上位机,能方便、灵活地对测试信号频点做出调整,编辑好参数配置模板后就可执行自动化测试,简化了测试复杂度,避免了人为误差;在主控上位机计算的相对群时延并生成校准文件,各频点通过测量装置中线缆及射频交换网络的绝对群时延可视为一个固定值,在计算相对群时延时就会被剔除掉,减少了测量的误差,生成校准文件可直接应用于待测设备发射通道和接收通道的时延补偿,能提高接收端符号定位精度;在跳频通信设备的批量化生产中,待测设备的数字板卡处理单元的逻辑能直接运行于跳频通信设备的数字板卡之上,时延测量时只需将设备切换为测量状态,无需额外配备仪器、节省成本,有效节省硬件资源。

- 还没有人留言评论。精彩留言会获得点赞!