一种熔融石英电视、近红外双波段分光膜及其制备方法与流程

[0001]

本发明属于光学薄膜制造技术领域,具体涉及一种熔融石英电视、近红外双波段分光膜及其制备方法。

背景技术:

[0002]

目前机载光电产品朝着体积小,重量轻,探测距离远、分辨精度高的方向发展,熔融石英基底分光镜为机载光电系统中关键零件,镀分光膜后可实现同路光束一部分能量反射另一部分透射,为实现该光学特性,熔融石英基底表面要求镀制0.6μm~0.9μm、0.95μm~1.7μm两个波段的分光膜。

技术实现要素:

[0003]

有鉴于此,本发明提供一种熔融石英电视、近红外双波段分光膜的膜系结构及制备方法。由熔融石英基底和在45

°

入射角0.6μm~0.9μm波段透过率≤2%、0.95μm~1.7μm近红外波段透射率≥97%分光膜两部分构成。

[0004]

为了达到上述技术目的,本发明所采用的具体技术方案为:

[0005]

本发明提出一种熔融石英电视、近红外双波段分光膜,所述分光膜的膜系为82层,奇数膜层均为ta2o5,偶数膜层均为sio2,第1层几何厚度为35.11

±

2nm,第2层几何厚度为141.67

±

2nm,第3层几何厚度为81.43

±

2nm,第4层几何厚度为73.17

±

2nm,第5层几何厚度为70.56

±

2nm,第6层几何厚度为87.08

±

2nm,第7层几何厚度为79.81

±

2nm,第8层几何厚度为140.10

±

2nm,第9层几何厚度为89.87

±

2nm,第10层几何厚度为98.01

±

2nm,第11层几何厚度为78.13

±

2nm,第12层几何厚度为66.83

±

2nm,第13层几何厚度为79.01

±

2nm,第14层几何厚度为124.75

±

2nm,第15层几何厚度为87.28

±

2nm,第16层几何厚度为134.35

±

2nm,第17层几何厚度为87.12

±

2nm,第18层几何厚度为96.72

±

2nm,第19层几何厚度为72.86

±

2nm,第20层几何厚度为89.18

±

2nm,第21层几何厚度为78.60

±

2nm,第22层几何厚度为105.08

±

2nm,第23层几何厚度为71.12

±

2nm,第24层几何厚度为114.65

±

2nm,第25层几何厚度为83.34

±

2nm,第26层几何厚度为127.92

±

2nm,第27层几何厚度为89.16

±

2nm,第28层几何厚度为190.05

±

2nm,第29层几何厚度为39.04

±

2nm,第30层几何厚度为303.88

±

2nm,第31层几何厚度为68.86

±

2nm,第32层几何厚度为137.71

±

2nm,第33层几何厚度为106.13

±

2nm,第34层几何厚度为185.28

±

2nm,第35层几何厚度为50.99

±

2nm,第36层几何厚度为219.17

±

2nm,第37层几何厚度为74.20

±

2nm,第38层几何厚度为73.37

±

2nm,第39层几何厚度为378.08

±

2nm,第40层几何厚度为74.28

±

2nm,第41层几何厚度为91.76

±

2nm,第42层几何厚度为151.33

±

2nm,第43层几何厚度为95.75

±

2nm,第44层几何厚度为149.86

±

2nm,第45层几何厚度为98.96

±

2nm,第46层几何厚度为156.10

±

2nm,第47层几何厚度为121.01

±

2nm,第48层几何厚度为109.27

±

2nm,第49层几何厚度为130.01

±

2nm,第50层几何厚度为148.98

±

2nm,第51层几何厚度为95.70

±

2nm,第52层几何厚度为155.69

±

2nm,第53层几何厚度为101.57

±

2nm,第54层几何厚度为153.54

±

2nm,第55层几何厚度为

98.18

±

2nm,第56层几何厚度为90.45

±

2nm,第57层几何厚度为96.30

±

2nm,第58层几何厚度为41.98

±

2nm,第59层几何厚度为109.03

±

2nm,第60层几何厚度为120.67

±

2nm,第61层几何厚度为90.23

±

2nm,第62层几何厚度为156.79

±

2nm,第63层几何厚度为102.25

±

2nm,第64层几何厚度为156.97

±

2nm,第65层几何厚度为88.72

±

2nm,第66层几何厚度为112.38

±

2nm,第67层几何厚度为263.57

±

2nm,第68层几何厚度为45.53

±

2nm,第69层几何厚度为108.66

±

2nm,第70层几何厚度为159.91

±

2nm,第71层几何厚度为98.47

±

2nm,第72层几何厚度为141.75

±

2nm,第73层几何厚度为91.14

±

2nm,第74层几何厚度为152.12

±

2nm,第75层几何厚度为93.48

±

2nm,第76层几何厚度为30.60

±

2nm,第77层几何厚度为283.02

±

2nm,第78层几何厚度为136.79

±

2nm,第79层几何厚度为80.00

±

2nm,第80层几何厚度为135.57

±

2nm,第81层几何厚度为109.01

±

2nm,第82层几何厚度为275.51

±

2nm。

[0006]

进一步的,所述分光膜的第1层几何厚度为35.11nm,第2层几何厚度为141.67nm,第3层几何厚度为81.43nm,第4层几何厚度为73.17nm,第5层几何厚度为70.56nm,第6层几何厚度为87.08nm,第7层几何厚度为79.81nm,第8层几何厚度为140.10nm,第9层几何厚度为89.87nm,第10层几何厚度为98.01nm,第11层几何厚度为78.13nm,第12层几何厚度为66.83nm,第13层几何厚度为79.01nm,第14层几何厚度为124.75nm,第15层几何厚度为87.28nm,第16层几何厚度为134.35nm,第17层几何厚度为87.12nm,第18层几何厚度为96.72nm,第19层几何厚度为72.86nm,第20层几何厚度为89.18nm,第21层几何厚度为78.60nm,第22层几何厚度为105.08nm,第23层几何厚度为71.12nm,第24层几何厚度为114.65nm,第25层几何厚度为83.34nm,第26层几何厚度为127.92nm,第27层几何厚度为89.16nm,第28层几何厚度为190.05nm,第29层几何厚度为39.04nm,第30层几何厚度为303.88nm,第31层几何厚度为68.86nm,第32层几何厚度为137.71nm,第33层几何厚度为106.13nm,第34层几何厚度为185.28nm,第35层几何厚度为50.99nm,第36层几何厚度为219.17nm,第37层几何厚度为74.20nm,第38层几何厚度为73.37nm,第39层几何厚度为378.08nm,第40层几何厚度为74.28nm,第41层几何厚度为91.76nm,第42层几何厚度为151.33nm,第43层几何厚度为95.75nm,第44层几何厚度为149.86nm,第45层几何厚度为98.96nm,第46层几何厚度为156.10nm,第47层几何厚度为121.01nm,第48层几何厚度为109.27nm,第49层几何厚度为130.01nm,第50层几何厚度为148.98nm,第51层几何厚度为95.70nm,第52层几何厚度为155.69nm,第53层几何厚度为101.57nm,第54层几何厚度为153.54nm,第55层几何厚度为98.18nm,第56层几何厚度为90.45nm,第57层几何厚度为96.30nm,第58层几何厚度为41.98nm,第59层几何厚度为109.03nm,第60层几何厚度为120.67nm,第61层几何厚度为90.23nm,第62层几何厚度为156.79nm,第63层几何厚度为102.25nm,第64层几何厚度为156.97nm,第65层几何厚度为88.72nm,第66层几何厚度为112.38nm,第67层几何厚度为263.57nm,第68层几何厚度为45.53nm,第69层几何厚度为108.66nm,第70层几何厚度为159.91nm,第71层几何厚度为98.47nm,第72层几何厚度为141.75nm,第73层几何厚度为91.14nm,第74层几何厚度为152.12nm,第75层几何厚度为93.48nm,第76层几何厚度为30.60nm,第77层几何厚度为283.02nm,第78层几何厚度为136.79nm,第79层几何厚度为80.00nm,第80层几何厚度为135.57nm,第81层几何厚度为109.01nm,第82层几何厚度为275.51nm。

[0007]

进一步的,本发明还提出上述熔融石英电视、近红外双波段分光膜的制备方法,包

括以下步骤:

[0008]

1)镀制第1层膜层:取ta2o5膜料由电阻蒸发源在真空腔室内进行蒸镀,蒸镀时,蒸镀环境的真空度≤1.0

×

10-3

pa,蒸镀速率为0.4nm/s~0.5nm/s;

[0009]

2)镀制第2层膜层:取sio2膜料由电阻蒸发源在真空腔室内进行蒸镀,蒸镀时,真空度≤1.0

×

10-3

pa,蒸镀速率为0.6nm/s~0.7nm/s;

[0010]

3)重复步骤1)和2),交替镀制第3~82层膜层;

[0011]

4)镀制完毕后冷却在真空腔室内的温度使其不大于45℃;

[0012]

其中:所述分光膜的镀制基底为熔融石英材料。

[0013]

进一步的,在步骤1)之前还包括基底预处理步骤:对所述镀制基底进行清洗和烘烤。

[0014]

进一步的,所述清洗的具体方法为:采用清洁剂对所述基底进行清洗。

[0015]

进一步的,所述烘烤的具体方法为:将所述基底置于所述真空腔室内中,抽真空至真空度≤1.0

×

10-3

pa,在140~150℃下保温1~2小时。

[0016]

采用上述技术方案,本发明能够带来以下有益效果:

[0017]

本发明采用膜层设计软件设计并优化熔融石英电视、近红外双波段分光膜膜系,该膜系在45

°

入射时,0.6μm~0.9μm电视波段透过率平均设计值≤2%,测试平均值为1.8%;0.95μm~1.7μm近红外波段透射率设计值≥97%,测试值为97.6%。

附图说明

[0018]

为了更清楚地说明本公开实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

[0019]

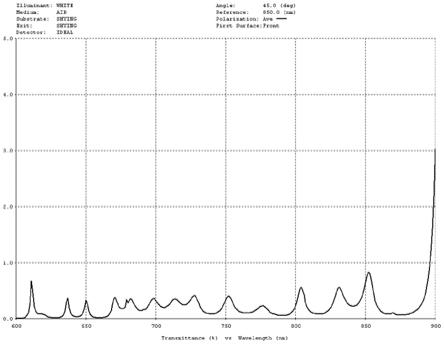

图1为本发明提供的熔融石英基底在0.6μm~0.9μm电视波段,45

°

入射角范围内的透过率设计曲线图;

[0020]

图2为本发明提供的熔融石英基底在0.95μm~1.7μm近红外波段,45

°

入射角范围内的透过率设计曲线图。

具体实施方式

[0021]

下面结合附图对本公开实施例进行详细描述。

[0022]

以下通过特定的具体实例说明本公开的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本公开的其他优点与功效。显然,所描述的实施例仅仅是本公开一部分实施例,而不是全部的实施例。本公开还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本公开的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。基于本公开中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本公开保护的范围。

[0023]

要说明的是,下文描述在所附权利要求书的范围内的实施例的各种方面。应显而易见,本文中所描述的方面可体现于广泛多种形式中,且本文中所描述的任何特定结构及/或功能仅为说明性的。基于本公开,所属领域的技术人员应了解,本文中所描述的一个方面

可与任何其它方面独立地实施,且可以各种方式组合这些方面中的两者或两者以上。举例来说,可使用本文中所阐述的任何数目个方面来实施设备及/或实践方法。另外,可使用除了本文中所阐述的方面中的一或多者之外的其它结构及/或功能性实施此设备及/或实践此方法。

[0024]

还需要说明的是,以下实施例中所提供的图示仅以示意方式说明本公开的基本构想,图式中仅显示与本公开中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

[0025]

另外,在以下描述中,提供具体细节是为了便于透彻理解实例。然而,所属领域的技术人员将理解,可在没有这些特定细节的情况下实践所述方面。

[0026]

在本发明的一个实施例中,提出一种熔融石英电视、近红外双波段分光膜,分光膜的膜系为82层,奇数膜层均为ta2o5,偶数膜层均为sio2,第1层几何厚度为35.11

±

2nm,第2层几何厚度为141.67

±

2nm,第3层几何厚度为81.43

±

2nm,第4层几何厚度为73.17

±

2nm,第5层几何厚度为70.56

±

2nm,第6层几何厚度为87.08

±

2nm,第7层几何厚度为79.81

±

2nm,第8层几何厚度为140.10

±

2nm,第9层几何厚度为89.87

±

2nm,第10层几何厚度为98.01

±

2nm,第11层几何厚度为78.13

±

2nm,第12层几何厚度为66.83

±

2nm,第13层几何厚度为79.01

±

2nm,第14层几何厚度为124.75

±

2nm,第15层几何厚度为87.28

±

2nm,第16层几何厚度为134.35

±

2nm,第17层几何厚度为87.12

±

2nm,第18层几何厚度为96.72

±

2nm,第19层几何厚度为72.86

±

2nm,第20层几何厚度为89.18

±

2nm。第21层几何厚度为78.60

±

2nm,第22层几何厚度为105.08

±

2nm,第23层几何厚度为71.12

±

2nm,第24层几何厚度为114.65

±

2nm,第25层几何厚度为83.34

±

2nm,第26层几何厚度为127.92

±

2nm,第27层几何厚度为89.16

±

2nm,第28层几何厚度为190.05

±

2nm,第29层几何厚度为39.04

±

2nm,第30层几何厚度为303.88

±

2nm。第31层几何厚度为68.86

±

2nm,第32层几何厚度为137.71

±

2nm,第33层几何厚度为106.13

±

2nm,第34层几何厚度为185.28

±

2nm,第35层几何厚度为50.99

±

2nm,第36层几何厚度为219.17

±

2nm,第37层几何厚度为74.20

±

2nm,第38层几何厚度为73.37

±

2nm,第39层几何厚度为378.08

±

2nm,第40层几何厚度为74.28

±

2nm,第41层几何厚度为91.76

±

2nm,第42层几何厚度为151.33

±

2nm,第43层几何厚度为95.75

±

2nm,第44层几何厚度为149.86

±

2nm,第45层几何厚度为98.96

±

2nm,第46层几何厚度为156.10

±

2nm,第47层几何厚度为121.01

±

2nm,第48层几何厚度为109.27

±

2nm,第49层几何厚度为130.01

±

2nm,第50层几何厚度为148.98

±

2nm,第51层几何厚度为95.70

±

2nm,第52层几何厚度为155.69

±

2nm,第53层几何厚度为101.57

±

2nm,第54层几何厚度为153.54

±

2nm,第55层几何厚度为98.18

±

2nm,第56层几何厚度为90.45

±

2nm,第57层几何厚度为96.30

±

2nm,第58层几何厚度为41.98

±

2nm,第59层几何厚度为109.03

±

2nm,第60层几何厚度为120.67

±

2nm,第61层几何厚度为90.23

±

2nm,第62层几何厚度为156.79

±

2nm,第63层几何厚度为102.25

±

2nm,第64层几何厚度为156.97

±

2nm,第65层几何厚度为88.72

±

2nm,第66层几何厚度为112.38

±

2nm,第67层几何厚度为263.57

±

2nm,第68层几何厚度为45.53

±

2nm,第69层几何厚度为108.66

±

2nm,第70层几何厚度为159.91

±

2nm,第71层几何厚度为98.47

±

2nm,第72层几何厚度为141.75

±

2nm,第73层几何厚度为91.14

±

2nm,第74层几何厚度为152.12

±

2nm,第75层几何厚度为93.48

±

2nm,第76层几何厚度为30.60

±

2nm,第77层几何厚度为283.02

±

2nm,第78层几何厚度为136.79

±

2nm,第79层几何厚度为80.00

±

2nm,第80层几何厚度为135.57

±

2nm,第81层几何厚度为109.01

±

2nm,第82层几何厚度为275.51

±

2nm。

[0027]

在一个实施例中,分光膜的第1层几何厚度为35.11nm,第2层几何厚度为141.67nm,第3层几何厚度为81.43nm,第4层几何厚度为73.17nm,第5层几何厚度为70.56nm,第6层几何厚度为87.08nm,第7层几何厚度为79.81nm,第8层几何厚度为140.10nm,第9层几何厚度为89.87nm,第10层几何厚度为98.01nm,第11层几何厚度为78.13nm,第12层几何厚度为66.83nm,第13层几何厚度为79.01nm,第14层几何厚度为124.75nm,第15层几何厚度为87.28nm,第16层几何厚度为134.35nm,第17层几何厚度为87.12nm,第18层几何厚度为96.72nm,第19层几何厚度为72.86nm,第20层几何厚度为89.18nm。第21层几何厚度为78.60nm,第22层几何厚度为105.08nm,第23层几何厚度为71.12nm,第24层几何厚度为114.65nm,第25层几何厚度为83.34nm,第26层几何厚度为127.92nm,第27层几何厚度为89.16nm,第28层几何厚度为190.05nm,第29层几何厚度为39.04nm,第30层几何厚度为303.88nm。第31层几何厚度为68.86nm,第32层几何厚度为137.71nm,第33层几何厚度为106.13nm,第34层几何厚度为185.28nm,第35层几何厚度为50.99nm,第36层几何厚度为219.17nm,第37层几何厚度为74.20nm,第38层几何厚度为73.37nm,第39层几何厚度为378.08nm,第40层几何厚度为74.28nm,第41层几何厚度为91.76nm,第42层几何厚度为151.33nm,第43层几何厚度为95.75nm,第44层几何厚度为149.86nm,第45层几何厚度为98.96nm,第46层几何厚度为156.10nm,第47层几何厚度为121.01nm,第48层几何厚度为109.27nm,第49层几何厚度为130.01nm,第50层几何厚度为148.98nm,第51层几何厚度为95.70nm,第52层几何厚度为155.69nm,第53层几何厚度为101.57nm,第54层几何厚度为153.54nm,第55层几何厚度为98.18nm,第56层几何厚度为90.45nm,第57层几何厚度为96.30nm,第58层几何厚度为41.98nm,第59层几何厚度为109.03nm,第60层几何厚度为120.67nm,第61层几何厚度为90.23nm,第62层几何厚度为156.79nm,第63层几何厚度为102.25nm,第64层几何厚度为156.97nm,第65层几何厚度为88.72nm,第66层几何厚度为112.38nm,第67层几何厚度为263.57nm,第68层几何厚度为45.53nm,第69层几何厚度为108.66nm,第70层几何厚度为159.91nm,第71层几何厚度为98.47nm,第72层几何厚度为141.75nm,第73层几何厚度为91.14nm,第74层几何厚度为152.12nm,第75层几何厚度为93.48nm,第76层几何厚度为30.60nm,第77层几何厚度为283.02nm,第78层几何厚度为136.79nm,第79层几何厚度为80.00nm,第80层几何厚度为135.57nm,第81层几何厚度为109.01nm,第82层几何厚度为275.51nm。

[0028]

在一个实施例中,本发明还提出上述熔融石英电视、近红外双波段分光膜的制备方法,包括以下步骤:

[0029]

1)镀制第1层膜层:取ta2o5膜料由电阻蒸发源在真空腔室内进行蒸镀,蒸镀时,蒸镀环境的真空度≤1.0

×

10-3

pa,蒸镀速率为0.4nm/s~0.5nm/s;

[0030]

2)镀制第2层膜层:取sio2膜料由电阻蒸发源在真空腔室内进行蒸镀,蒸镀时,真空度≤1.0

×

10-3

pa,蒸镀速率为0.6nm/s~0.7nm/s;

[0031]

3)重复步骤1)和2),交替镀制第3~82层膜层;

[0032]

4)镀制完毕后冷却在真空腔室内的温度使其不大于45℃;

[0033]

其中:分光膜的镀制基底为熔融石英材料。

[0034]

在一个实施例中,在步骤1)之前还包括基底预处理步骤:对镀制基底进行清洗和烘烤。

[0035]

在一个实施例中,清洗的具体方法为:采用清洁剂对基底进行清洗。

[0036]

在一个实施例中,烘烤的具体方法为:将基底置于真空腔室内中,抽真空至真空度≤1.0

×

10-3

pa,在140~150℃下保温1~2小时。

[0037]

在一个实施例中,提出一种上述实施例中熔融石英电视、近红外双波段分光膜的制备方法,膜系制备过程中所用设备需配置高真空抽气系统、两组电阻蒸发源、光学膜厚控制仪、石英晶体膜厚控制装置、离子束辅助装置、加热烘烤装置和转速可调工件夹具。

[0038]

本实施例中,熔融石英电视、近红外双波段分光膜的膜系制备方法,包括以下步骤:

[0039]

一、准备工作

[0040]

清洁真空室、镀膜夹具、蒸发源挡板及离子源;

[0041]

在蒸发舟内装入ta2o5和sio2;

[0042]

更换石英晶振片;

[0043]

二、清洁零件

[0044]

零件为熔融石英基底;

[0045]

用脱脂棉蘸取醇醚混合液清洁零件表面;

[0046]

安装专用工装,并将零件装入真空室。

[0047]

三、膜层镀制

[0048]

关闭真空室,启动镀膜程序开始镀膜,具体如下:

[0049]

抽气、烘烤基底:将待镀零件置于高真空镀膜设备中,抽真空至≤1.0

×

10-3

pa,加热基底到150℃,保温2小时,再启动离子源对基底进行轰击5min;

[0050]

镀制第1层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0051]

镀制第2层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0052]

镀制第3层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0053]

镀制第4层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0054]

镀制第5层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0055]

镀制第6层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0056]

镀制第7层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0057]

镀制第8层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0058]

镀制第9层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0059]

镀制第10层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0060]

镀制第11层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0061]

镀制第12层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0062]

镀制第13层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0063]

镀制第14层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0064]

镀制第15层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0065]

镀制第16层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0066]

镀制第17层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0067]

镀制第18层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0068]

镀制第19层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0069]

镀制第20层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0070]

镀制第21层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0071]

镀制第22层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0072]

镀制第23层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0073]

镀制第24层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0074]

镀制第25层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0075]

镀制第26层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0076]

镀制第27层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0077]

镀制第28层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸

发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0078]

镀制第29层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0079]

镀制第30层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0080]

镀制第31层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0081]

镀制第32层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0082]

镀制第33层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0083]

镀制第34层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0084]

镀制第35层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0085]

镀制第36层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0086]

镀制第37层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0087]

镀制第38层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0088]

镀制第39层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0089]

镀制第40层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0090]

镀制第41层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0091]

镀制第42层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0092]

镀制第43层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0093]

镀制第44层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0094]

镀制第45层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0095]

镀制第46层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0096]

镀制第47层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0097]

镀制第48层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0098]

镀制第49层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0099]

镀制第50层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0100]

镀制第51层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0101]

镀制第52层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0102]

镀制第53层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0103]

镀制第54层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0104]

镀制第55层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0105]

镀制第56层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0106]

镀制第57层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0107]

镀制第58层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0108]

镀制第59层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0109]

镀制第60层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0110]

镀制第61层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0111]

镀制第62层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0112]

镀制第63层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0113]

镀制第64层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0114]

镀制第64层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0115]

镀制第66层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0116]

镀制第67层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,

蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0117]

镀制第68层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0118]

镀制第69层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0119]

镀制第70层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0120]

镀制第71层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0121]

镀制第72层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0122]

镀制第73层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0123]

镀制第74层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0124]

镀制第75层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0125]

镀制第76层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0126]

镀制第77层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0127]

镀制第78层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0128]

镀制第79层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0129]

镀制第80层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0130]

镀制第81层膜层:膜料ta2o5由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.4nm/s,膜层厚度由石英晶体膜厚测量装置控制;

[0131]

镀制第82层膜层:膜料sio2由电阻蒸发源进行蒸镀,蒸镀真空度≤1.0

×

10-3

pa,蒸发速率0.6m/s,膜层厚度由石英晶体膜厚测量装置控制;

[0132]

镀制完毕冷却真空室的温度低于45℃。

[0133]

取本实施例的膜系进行光学特性测试,测量结果如图1和图2所示,根据读取图1和图2的曲线,得出两组工作波段的透过率数据,如表1所示

[0134]

工作波段0.6μm~0.9μm0.95μm~1.7μm透过率1.8%97.6%

[0135]

表1

[0136]

从表1可见,实施例镀制的膜系45

°

入射时,对0.6μm~0.9μm平均透过率1.8%,对0.95μm~1.7μm近红外波段透射率为97.6%。满足熔融石英电视、近红外双波段分光膜光学

特性要求。

[0137]

以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1