一种MEMS加速度计的多级抗过载封装结构及方法与流程

一种mems加速度计的多级抗过载封装结构及方法

技术领域

1.本发明涉及一种mems加速度计的多级抗过载封装结构及方法,属于芯片封装技术领域,可应用于mems加速度计、mems陀螺仪等mems惯性仪表的封装,用于提高mems惯性仪表的抗高过载能力。

背景技术:

2.mems加速度计因其具有体积小、功耗低、寿命长、价格低廉及可批量化生产的特点,被广泛应用于航空航天、制导弹药等装备以及汽车、机器人及消费电子产品等领域。随着mems加速度计的快速发展,对其抗振动、抗过载等环境适应性要求越来越高。特别是应用在火炮、舰炮、电磁炮用制导弹药等方面,mems加速度计在载体发射、飞行过程都要承受很大的过载冲击,会达到上万g甚至达十万g乃至数十万g。由于mems加速度计主要放置于载体的端面或侧面,而其所受的过载冲击也集中在载体的运动方向,在这种情况下,为保证mems加速度计的正常工作,提高其x向和z方向的抗高过载特性显得尤为重要。

3.提高器件的抗过载能力可以从结构本身及后续封装环节进行设计研究,其中,封装对mems加速度计如何更好地克服环境状态改变对其性能的影响、从而提高环境适应性具有举足轻重的作用。由于传统管壳封装方式为简单的把被封装mems加速度计芯片直接粘结在管壳底部,当过载较大时,一方面被封装mems加速度计芯片与封装管壳的相对位移导致性能退化,另一方面,如没有外止档有效的卸载掉一定量级的高过载应力,易使敏感结构因承载传导过来的过载应力过大从而导致仪表失效。

技术实现要素:

4.本发明解决的技术问题是:克服现有技术的不足,提供一种mems加速度计的多级抗过载封装结构及方法,将mems加速度计和信号处理芯片可靠的互连并固定在封装管壳中,既能满足mems加速度计的稳定工作要求又能提高ems加速度计的抗过载能力。

5.本发明解决技术的方案是:一种mems加速度计的多级抗过载封装结构,该封装结构包括封装管壳、封装盖板、外止档、侧面应力缓冲层、上表面应力缓冲层;其中:

6.所述mems加速度计包括mems加速度计芯片和asic芯片,asic芯片用于mems加速度计芯片信号调理和采集,所述被封装mems加速度计芯片固定在封装管壳基底上;被封装mems加速度计芯片粘贴在封装管壳上;外止档固化在封装管壳基底上,外止档罩在被封装mems加速度计芯片上方,使得被封装mems加速度计芯片位于外止档内部,且所述被封装mems加速度计芯片和外止档之间留有抗过载间隙,用于限制被封装mems加速度计芯片在高过载环境下的位移改变量;所述被封装asic芯片粘结在外止档上表面;

7.所述被封装mems加速度计芯片的侧面和上表面涂覆有分布式布局的柔性聚合物作为应力缓冲层,分别记为侧面应力缓冲层和上表面应力缓冲层;在高过载情况下被封装mems加速度计芯片与外止档产生碰撞时,利用应力缓冲层的储存和耗散能量。

8.所述外止档结构为倒u型。

9.所述外止档选择陶瓷材料。

10.所述外止档通过第一粘结剂固化在封装管壳基底上;所述第一粘结剂采用平铺的方式粘接,且粘度越大越好。

11.所述外止档边缘设有光学观察窗,用以校准被封装mems加速度计芯片与外止档的相对位置。

12.所述侧面应力缓冲层和上表面应力缓冲层的厚度为微米量级。

13.所述被封装mems加速度计芯片和外止档之间的抗过载间隙取值范围为2

‑

5μm。

14.所述被封装asic芯片采用第二粘结剂粘结在外止档上表面;

15.所述第二粘结剂选取asic专用粘结剂,以平铺的方式进行被封装asic芯片和外止档的粘结固定。

16.所述被封装mems加速度计芯片通过第三粘结剂固定在封装管壳基底上,所述第三粘结剂通过点胶的方式使其呈圆柱状附着在封装管壳基底上。

17.所述被封装mems加速度计芯片与被封装asic芯片的相应电极焊盘进行金属引线互连,被封装asic芯片通过金属引线与位于封装管壳内的相应焊盘实现电气连接。

18.本发明的另一个技术解决方案是:一种mems加速度计的多级抗过载封装方法,该方法包括如下步骤:

19.s1、从芯片盒中取出被封装mems加速度计芯片,并在被封装mems加速度计芯片侧面和上表面涂敷高分子聚合物;

20.s2、实现外止挡在封装管壳上的粘结,使得外止档罩在被封装mems加速度计芯片上,使得被封装mems加速度计芯片位于外止档内部,且所述被封装mems加速度计芯片和外止档之间留有抗过载间隙;

21.s3、实现被封装asic芯片在隔离框架上表面的粘结;不同的是粘结剂采取平铺形式;

22.s4、将被封装mems加速度计芯片的电极焊盘与对应的被封装asic芯片电极焊盘互连;

23.s5、将被封装asic芯片的电极焊盘与对应的封装管壳上的焊盘进行金丝键合,实现mems器件的电气连接;

24.s6、实现封装管壳和封装盖板的集成封装。

25.优选地,所述步骤中封装管壳和封装盖板通过共晶熔合的方式来进行封装。

26.优选地,所述外止档通过第一粘结剂固化在封装管壳基底上;所述第一粘结剂采用平铺的方式粘接,且粘度越大越好。

27.优选地,所述被封装asic芯片采用第二粘结剂粘结在外止档上表面;所述第二粘结剂选取asic专用粘结剂,以平铺的方式进行被封装asic芯片和外止档的粘结固定。

28.优选地,所述被封装mems加速度计芯片通过第三粘结剂固定在封装管壳基底上,所述第三粘结剂通过点胶的方式使其呈圆柱状附着在封装管壳基底上。

29.本发明与现有技术相比的有益效果是:

30.(1)、本发明通过把被封装mems加速度计芯片粘结在外止档内,所述外止档可限制被封装mems加速度计芯片在高过载环境下的位移量,降低被封装mems加速度计芯片的过载应力;

31.(2)、本发明通过被封装mems加速度计芯片上表面及端面的应力缓冲结构,缓冲高过载情况下被封装mems加速度计芯片与外止档的碰撞应力,在高过载情况下被封装mems加速度计芯片与外止档产生碰撞时,利用应力缓冲层的储存和耗散能量机制,可减小传递到芯片上冲击峰值,避免被封装mems加速度计芯片的物理性损伤;

32.(3)、本发明通过采用软胶以柱状形式固定被封装mems加速度计芯片,可降低被封装mems加速度计芯片与被封装asic芯片在环境力学参数改变下的应力,提高抗过载能力;

33.(4)、本发明与传统的管壳灌封胶质物实现抗过载的技术相比,更易实现小型化封装,且消除了灌封胶质物在变温环境下所产生的热应力对器件的影响。

34.(5)、本发明通过限制mems加速度计在高过载下的位移以及通过应力缓冲层释放结构应力,可提高mems加速度计在x、z两个方向的抗过载能力。

35.(6)、被封装mems加速度计芯片和封装管壳之间的粘结剂通过粘结材料和粘结形式的选择,可有效释放被封装mems加速度计芯片在高过载下的形变应力。

36.(7)、本发明成本低廉,工艺简单,可有效提高mems器件的高过载稳定性,具有广阔的应用前景。

附图说明

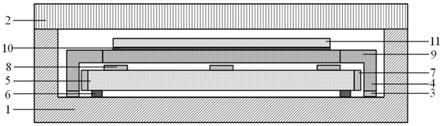

37.图1为本发明实施例的一种多级抗过载mems加速度计结构示意图;

38.图2为本发明实施例的一种多级抗过载mems加速度计的被封装mems加速度计芯片与封装管壳粘结剂位置与形貌示意图;

39.图3为本发明实施例的一种mems加速度计的多级抗过载封装方法的被封装mems加速度计芯片粘结示意图;

40.图4为本发明实施例的一种的多级抗过载mems加速度计mems的外止档示意图;

41.图5为本发明实施例的一种多级抗过载mems加速度计封装后示意图。

具体实施方式

42.下面结合实施例对本发明作进一步阐述。

43.本发明提供了一种多级抗过载mems加速度计,该加速度计包括封装管壳1、封装盖板2、被封装mems加速度计芯片5、被封装asic芯片11、外止档4、侧面应力缓冲层7、上表面应力缓冲层8;其中:

44.所述被封装mems加速度计芯片5固定在封装管壳1基底上;被封装mems加速度计芯片5粘贴在封装管壳1;外止档4固化在封装管壳1基底上,外止档4罩在被封装mems加速度计芯片5上方,使得被封装mems加速度计芯片5位于外止档4内部,且所述被封装mems加速度计芯片5和外止档4之间留有抗过载间隙,用于限制被封装mems加速度计芯片5在高过载环境下的位移改变量,同时卸载部分过载应力,降低传递到被封装mems加速度计芯片上的应力;所述被封装asic芯片11粘结在外止档4上表面。

45.所述被封装mems加速度计芯片5的侧面和上表面涂覆有柔性聚合物作为应力缓冲层,分别记为侧面应力缓冲层7和上表面应力缓冲层8;在高过载情况下被封装mems加速度计芯片与外止档产生碰撞时,利用应力缓冲层的储存和耗散能量,可减小传递到芯片上冲击峰值,避免被封装mems加速度计芯片的物理性损伤。

46.优选地,所述外止档4结构为倒u型。

47.优选地,所述外止档4选择al2o3等刚度较大的陶瓷材料。

48.优选地,所述外止档4通过第一粘结剂3固化在封装管壳1基底上;优选地,所述第一粘结剂3采用平铺的方式粘接,且粘度越大越好,用以降低外止档4在高过载下的位移,有效释放mems器件在高过载下的形变应力。最好选用硬胶,如导电银胶jm7000。

49.优选地,所述外止档4边缘设有光学观察窗,用以校准被封装mems加速度计芯片与外止档4的相对位置。

50.优选地,所述侧面应力缓冲层7和上表面应力缓冲层8,缓冲层厚度为微米量级。

51.优选地,所述被封装mems加速度计芯片5和外止档4之间的抗过载间隙优选取值范围为2

‑

5μm。

52.优选地,所述被封装asic芯片11采用第二粘结剂粘结在外止档4上表面。

53.优选地,所述第二粘结剂选取asic专用粘结剂,以平铺的方式进行被封装asic芯片11和外止档的粘结固定4。

54.优选地,所述被封装mems加速度计芯片5通过第三粘结剂固定在封装管壳1基底上。所述第三粘结剂选取弹性系数高的软胶,如gd414,并通过点胶的方式使其呈圆柱状附着在封装管壳1基底上,粘结剂在封装管壳1的位置对应于被封装mems加速度计芯片5的四角。所述被封装mems加速度计芯片5四周表面涂覆柔性聚合物,以缓冲高过载条件下与外止档4的冲击力。

55.所述被封装mems加速度计芯片5与被封装asic芯片11通过金属引线与位于封装管壳1内的相应焊盘实现电气连接。

56.进一步地,本发明盖板键合,实现被封装mems加速度计芯片5的抗高过载封装。

57.本发明还提供了另一个解决方案:上述多级抗过载mems加速度计的封装方法,该方法包括如下步骤:

58.s1、从芯片盒中取出被封装mems加速度计芯片5,并在被封装mems加速度计芯片5侧面和上表面涂敷高分子聚合物;

59.s2、实现外止挡4在封装管壳1上的粘结,使得外止档4罩在被封装mems加速度计芯片5上,使得被封装mems加速度计芯片5位于外止档4内部,且所述被封装mems加速度计芯片5和外止档4之间留有抗过载间隙;

60.s3、实现被封装asic芯片11在隔离框架4上表面的粘结;不同的是粘结剂10采取平铺形式;

61.s4、实现封装管壳1和封装盖板2的集成封装。

62.优选地,封装管壳1和封装盖板2通过共晶熔合的方式来进行封装。

63.优选地,所述外止档4通过第一粘结剂3固化在封装管壳1基底上;所述第一粘结剂3采用平铺的方式粘接,且粘度越大越好。

64.优选地,所述被封装asic芯片11采用第二粘结剂粘结在外止档4上表面;所述第二粘结剂选取asic专用粘结剂,以平铺的方式进行被封装asic芯片11和外止档的粘结固定4。

65.优选地,所述被封装mems加速度计芯片5通过第三粘结剂固定在封装管壳1基底上,所述第三粘结剂通过点胶的方式使其呈圆柱状附着在封装管壳1基底上。

66.实施例1

67.下面结合附图和具体实施方式对本发明做进一步阐述和说明。本发明说明书中未作详细描述的内容属于本领域专业技术人员的公知技术。

68.如图1为本发明的一种mems加速度计的多级抗过载封装方法结构示意图,整体封装结构包括被封装mems加速度计芯片5,被封装asic芯片6,隔离框架4,侧面应力缓冲层7,上表面应力缓冲层8,封装管壳1及封装盖板2;

69.封装管壳1、封装盖板2、外止挡4材料为陶瓷但不仅限于陶瓷。在实施例中,优选陶瓷材料,其封装的电、热性能优良,可靠性高;

70.图2

‑

图5本发明的一种mems加速度计的多级抗过载封装方法封装流程图;

71.第一步是从芯片盒中取出被封装mems加速度计芯片5,并在其x方向的侧面和上表面涂敷高分子聚合物;

72.第二步是对封装管壳8进行清洗;首先用镊子将管壳放在结晶皿中,倒入丙酮溶液,确认丙酮浸没管壳并且管壳之间没有交叠;然后将结晶皿放入超声清洗机中,设置超声时间为5min,功率为100%,开始超声;将结晶皿放入温度为110℃,开启氮气吹扫功能的红外烘箱中烘烤5min。

73.第三步是备片,挤粘结剂于胶管中,粘结剂应均匀无凝结现象,离心后将胶管嵌入点胶机上,将装有被封装mems加速度计芯片5的片盒装卡在贴片机上,并通过位置调节确认被封装mems加速度计芯片5在封装管壳的位置正确无误。

74.第四步是点胶,利用点胶机,点适量胶在被封装mems加速度计芯片5与封装管壳1的粘结面的四角位置;

75.第五步是贴片,调节贴片机、吸取被封装mems加速度计芯片5,用粘接面轻轻挤压粘结剂,并实现粘结剂与被封装mems加速度计芯片5和封装管壳1粘接面的良好接触;

76.第六步是固化,根据所选取的粘结剂类型,完成粘结剂的完全固化;

77.第七步是镜检,利用体视显微镜观察粘接层是否处于同一水平面,并均匀覆盖粘接面;

78.重复上述第二步到第六步过程,实现隔离框架4在封装管壳1上的粘结;不同的是隔离框架4与封装管壳1粘结的过程中,需要通过光学观察窗9校准隔离框架4和被封装mems加速度计芯片5的相对位置;

79.重复上述第二步到第七步过程,实现被封装asic芯片11在隔离框架4上表面的粘结;不同的是粘结剂10采取平铺形式;

80.参见图5,实现封装管壳1和封装盖板2的集成封装,在实施例中,优选地,通过共晶熔合的方式来进行封装,真空共晶焊接方法能够实现高真空度,加上吸气剂的合理应用,能维持长期的真空稳定性。

81.本发明虽然已以较佳实施例公开如上,但其并不是用来限定本发明,任何本领域技术人员在不脱离本发明的精神和范围内,都可以利用上述揭示的方法和技术内容对本发明技术方案做出可能的变动和修改,因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化及修饰,均属于本发明技术方案的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1