一种混合集成传感微系统及其单芯片集成制备方法

1.本发明属于微机电系统(mems)和集成电路领域,具体涉及到一种混合集成传感微系统及其单芯片集成制备方法。

背景技术:

2.自上世纪80年代末以来,微电子机械系统技术的高速发展使得传感器逐渐实现了小型化和低成本,大量mems传感器被广泛用于国防、工业、航空航天、汽车等领域。近年来,微纳加工技术和集成电路技术的快速发展使得把多种不同功能的微传感器、信号调理处理电路以及微处理器等集成到一起,形成一个复杂的单片集成微系统成为可能。这种高度集成化的系统芯片使得传感器性能向着多功能、高精度、高灵敏度、高稳定性、低功耗以及高可靠性的方向不断发展,集成传感微系统在精确制导、雷达预警、目标识别、宽带通信、生化检测等军事国防领域,以及消费电子、医疗、汽车驾驶、环境监测、生化检测、工业控制等民用领域展现出广阔的应用前景。同时,具有无线功能的传感器兼具远程和多信息感知,可实现网络化集群协同感知模式的突破,随着我国从机械化向信息化建设的迈进,也迫切需要发展高灵敏度、多层次、生化一体、快速、微小型的无线传感器及其系统,以实现信息的高灵敏度实时监测和感知。而mems传感器与ic的单片集成在实现完整器件功能探测的同时,也为传感器向智能化、微型化和网络化方向发展奠定了基础。

3.随着集成微系统产业需求的逐步增大,国防和民用领域都对高性能传感微系统提出了广泛需求,集成制造技术也面临着巨大挑战。绝缘体上的硅(silicon on

‑

on

‑

insulator,soi)由单晶硅器件层、sio2埋氧层和衬底组成,该材料具有十分优异的电学和机械性能,以及耐高温、抗辐射等特性,是制备高性能mems传感器的首选,特别是利用单晶硅器件层的高压阻效应制备压阻式微传感器。目前,soi基的mems器件与ic的单片集成主要根据器件层厚度来设计,对于厚器件层的soi基片,cmos电路及mems器件直接制备在器件层上,因此该方式实际上是一种基于体硅cmos工艺的集成技术。体硅cmos存在与衬底的寄生效应、电容损耗、闩锁效应、高温漏电流、短沟效应等问题,因此限制了集成微系统性能的进一步提升。对于薄器件层的soi材料,通常是去除电路区的器件层和埋氧层,cmos电路制备在硅衬底上,所以该集成工艺仍然是一种基于体硅cmos的集成技术。这种方式摒弃了soi cmos在抑制栓锁效应、短沟效应、寄生效应、沟道漏电流、串扰等方面的卓越性能,同时,去除器件层和埋氧层后的硅衬底表面缺陷和界面态、电路与传感器电互联的爬坡、以及电路和传感器不在同一层面的制备等问题均会严重影响集成微系统的性能和集成制造工艺的可靠性。

4.在上世纪60年代,出于军事空间科技发展的要求,人们开始研究soi技术。直至九十年代中期,人们才找到低成本的soi cmos工艺,soi加工技术也随之发展起来。虽然当今大部分集成电路的生产仍采用传统体硅cmos技术,但是soi技术凭借其全隔离结构在集成微传感系统领域展现出独特的优势。soi技术能够将衬底与器件有效地隔离开,避免在高温情况下普通硅片的扩散电阻pn结隔离而导致的漏电流,也能够很好避免体硅中存在的寄生

效应、闩锁效应等。在军事领域,面对高辐射环境,体硅cmos工艺感生的氧化层电荷增加,产生界面态,将不能正常工作,而soi cmos工艺因为有背栅的存在,将有效减少这种情况对器件性能的影响,因此在各种极端情况下,具有更高的稳定性。

技术实现要素:

5.集成微传感系统将高灵敏度的微传感器与信号调理、处理、以及无线通信电路进行集成,从而减小了互连线以及pcb板引入的额外寄生参数,有效减小了直流失调电压和信号通路带来的额外噪声,从而可实现微传感器信号的高信噪比检测,以及多功能、微型化、智能化、低功耗、远程监测的应用,可为集成传感微系统在信息检测领域的实用化提供有效的手段。

6.为达到上述目的,本发明的技术方案包括如下步骤:

7.一种混合集成传感微系统,其特征在于,混合集成传感微系统的组件包括多通道微传感器和电路系统,所述电路系统包括微传感器信号调理电路、以及外围设备和支持电路;或所述电路系统包括微传感器信号调理电路、微控制单元、以及外围设备和支持电路;或所述电路系统包括微传感器信号调理电路、微控制单元、射频电路模块、以及外围设备和支持电路,所述多通道微传感器进行多源信息的并行检测;所述微传感器信号调理电路对多通道微传感器信号进行选择、低噪声放大、模数转换和噪声滤除;所述微控制单元进行传感微系统的数据处理、管理、存储、控制射频模块发射数字信号、与外部系统实现交互功能;所述射频模块用于实现微传感器信号的远程无线传输;所述外围设备和支持电路用于实现信号调理电路与微控制单元之间、微控制单元与射频模块间以串行方式进行通信以交换信息,上述全部组件单片集成或者系统级集成在一起。本发明混合集成传感微系统可以基于体硅cmos工艺制备,也可以基于soi cmos工艺制备。本发明的集成传感微系统具有多通道信号并行检测、信号远程传输、信噪比高、成本低、体积小、功耗低、便于携带等技术优势。

8.本发明同时提供混合集成传感微系统的单芯片集成制备方法,其特征在于,该集成传感微系统采用体硅工艺或者soi工艺制备,将多通道微传感器、模拟cmos电路和数字cmos电路单片集成在一起,若采用体硅工艺,微传感器和cmos电路均制备在硅衬底上,若采用soi硅片制备,soi硅片的器件层即作为微传感器的敏感层,又作为cmos电路的有源区,而soi硅片的埋氧层作为微传感器和电路的下保护层,利用soi cmos工艺完成微传感器的大部分平面加工步骤,并在cmos电路制备过程中增加其他soi cmos工艺不具备的微传感器平面工艺,在soi cmos的制备工艺结束以后,完成剩余微传感器的加工步骤,用于释放微传感器结构。所述利用部分耗尽soi cmos完成的微传感器平面加工工艺包括:有源区定义、离子注入、微传感器力敏电阻上保护层淀积、欧姆接触、金属互连线定义和焊盘定义。硅岛隔离工艺同时定义传感器和soi cmos电路的有源区;利用soi cmos工艺中的沟道或者调阈值离子注入条件形成微传感器力敏电阻间的部分电互联、力敏电阻保护环和力敏电阻。利用soi cmos工艺中的重掺杂源漏注入和自对准硅化物来制备微传感器接触孔中单晶硅的掺杂,以实现欧姆接触;利用soi cmos工艺有金属互连线实现力敏电阻之间的闭合连线以及与soi cmos信号调理电路的互连。所述释放微传感器结构为去除微传感器下的衬底硅,包括从正面去除衬底硅,或者从背面去除衬底硅,soi硅片的埋氧层作为释放的自停止层,衬底硅的去除方法是采用干法刻蚀硅衬底释放微传感器结构,或者采用湿法腐蚀衬底硅释放微传感

器结构。

9.本发明具有如下有益效果:

10.本发明的集成传感微系统具有多通道信号并行检测、信号远程传输、信噪比高、成本低、体积小、功耗低、便于携带等技术优势,可为集成传感微系统在信息检测领域的实用化提供有效手段,是一种实现智能传感器的新型技术。本发明还提出了一种基于部分耗尽soi cmos的传感微系统单芯片集成制造工艺,一方面,soi cmos技术可避免体硅cmos与衬底的寄生效应、栓锁效应、高温漏电流等问题,可以大幅提高传感微系统性能。另一方面,soi基片的埋氧层提供了理想的衬底隔离层,在有效较小漏电的同时为微传感器结构释放提供诸多便利。此外,soi材料在耐高温、低压、低功耗方面的优势可以大幅提高传感器对恶劣环境的应用能力,拓展传感器的应用范围。项目提出的传感微系统集成方案具有广泛的适用性,除可以应用于本专利提出的传感微系统的研制外,还可以广泛适用于其他类型传感微系统的开发。

附图说明

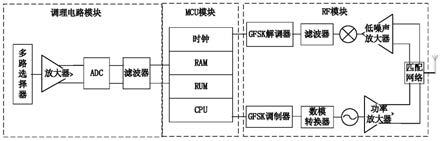

11.图1本发明实施例集成传感微系统的基本结构框图。

具体实施方式

12.下面结合附图并举实施例,对本发明进行详细描述。

13.如图1所示,本发明混合集成传感微系统包括微传感器信号调理电路、微控制单元(mcu)、射频(rf)电路模块、电源管理和时钟等伺服电路组件组成。所述微传感器信号调理电路为模拟专用集成电路(asic),包括时分或频分多路信号选择器(mux)、仪表运算放大器、模数转换电路(adc)、滤波器、伺服电路。多路信号选择器使后续电路对所需要处理的微传感器信号进行分时或分频选择,仪表运算放大器对mux输出的模拟电信号进行低噪声放大,adc将仪表运算放大器输出的模拟信号转换为脉冲宽度调制的数字信号,滤波器用于滤除带外的量化噪声,伺服模块提供基准电压、电流源和时钟信号,仪表运算放大器和adc通过时钟信号来控制信号采样频率,同时放大器模块需要带隙基准源和电流源提供精确的偏置电压和温度补偿。

14.所述muc为数据处理与控制电路,为数字电路,主要由数字信号处理(dsp),非易失性存储器(rom),易失性存储器(ram),外围设备和支持电路组成,所述cpu根据编写的指令序列执行算术运算,管理数据流并生成控制信号,非易失性存储器用于存储微控制单元的程序,易失性存储器(即ram)用于临时数据存储,外围设备帮助微控制单元与外部系统实现交互的硬件模块,经过通信协议格式转换,控制射频模块发射数字信号。所述mcu设计为处理两个不同的信号路径:控制路径和数据路径,mcu的控制路径控制主导微传感器、多路选择器、adc和带天线的rf发送器均在有限状态机(fsm)中按有序方式进行控制,以节省电源管理中的功耗。所述mcu的数据路径对微传感器数据进行压缩处理,从芯片读取adc输出的1bit码流和时钟,通过数字信号处理(dsp)完成抽取和滤波,最后获得24bit的输出数据,再通过串行接口发送到射频(rf)模块中,rf模块负责向外界发送传感器输出数据。所述外围设备和支持电路包括但不限于串行外设接口电路,用于实现adc信号与微控制单元之间、微控制单元与射频模块间以串行方式进行通信以交换信息;

15.所述射频模块包括收发器和天线,主要由射频收发机、频率发生器、晶体振荡器、调制解调器等功能模块组成,支持一对多组网和带ack的通信模式,用于实现微传感器信号的远程无线传输;所述射频模块由微控制单元控制,实现微传感器信号的发射、接收、唤醒、寄存的低功耗运行,射频模块的发射和接收功率、工作频道以及通信数据率均可配置,自带部分链路层的通信协议,并配置少量的参数寄存器。

16.本发明全部组件可以采用体硅工艺或者soi工艺单芯片集成在一起。

17.本发明以一种基于部分耗尽soi cmos工艺的压阻式集成微悬臂梁传感器单芯片集成为例,包括但不限于以下工艺步骤:

18.a)使用部分耗尽型的soi cmos工艺,采用单抛p型[110]晶向soi硅片,器件层厚度340nm,埋氧厚度400nm。器件层同时作为微传感器力敏电阻和cmos器件的有源区,埋氧层作为器件的下保护层和释放微悬臂梁传感器工艺的停止层。

[0019]

b)soi硅片经过常规清洗后,淀积二氧化硅层和氮化硅层,氮化硅作为刻蚀硅的掩膜,中间层的二氧化硅可用于后续的注入阻挡。

[0020]

c)光刻定义有源区,包含cmos电路区域和微悬臂梁传感器区域,这两部分之间尽量远离放置,以避免后续的微传感器工艺影响cmos电路的性能和可靠性。之后刻蚀氮化硅、二氧化硅层和单晶硅器件层,形成硅岛结构。

[0021]

d)淀积二氧化硅绝缘层,以在硅岛隔离结构之间形成完全的区域隔离,防止cmos电路和微传感器器件之间的互相干扰。

[0022]

e)利用化学机械抛光工艺平坦器件表面并形成浅槽隔离,最终完成有源区的定义。

[0023]

f)去除硬掩模氮化硅,裸露出的二氧化硅可用来做后续的沟道离子注入阻挡层。

[0024]

g)光刻,离子注入形成n阱区和p

‑

沟道区,为了形成均匀分布,可采用不同能量多次注入的方法,用低能量、低剂量注入调整soi cmos器件的阈值电压。其中n阱区域的离子注入同时对力敏电阻区域进行,形成n+环,以减小力敏电阻的漏电流。

[0025]

h)去除二氧化硅,重新热氧化生成栅氧化层,根据设计的阈值电压调整栅氧的厚度。然后lpcvd淀积多晶硅,磷离子注入形成n+多晶硅栅。光刻定义多晶硅栅、多晶硅引线,刻蚀多晶硅,再进行多晶硅退火。

[0026]

i)光刻,同时对pmos和nmos进行ldd注入,用来抑制短沟道效应。

[0027]

j)lpcvd淀积二氧化硅后刻蚀掉形成二氧化硅侧墙,用来阻挡源漏注入离子的横向散射。

[0028]

k)光刻后进行源漏注入,使源漏结深到达埋氧层,同时定义重掺杂互连线。该工艺还同时对体接触区域进行注入,改善体接触电阻。之后进行快速热退火处理,改善离子分布。

[0029]

l)定义力敏电阻图形,离子注入调整力敏电阻阻值,为了保证力敏电阻的位置靠近微传感器表面,并保证较高的探测灵敏度,需调整注入剂量和注入能量。

[0030]

m)为了实现金属互连,先淀积二氧化硅钝化层,之后进行光刻,反应离子刻蚀二氧化硅钝化层,形成接触孔。

[0031]

n)溅射金属ti/tin,作为阻挡层,金属w有很好的填充性能和台阶覆盖性,cvd淀积w后,然后利用cmp平坦化金属w,并形成金属互连线。

[0032]

o)完成多次金属工艺后,在微传感器表面及反应池区域形成较厚的介质层,这会影响微传感器的灵敏度。因此需对该区域介质层进行减薄,最终使微传感器的总体厚度约为1μm。

[0033]

p)进行厚胶光刻,定义微传感器结构,bhf腐蚀钝化层和埋氧层,并rie刻蚀埋氧与硅衬底界面的过渡层。最终采用各向异性/同性干法刻蚀工艺去除微传感器下的衬底硅,释放微传感器。

[0034]

综上所述,以上仅为本发明的较佳实施例而已,并非用于限定本发明的保护范围。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1