电源电路的制作方法

1.本发明涉及一种电源电路。

背景技术:

2.对于电源电路要求驱动能力高且自消耗电力小的高效率的电路。另一方面,为了提高驱动能力,需要能力高的驱动元件。能力高的驱动元件由于其电流驱动能力高,因此存在招致启动时的冲击电流和输出电压的过冲这样的问题。

3.因此,已知具备对输出晶体管的能力进行切换的功能的电源电路(例如参照专利文献1)。电源电路在启动时,通过抑制输出晶体管的能力来防止过冲和冲击电流。电源电路在输出电压达到目标电压附近时,使输出晶体管的能力增加。

4.通过这样的控制,在电源电路的启动时抑制电流驱动能力,在作为电源电路进行动作时,能够具有必要且充分的电流驱动能力。

5.专利文献1:日本特开2009

‑

266121号公报

技术实现要素:

6.发明要解决的问题

7.在专利文献1的电源电路中,在启动时与通常时之间对输出晶体管的能力进行切换,由此实现顺畅的启动和启动后的高的电流能力。

8.在专利文献1的电源电路中,在启动时和启动后这两方,输出晶体管的前级的放大电路的结构及动作相同。在启动时和启动后,放大器的输出阻抗不变化,因此电源电路无法供给稳定的电压。

9.因此,本发明的目的在于提供能够实现顺畅的启动和启动后的高的电流能力并且供给稳定的电压的电源电路。

10.用于解决问题的方案

11.本发明的电源电路具备:差动放大部,包括构成差动对的第一输入晶体管和第二输入晶体管以及第一尾电流源和第二尾电流源;输出级,包括能够利用差动放大部的输出来进行驱动的第一输出晶体管和第二输出晶体管;以及控制部,以在启动时由第一尾电流源和第一输出晶体管对负载进行驱动、在启动后由第一尾电流源、第二尾电流源、第一输出晶体管以及第二输出晶体管对负载进行驱动的方式进行控制。

12.发明的效果

13.根据本发明,在启动时,由第一尾电流源和第一输出晶体管对负载进行驱动,在启动后,由第一尾电流源、第二尾电流源、第一输出晶体管以及第二输出晶体管对负载进行驱动。由此,能够实现顺畅的启动和启动后的高的电流能力,并且供给稳定的电压。

附图说明

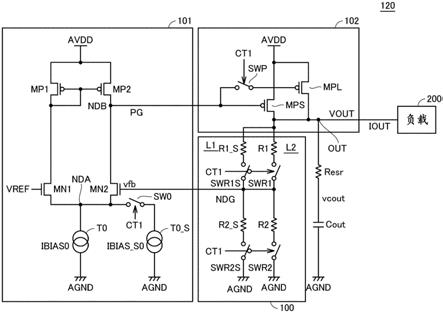

14.图1是表示实施方式1的电源电路的结构的图。

15.图2是表示参考例的运算放大器620的结构的图。

16.图3是表示实施方式1的运算放大器120的结构的图。

17.图4是表示控制部103的结构的图。

18.图5的(a)是表示输入控制信号ct0的时间变化的图。图5的(b)是表示启动完成控制信号ct1的时间变化的图。

19.图6的(a)是表示参考例的运算放大器620的频率响应特性的波特图。(b)是表示实施方式1的运算放大器120的频率响应特性的波特图。

20.图7是表示参考例的运算放大器620的输出电压vout的波形的图。

21.图8是表示实施方式1的运算放大器120的输出电压vout的波形的图。

22.图9是表示参考例的电源电路的消耗电流的波形的图。

23.图10是表示实施方式1的电源电路的消耗电流的波形的图。

24.图11是表示实施方式2的控制部203的结构的图。

25.图12是表示实施方式3的运算放大器220的结构的图。

26.图13是表示实施方式4的运算放大器320的结构的图。

27.图14是表示实施方式5的运算放大器420的结构的图。

28.图15是表示实施方式6的运算放大器520的结构的图。

29.图16是表示实施方式7的运算放大器720的结构的图。

30.(附图标记说明)

31.100、500、600:反馈电阻部;101、201、301、601、701:差动放大部;102、602:输出级;103、203:控制部;120、220、320、420、520、620、720:运算放大器;200:负载;210:分压部;cout:输出电容;mp1、mp2、mp3、mp4、mps、mpl、mps2、mpl2:pmos晶体管;mn1、mn2、m200:nmos晶体管;rd1、rd2、r1、r2、r1_s、rs_s、r12、r22、r12_s、r22_s:电阻;t0、t0_s、t1、t1_s、t2、t2_s、t0_s1、t0_s2:尾电流源;swp、swp2、sw0、sw1、sw2、sw0_1、sw0_2、swr1、swr2、swr1s、swr2s、swr12、swr22、swr12s、swr22s:开关;bf、bf2:缓冲器;iv1、iv2、iv3、iv4:反相器;bi:偏置电流源;c200:电容元件;cmp:比较器。

具体实施方式

32.以下,关于实施方式,参照图来进行说明。

33.实施方式1.

34.图1是表示实施方式1的电源电路的结构的图。

35.该电源电路具备输入端子in、控制端子ctrl、输出端子out、运算放大器120、输出电容cout以及控制部103。

36.运算放大器120通过将从输入端子in输入的输入电压vref根据反馈电阻比进行放大,来产生输出电压vout。运算放大器120具备差动放大部101、输出级102以及反馈电阻部100。控制部103接收输入控制信号ct0并输出启动完成控制信号ct1。输入控制信号ct0经由控制部103被送到运算放大器120的各结构要素,对运算放大器120的各结构要素的低消耗电力模式的设定进行控制。对于运算放大器120的启动,利用来自控制部103的启动完成控制信号ct1和输出电容cout进行控制。

37.图2是表示参考例的运算放大器620的结构的图。

38.参考例的运算放大器620具备差动放大部601、输出级102以及反馈电阻部600。

39.差动放大部601具备构成差动对的nmos晶体管mn1、mn2、构成有源负载的pmos晶体管mp1、mp2以及尾电流源t0。

40.在电源avdd与节点nda之间,pmos晶体管mp1与nmos晶体管mn1串联连接。在电源avdd与节点nda之间,pmos晶体管mp2与nmos晶体管mn2串联连接。

41.pmos晶体管mp1的栅极、pmos晶体管mp1的漏极以及pmos晶体管mp2的栅极被连接。

42.nmos晶体管mn1的栅极接收输入电压vref。nmos晶体管mn2的栅极接收来自反馈电阻部600的反馈电压vfb。

43.pmos晶体管mp2与nmos晶体管mn2之间的节点ndb将栅极电压pg送到输出级102。

44.在节点nda与地电源agnd之间配置有尾电流源t0。尾电流源t0输出尾电流ibias0+ibias_s0。

45.输出级102具备作为输出晶体管的pmos晶体管mpl、mps以及开关swp。

46.在电源avdd与输出端子out之间,pmos晶体管mps与pmos晶体管mpl并联地配置。pmos晶体管mps的栅极与节点ndb连接,接收栅极电压pg。

47.在节点ndb与pmos晶体管mpl的栅极之间配置有开关swp。pmos晶体管mpl的栅极在开关swp为导通时,接收栅极电压pg。对于开关swp,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关swp变为导通。在启动完成控制信号ct1为低电平时,开关swp变为断开。

48.反馈电阻部600具备反馈电阻r1、r2。

49.在输出端子out与地电源agnd之间,电阻r1、电阻r2串联连接。

50.图3是表示实施方式1的运算放大器120的结构的图。

51.运算放大器120具备差动放大部101、输出级102以及反馈电阻部100。

52.差动放大部101具备构成差动对的nmos晶体管mn1(第一输入晶体管)和nmos晶体管mn2(第二输入晶体管)、构成有源负载的pmos晶体管mp1、mp2。差动放大部101还具备尾电流源ti(第一尾电流源)、尾电流源ti_s(第二尾电流源)以及开关sw0(第二开关)。

53.在电源avdd(第一电源)与节点nda(第一节点)之间,pmos晶体管mp1与nmos晶体管mn1串联连接。在电源avdd与节点nda之间,pmos晶体管mp2与nmos晶体管mn2串联连接。nmos晶体管mn1的一端和nmos晶体管mn2的一端连接于节点nda。

54.pmos晶体管mp1的栅极、pmos晶体管mp1的漏极以及pmos晶体管mp2的栅极被连接。

55.nmos晶体管mn1的栅极接收输入电压vref。nmos晶体管mn2的栅极接收来自反馈电阻部100的反馈电压vfb。

56.pmos晶体管mp2与nmos晶体管mn2之间的节点ndb将栅极电压pg送到输出级102。

57.在节点nda与地电源agnd(第二电源)之间配置有尾电流源t0。尾电流源t0输出尾电流ibias0。

58.在节点nda与地电源agnd之间,开关sw0与尾电流源t0_s串联连接。尾电流源t0_s输出尾电流ibias_s0。对于开关sw0,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关sw0变为导通。在启动完成控制信号ct1为低电平时,开关sw0变为断开。

59.输出级102具备作为输出晶体管的pmos晶体管mps(第一输出晶体管)、pmos晶体管

mps(第二输出晶体管)以及开关swp(第一开关)。pmos晶体管mpl的尺寸大于pmos晶体管mps的尺寸。

60.在电源avdd与输出端子out之间配置有pmos晶体管mps。在电源avdd与输出端子out之间配置有pmos晶体管mpl。pmos晶体管mps的栅极与节点ndb连接,接收栅极电压pg。

61.在节点ndb与pmos晶体管mpl的栅极之间配置有开关swp。pmos晶体管mpl的栅极在开关swp为导通时,接收栅极电压pg。对于开关swp,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关swp变为导通。在启动完成控制信号ct1为低电平时,开关swp变为断开。

62.反馈电阻部100将对输出端子out的电压进行分压得到的电压反馈到差动放大部101。反馈电阻部100包括第一路径l1和第二路径l2。

63.控制部103以在启动时使电流流过第一路径l1、且使电流不流过第二路径l2的方式进行控制。控制部103以在启动后使电流流过第二路径l2、且使电流不流过第一路径l1的方式进行控制。第一路径l1的电阻小于第二路径l2的电阻。

64.反馈电阻部100具备反馈电阻r1_s(第一电阻)、反馈电阻r1(第二电阻)、反馈电阻r2_s(第三电阻)、反馈电阻r2(第四电阻)。

65.反馈电阻部100还具备开关swr1s(第五开关)、开关swr1(第六开关)、开关swr2s(第七开关)、开关swr2(第八开关)。反馈电阻r1_s的电阻值小于反馈电阻r1的电阻值。反馈电阻r2_s的电阻值小于反馈电阻r2的电阻值。

66.反馈电阻r1与反馈电阻r1_s在输出端子out与节点ndg(第二节点)之间并联地配置。反馈电阻r2与反馈电阻r2_s在节点ndg与地电源agnd之间并联地配置。节点ndg的电压vfg被送到差动放大部101的nmos晶体管mn2的栅极。

67.开关swr1s配置于反馈电阻r1_s与节点ndg之间。开关swr1配置于反馈电阻r1与节点ndg之间。开关swr2s配置于反馈电阻r2_s与地电源agnd之间。开关swr2配置于反馈电阻r2与地电源agnd之间。

68.对于开关swr1、swr2,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关swr1、swr2变为导通。在启动完成控制信号ct1为低电平时,开关swr1、swr2变为断开。对于开关swr1s、swr2s,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关swr1s、swr2s变为断开。在启动完成控制信号ct1为低电平时,开关swr1s、swr2s变为导通。由此,在启动时,电流流过第一路径l1上的反馈电阻r1_s和反馈电阻r2_s,且电流不流过第二路径l2上的反馈电阻r1和反馈电阻r2。在启动后,电流流过第二路径l2上的反馈电阻r1和反馈电阻r2,且电流不流过第一路径l1上的反馈电阻r1_s和反馈电阻r2_s。

69.图4是表示控制部103的结构的图。

70.控制部103具备nmos晶体管m200、电容元件c200、偏置电流源bi以及缓冲器bf。缓冲器bf具备反相器iv1和反相器iv2。

71.在电源avdd与节点ndc(第三节点)之间配置有偏置电流源bi。偏置电流源bi输出偏置电流ibias。

72.在节点ndc与地电源agnd之间配置有nmos晶体管m200(驱动晶体管)。nmos晶体管m200的栅极接收输入控制信号ct0。

73.在节点ndc与地电源agnd之间配置有电容元件c200。

74.反相器iv1接收节点ndc的电压。反相器iv1的输出与反相器iv2的输入连接。反相器iv2输出启动完成控制信号ct1。利用启动完成控制信号ct1对包含于差动放大部101、输出级102、反馈电阻部100中的开关sw0、swp、swr1、swr2、swr1s、swr2s进行控制。

75.图5的(a)是表示输入控制信号ct0的时间变化的图。图5的(b)是表示启动完成控制信号ct1的时间变化的图。

76.在初始状态下,输入控制信号ct0为低电平。此时,nmos晶体管m200为断开状态,因此作为nmos晶体管m200的漏极电压的节点ndc的电压为几乎接近电源电压avdd的电平。在该状态下,反相器iv1被输入低电平的电压,因此从反相器iv2输出的启动完成控制信号ct1为低电平。

77.当输入控制信号ct0从低电平变化为高电平时,nmos晶体管m200导通,由此作为nmos晶体管m200的漏极电压的节点ndc的电压逐渐从电源电压avdd电平变化为agnd电平。

78.在此,在将偏置电流源bi的电流设为ibias、以及将电容元件c200的电容值设为c200时,用以下的式表示从输入控制信号ct0变化为高电平起至启动完成控制信号ct1变化为高电平为止的时间δt。

79.δv=avdd

‑

agnd

···

(a1)

80.δt=c200

×

δv/ibias

···

(a2)

81.控制部103在初始状态下(启动时)将启动完成控制信号ct1设为低电平,在启动后将启动完成控制信号ct1设为高电平。换言之,启动完成信号ct1为低电平时是启动时,启动完成信号ct1为高电平时是启动后。

82.控制部103在启动时,将开关sw0设为断开,将开关swp设为断开,将开关swr1、swr2设为断开,将开关swr1s、swr2s设为导通。其结果,尾电流仅为ibias0,只有输出晶体管mps被驱动。其结果,由输出晶体管mps和尾电流源t0对负载200进行驱动。电流从输出端子out通过电阻r1_s和r2_s流动。

83.控制部103在启动后,将开关sw0设为导通,将开关swp设为导通,将开关swr1、swr2设为导通,将swr1s、swr2s设为断开。其结果,尾电流为ibias0+ibias_s0,输出晶体管mps和mpl被驱动。其结果,由输出晶体管mps、mpl和尾电流源t0、t0_s对负载200进行驱动。电流从输出端子out通过电阻r1和r2流动。

84.初始状态的运算放大器120的驱动能力是由晶体管mps决定的。晶体管mps与晶体管mpl相比能力足够低,因此能够抑制启动时的电流能力。

85.在参考例中,仅具有利用开关swp对输出晶体管的能力的大小进行切换的功能。例如,在将输出晶体管mps与mpl的尺寸的比率设定为2倍~5倍左右的情况下,不会产生大的问题。

86.然而,近年的iot(internet of things:物联网)等的装置被要求运算放大器120或电源电路的自消耗电力极小,为数[ua]至[na]的水平。另外,启动时的消耗电力也被要求为[uw]至[nw]的水平。并且,其驱动能力被要求为数100[ma]至数[a]的水平。

[0087]

鉴于这样的状况,为了抑制启动时的突入电流,需要选择能力低的晶体管来作为输出晶体管mps。另一方面,为了提高通常使用时的驱动能力,需要选择能力高的晶体管来作为输出晶体管mpl。

[0088]

这样构成的运算放大器以在使用时其输出电压稳定为绝对条件。然而,即使设计成在使用时稳定,如果输出晶体管mps与mpl的尺寸的比率相差10倍以上,则也存在如下担忧:即使在选择了输出晶体管mpl和mps时稳定,在仅选择了输出晶体管mps时也变得不稳定。

[0089]

在本实施方式中,利用开关swp对输出晶体管的能力的大小进行切换,并且利用开关sw0对尾电流的大小进行切换,利用开关swr1、swr2、swr1s、swr2s对在反馈电阻部100中流动的电流的大小进行切换。

[0090]

图6的(a)是表示参考例的运算放大器620的频率响应特性的波特图。

[0091]

运算放大器620的第一极点p1在启动后被配置在频率fp1,在启动时被配置在频率fp1

′

。

[0092]

fp1=λiout/(2πcout)

···

(1)

[0093]

fp1

′

=λ

′

iout

′

/(2πcout)

···

(2)

[0094]

其中,λ是由输出晶体管mps和mpl确定的沟道长度调制系数。输出晶体管mps的尺寸小于输出晶体管mpl的尺寸,因此λ大致是输出晶体管mpl的沟道长度调制系数。λ

′

是输出晶体管mps的沟道长度调制系数。iout、iout

′

是从输出端子out流过负载200的电流。由于iout

′

>iout、λ

′

>λ,因此成为fp1

′

>fp1。cout是输出电容cout的电容值。

[0095]

运算放大器620的第二极点p2在启动后被配置在频率fp2,在启动时被配置在频率fp2

′

(r)。

[0096]

fp2=1/(2π(r1+r2)

×

cgate)

···

(3)

[0097]

fp2

′

(r)=1/(2π(r1+r2)

×

cgate

′

)

···

(4a)

[0098]

在此,r1、r2是电阻r1、r2的电阻值。cgate是以输出晶体管mpl和mps的栅极电容为主的寄生电容。cgate

′

是以输出晶体管mps的栅极电容为主的寄生电容。由于cgate>cgate

′

,因此成为fp2

′

(r)>fp2。

[0099]

运算放大器的第三极点p3在启动后被配置在频率fp3,在启动时被配置在频率fp3

′

(r)。

[0100]

fp3=1/(2π(roa

×

cgate)

···

(5)

[0101]

fp3

′

(r)=1/(2π(roa

×

cgate

′

)

···

(6a)

[0102]

在此,roa是晶体管mp2和mn2的输出阻抗。roa与尾电流ibias0+ibias_s0成比例。

[0103]

由于cgate>cgate

′

,因此成为fp3

′

(r)>fp3。

[0104]

运算放大器的零点z1在启动后和启动时被配置在频率fz1。

[0105]

fz1=1/(2πresr

×

cout)

···

(7)

[0106]

在此,resr是输出电容cout的esr。

[0107]

图6的(b)是表示实施方式1的运算放大器120的频率响应特性的波特图。

[0108]

运算放大器120的第一极点p1在启动后被配置在频率fp1,在启动时被配置在频率fp1

′

。

[0109]

fp1=λiout/(2πcout)

···

(1)

[0110]

fp1

′

=λ

′

iout

′

/(2πcout)

···

(2)

[0111]

其中,λ是由输出晶体管mps和mpl确定的沟道长度调制系数。输出晶体管mps的尺寸小于输出晶体管mpl的尺寸,因此λ大致是输出晶体管mpl的沟道长度调制系数。λ

′

是输出

晶体管mps的沟道长度调制系数。iout、iout

′

是从输出端子out流过负载200的电流。由于iout

′

>iout、λ

′

>λ,因此成为fp1

′

>fp1。cout是输出电容cout的电容值。

[0112]

运算放大器的第二极点p2在启动后被配置在频率fp2,在启动时被配置在频率fp2

′

。

[0113]

fp2=1/(2π(r1+r2)

×

cgate)

···

(3)

[0114]

fp2

′

=1/(2π(r1_s+r2_s)

×

cgate

′

)

···

(4)

[0115]

在此,r1、r2、r1_s、r2_s是电阻r1、r2、r1_s、r2_s的电阻值。cgate是以输出晶体管mpl和mps的栅极电容为主的寄生电容。cgate

′

是以输出晶体管mps的栅极电容为主的寄生电容。由于r1>r1_s、r2>r2_s、cgate>cgate

′

,因此成为fp2

′

>fp2、fp2

′

>fp2

′

(r)。

[0116]

运算放大器的第三极点p3在启动后被配置在频率fp3,在启动时被配置在频率fp3

′

。

[0117]

fp3=1/(2π(roa

×

cgate)

···

(5)

[0118]

fp3

′

=1/(2π(roa

′×

cgate

′

)

···

(6)

[0119]

在此,roa、roa

′

是晶体管mp2和mn2的输出阻抗。roa与尾电流ibias0+ibias_s0成比例,roa

′

与尾电流ibias0成比例。

[0120]

由于roa>roa

′

、cgate>cgate

′

,因此成为fp3

′

>fp3、fp3

′

>fp3

′

(r)。如图6的(b)所示,fp3

′

与fp3相比足够大。在fp3

′

处,将总增益a[db]设为0[db]以下,由此能够实现2极点1零点的系统。其结果,能够确保充分的稳定性。

[0121]

运算放大器的零点z1在启动后和启动时被配置在频率fz1。

[0122]

fz1=1/(2πresr

×

cout)

···

(7)

[0123]

在此,resr是输出电容cout的esr。

[0124]

图7是表示参考例的运算放大器620的输出电压vout的波形的图。

[0125]

在参考例中,输出电压vout包括纹波或sin波等。

[0126]

图8是表示实施方式1的运算放大器120的输出电压vout的波形的图。

[0127]

在实施方式1中,输出电压vout包括启动时、启动后(稳定时以及从启动时起至稳定时为止的过渡期间)在内,稳定且平滑地变化。

[0128]

图9是表示参考例的电源电路的消耗电流的波形的图。

[0129]

在参考例中,在启动时,由于输出电压vout的变动而输出电容cout无用地进行充放电。即使使用抑制了能力的输出晶体管mps,也无法充分地发挥效果。

[0130]

图10是表示实施方式1的电源电路的消耗电流的波形的图。

[0131]

在实施方式1中,输出电容cout不会无用地进行充放电,因此能够削减消耗电流。

[0132]

实施方式2.

[0133]

图11是表示实施方式2的控制部203的结构的图。

[0134]

控制部203具备分压部210、比较器cmp以及缓冲器bf2。缓冲器bf2具备反相器iv3和反相器iv4。

[0135]

分压部210对向负载200供给的输出电压vout进行分压。分压部210具备在输出端子out与地电源agnd之间串联连接的电阻rd1和电阻rd1。

[0136]

分压部210输出分压电压vr。

[0137]

vr=vout

×

rd1/(rd1+rd2)

···

(8)

[0138]

将电阻rd1的电阻值设为rd1,将电阻rd2的电阻值设为rd2。

[0139]

比较器cmp将分压电压vr与作为基准电压的输入电压vref进行比较。比较器cmp在vr≥vref时输出高电平。比较器cmp在vr<vref时输出低电平。

[0140]

反相器iv3接收比较器cmp的输出。反相器iv3的输出与反相器iv4的输入连接。反相器iv4输出启动完成控制信号ct1。利用启动完成控制信号ct1对包含于差动放大部101、输出级102、反馈电阻部100中的开关sw0、swp、swr1、swr2、swr1s、swr2s进行控制。

[0141]

实施方式3.

[0142]

图12是表示实施方式3的运算放大器220的结构的图。

[0143]

运算放大器220具备差动放大部201、输出级102以及反馈电阻部100。输出级102及反馈电阻部100与在实施方式1中说明的内容同样,因此不重复说明。

[0144]

差动放大部201与实施方式1同样地,具备构成差动对的nmos晶体管mn1、mn2、构成有源负载的pmos晶体管mp1、mp2、尾电流源t0、t0_s以及开关sw0。

[0145]

差动放大部201还具备构成作为放大器发挥功能的源极接地电路的pmos晶体管mp3、尾电流源t1、t1_s以及开关sw1。

[0146]

在电源avdd与节点ndd之间配置有pmos晶体管mp3。pmos晶体管mp3的栅极接收节点ndb的栅极电压pg。连接有pmos晶体管mp3的漏极的节点ndd将栅极电压pg2送到输出级102。在输出级102中,pmos晶体管mps的栅极与节点ndd连接,接收栅极电压pg2。在节点ndd与pmos晶体管mpl的栅极之间配置有开关swp。pmos晶体管mpl的栅极在开关swp为导通时,接收栅极电压pg2。

[0147]

在节点ndd与地电源agnd之间配置有尾电流源t1。尾电流源t1输出尾电流ibias1。

[0148]

在节点ndd与地电源agnd之间连接开关sw1和尾电流源t1_s。尾电流源t1_s输出尾电流ibias_s1。对于开关sw1,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关sw1变为导通。在启动完成控制信号ct1为低电平时,开关sw1变为断开。

[0149]

控制部103在启动时,将开关sw0、sw1设为断开,将开关swp设为断开,将开关swr1、swr2设为断开,将开关swr1s、swr2s设为导通。其结果,尾电流仅为ibias0+ibias1,只有输出晶体管mps被驱动。电流从输出端子out通过电阻r1_s和r2_s流动。

[0150]

控制部103在启动后,将开关sw0、sw1设为导通,将开关swp设为导通,将开关swr1、swr2设为导通,将swr1s、swr2s设为断开。其结果,尾电流成为ibias0+ibias_s0+ibias1+ibias_s1,输出晶体管mps和mpl被驱动。电流从输出端子out通过电阻r1和r2流动。

[0151]

此外,根据运算放大器220的频带和psrr(power supply rejection ratio:电源抑制比)等规格,决定ibias0和ibias1的值。根据所决定的值,有时在从“启动时”变化为“启动后”时仅切换开关sw0和开关sw1中的一方的就足够。在这样的情况下,也可以仅对开关sw0和开关sw1中的一方进行切换,对另一方不进行切换。

[0152]

实施方式4.

[0153]

图13是表示实施方式4的运算放大器320的结构的图。

[0154]

运算放大器320具备差动放大部301、输出级102以及反馈电阻部100。输出级102及反馈电阻部100与在实施方式1中说明的内容同样,因此不重复说明。

[0155]

差动放大部301与实施方式2同样地,具备构成差动对的nmos晶体管mn1、mn2、构成

有源负载的pmos晶体管mp1、mp2、构成源极接地电路的pmos晶体管mp3、尾电流源t0、t0_s、t1、t1_s以及开关sw0、sw1。

[0156]

差动放大部301还具备构成作为放大器发挥功能的源极接地电路的pmos晶体管mp4、尾电流源t2、t2_s以及开关sw2。

[0157]

在电源avdd与节点nde之间配置有pmos晶体管mp4。pmos晶体管mp4的栅极接收节点ndd的栅极电压pg2。连接有pmos晶体管mp4的漏极的节点nde将栅极电压pg3送到输出级102。在输出级102中,pmos晶体管mps的栅极与节点nde连接,接收栅极电压pg3。在节点nde与pmos晶体管mpl的栅极之间配置有开关swp。pmos晶体管mpl的栅极在开关swp为导通时,接收栅极电压pg3。

[0158]

在节点nde与地电源agnd之间配置有尾电流源t2。尾电流源t2输出尾电流ibias2。

[0159]

在节点nde与地电源agnd之间连接开关sw2和尾电流源t2_s。尾电流源t2_s输出尾电流ibias_s2。

[0160]

对于开关sw2,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关sw2变为导通。在启动完成控制信号ct1为低电平时,开关sw2变为断开。

[0161]

控制部103在启动时,将开关sw0、sw1、sw2设为断开,将开关swp设为断开,将开关swr1、swr2设为断开,将开关swr1s、swr2s设为导通。其结果,尾电流仅为ibias0+ibias1+ibias2,只有输出晶体管mps被驱动。电流从输出端子out通过电阻r1_s和r2_s流动。

[0162]

控制部103在启动后,将开关sw0、sw1、sw2设为导通,将开关swp设为导通,将开关swr1、swr2设为导通,将swr1s、swr2s设为断开。其结果,尾电流成为ibias0+ibias_s0+ibias1+ibias_s1+ibias2+ibias_s2,输出晶体管mps和mpl被驱动。电流从输出端子out通过电阻r1和r2流过。

[0163]

此外,根据运算放大器320的频带和psrr等规格,决定ibias0、ibias1、ibias的值。根据所决定的值,有时在启动后仅切换开关sw0、开关sw1、开关sw2中的任意一个或两个就足够。在这样的情况下,也可以仅对开关sw0、开关sw1以及开关sw2中的任意一个或任两个进行切换,不对剩余开关进行切换。

[0164]

在上述的实施方式中,差动放大部还包括接收差动对的输出的2级的放大器mp3、mp4以及各自与对应的放大器连接的两套的第一组尾电流源t1、t2和第二种尾电流源t2、t2_s。第二组尾电流源t2、t2_s在各自的对应的开关为导通时,供给尾电流。

[0165]

控制部以在启动时由尾电流源t0和2个第一组尾电流源t1、t2对负载进行驱动的方式进行控制。控制部以在启动后由尾电流源t0、尾电流源t0_s、2个第一组尾电流源t1、t2以及2个第二种尾电流源t1_s、t2_s对负载进行驱动的方式进行控制。不限定于上述的实施方式,还包括如下的变形例。

[0166]

差动放大部还包括接收差动对的输出的n级(n为1以上的自然数)的放大器以及各自与对应的放大器连接的n套的第一组尾电流源和第二种尾电流源。第二组尾电流源在各自的对应的开关为导通时,供给尾电流。

[0167]

控制部以在启动时由尾电流源t0和n个第一组尾电流源对负载进行驱动的方式进行控制。控制部以在启动后由尾电流源t0、尾电流源t0_s、n个第一组尾电流源以及n个第二种尾电流源中的m个(n≥m)第二种尾电流源对负载进行驱动的方式进行控制。

[0168]

实施方式5.

[0169]

图14是表示实施方式5的运算放大器420的结构的图。

[0170]

运算放大器420具备差动放大部101、输出级402以及反馈电阻部100。差动放大部101及反馈电阻部100与在实施方式1中说明的内容同样,因此不重复说明。

[0171]

输出级402具备作为输出晶体管的pmos晶体管mpl、mpl2、mps、mps2以及开关swp、swp2。pmos晶体管mpl的尺寸大于pmos晶体管mps的尺寸。pmos晶体管mpl2的尺寸大于pmos晶体管mps2的尺寸。

[0172]

在电源avdd与输出端子out之间,pmos晶体管mps、pmos晶体管mps2、pmos晶体管mpl以及pmos晶体管mpl2并联地配置。pmos晶体管mps的栅极与节点ndb连接,接收栅极电压pg。pmos晶体管mps2的栅极与节点ndb连接,接收栅极电压pg。

[0173]

在节点ndb与pmos晶体管mpl的栅极之间配置有开关swp。在节点ndb与pmos晶体管mpl的栅极之间配置有开关swp2。pmos晶体管mpl的栅极在开关swp为导通时,接收栅极电压pg。pmos晶体管mpl2的栅极在开关swp2为导通时,接收栅极电压pg。对于开关swp、swp2,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关swp、swp2变为导通。在启动完成控制信号ct1为低电平时,开关swp、swp2变为断开。

[0174]

控制部103在启动时,将开关sw0设为断开,将开关swp、swp2设为断开,将开关swr1、swr2设为断开,将开关swr1s、swr2s设为导通。其结果,尾电流仅为ibias0,只有输出晶体管mps、mps2被驱动。其结果,由输出晶体管mps、mps2和尾电流源t0对负载200进行驱动。电流从输出端子out通过电阻r1_s和r2_s流动。

[0175]

控制部103在启动后,将开关sw0设为导通,将开关swp、swp2设为导通,将开关swr1、swr2设为导通,将swr1s、swr2s设为断开。其结果,尾电流成为ibias0+ibias_s0,输出晶体管mps、mps2、mpl、mpl2被驱动。其结果,由输出晶体管mps、mps2、mpl、mpl2和尾电流源t0、t0_s对负载200进行驱动。电流从输出端子out通过电阻r1和r2流动。

[0176]

此外,在上述的实施方式中,设为除了输出晶体管mps、ml2以外,还有2个晶体管在电源avdd与输出端子out之间并联地配置。控制部103以在启动时由输出晶体管mps和2个晶体管中的1个晶体管对负载200进行驱动的方式进行控制。控制部103以在启动后由输出晶体管mps、mpl和2个晶体管对负载200进行驱动的方式进行控制。不限定于上述的实施方式,还包括如下的变形例。

[0177]

也可以设为除了输出晶体管mps、mpl以外,还有n个(n为2以上的自然数)晶体管在电源avdd与输出端子out之间并联地配置。控制部103以在启动时由输出晶体管mps和n个晶体管中的m个(m为1以上的自然数)晶体管对负载200进行驱动的方式进行控制。也可以设为控制部103以在启动后由输出晶体管mps、mpl和n个晶体管对负载200进行驱动的方式进行控制。

[0178]

实施方式6.

[0179]

图15是表示实施方式6的运算放大器520的结构的图。

[0180]

运算放大器520具备差动放大部101、输出级102以及反馈电阻部500。差动放大部101及输出级102与在实施方式1中说明的内容同样,因此不重复说明。

[0181]

反馈电阻部500具备反馈电阻r1、r2、r12、r22、r1_s、r2_s、r12_s、r22_s和开关swr1、swr2、swr12、swr22、swr1s、swr2s、swr12s、swr22s。反馈电阻r1的电阻值大于反馈电阻r1_s的电阻值。反馈电阻r2的电阻值大于反馈电阻r2_s的电阻值。反馈电阻r12的电阻值

大于反馈电阻r12_s的电阻值。反馈电阻r22的电阻值大于反馈电阻r22_s的电阻值。

[0182]

在输出端子out与地电源agnd之间,电阻r1、开关swr1、电阻r2以及开关swr2串联连接。在输出端子out与地电源agnd之间,电阻r12、开关swr12、电阻r22以及开关swr22串联连接。

[0183]

在输出端子out与地电源agnd之间,电阻r1_s、开关swr1_s、电阻r2_s以及开关swr2_s串联连接。在输出端子out与地电源agnd之间,电阻r12_s、开关swr12_s、电阻r22_s以及开关swr22_s串联连接。

[0184]

对于开关swr1、swr2、swr12、swr22,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关swr1、swr2、swr12、swr22变为导通。在启动完成控制信号ct1为低电平时,开关swr1、swr2、swr12、swr22变为断开。

[0185]

对于开关swr1s、swr2s、swr12s、swr22s,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关swr1s、swr2s、swr12s、swr22s变为断开。在启动完成控制信号ct1为低电平时,开关swr1s、swr2s、swr12s、swr22s变为导通。

[0186]

控制部103在启动时,将开关sw0设为断开,将开关swp设为断开,将开关swr1、swr2、swr12、swr22设为断开,将开关swr1s、swr2s、swr12s、swr22s设为导通。其结果,尾电流仅为ibias0,只有输出晶体管mps被驱动。电流从输出端子out通过电阻r1_s和r2_s流动,并且电流通过电阻r12_s和r22_s流动。

[0187]

控制部103在启动后,将开关sw0设为导通,将开关swp设为导通,将开关swr1、swr2、swr12、swr22设为导通,将swr1s、swr2s、swr12s、swr22s设为断开。其结果,尾电流成为ibias0+ibias_s0,输出晶体管mps和mpl被驱动。电流从输出端子out通过电阻r1和r2流动,并且电流通过电阻r12和r22流动。

[0188]

此外,在上述的实施方式中,设为反馈电阻部除了包括第一路径l1和第二路径l2以外,还包括2个路径。控制部103以在启动时使电流流过第一路径l1和2个路径中的1个路径、使电流不流过第二路径l2和2个路径中的剩余的1个路径的方式进行控制。控制部103以在启动后使电流流过第二路径l2和2个路径中的剩余的1个路径、使电流不流过第一路径l1和2个路径中的1个路径的方式进行控制。2个路径中的1个路径的电阻小于2个路径中的剩余的1个的电阻。不限定于上述的实施方式,还包括如下的变形例。

[0189]

反馈电阻部除了包括第一路径l1和第二路径l2以外,还包括n个路径。控制部103以在启动时使电流流过第一路径l1和n个路径中的m个路径、使电流不流过第二路径和n个路径中的剩余的(n

‑

m)个路径的方式进行控制。控制部103以在启动后使电流流过第二路径l2和n个路径中的剩余的(n

‑

m)个路径、使电流不流过第一路径l1和n个路径中的m个路径的方式进行控制。n个路径中的m个路径的电阻小于n个路径中的剩余的(n

‑

m)个的电阻。

[0190]

实施方式7.

[0191]

图16是表示实施方式7的运算放大器720的结构的图。

[0192]

运算放大器720具备差动放大部701、输出级102以及反馈电阻部100。输出级102及反馈电阻部100与在实施方式1中说明的内容同样,因此不重复说明。

[0193]

差动放大部701与实施方式1同样地,具备构成差动对的nmos晶体管mn1、mn2、构成有源负载的pmos晶体管mp1、mp2以及尾电流源t0。

[0194]

差动放大部701还具备尾电流源t0_s1(第二尾电流源)、尾电流源t0_s2(第三尾电

流源)、开关sw0_1(第三开关)以及开关sw0_2(第四开关)。

[0195]

在连接有nmos晶体管mn1的另一端的节点ndf与地电源agnd之间,开关sw0_1与尾电流源t0_s1串联连接。尾电流源t0_s1输出尾电流ibias_s0。

[0196]

在连接有nmos晶体管mn2的另一端的节点ndb与地电源agnd之间,开关sw0_2与尾电流源t0_s2串联连接。尾电流源t0_s2输出尾电流ibias_s0。

[0197]

在此,为了使差动放大部101可靠地进行动作,需要不使流过晶体管mn1、mn2的电流成为0以下。为此,需要满足以下的条件。

[0198]

ibias0>2

×

ibias_s0

···

(9)

[0199]

对于开关sw0_1、sw0_2,利用启动完成控制信号ct1进行控制。在启动完成控制信号ct1为高电平时,开关sw0_1、sw0_2变为导通。在启动完成控制信号ct1为低电平时,开关sw0_1、sw0_2变为断开。

[0200]

控制部103在启动时,将开关sw0_1、sw0_2设为断开,将开关swp设为断开,将开关swr1、swr2设为断开,将开关swr1s、swr2s设为导通。其结果,尾电流仅为ibias0,只有输出晶体管mps被驱动。电流从输出端子out通过电阻r1_s和r2_s流动。

[0201]

控制部103在启动后,将开关sw0_1、sw0_2设为导通,将开关swp设为导通,将开关swr1、swr2设为导通,将swr1s、swr2s设为断开。其结果,尾电流成为ibias0+2

×

ibias_s0,输出晶体管mps和mpl被驱动。电流从输出端子out通过电阻r1和r2流动。

[0202]

应认为本次公开的实施方式在所有方面均是例示,而不是限制性的。本发明的范围不是由上述的说明表示,而是由权利要求书表示,意图包括与权利要求书均等的含义及范围内的所有变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1