一种定时器开关数据采集系统的制作方法

1.本发明涉及数据信号采集和处理领域,更具体的说,涉及一种定时器开关数据采集系统。

背景技术:

2.目前,现有的定时器或其它类似的通断控制产品功能复杂,控制方法多样,包括带可编程定时、学习型、倒计时、光控、随机、wifi、rf(射频)等控制手段。

3.当这些控制手段在执行时,如何纠错及验证功能的执行情况是否达到预期设定的执行,执行功能是否在符合设计输入及客户要求,是否稳定不被其它不确定因素干扰等,现有技术通常是采用工作人员进行长时间的监测,或者采用定制设备配合人员进行数据采集与验证。

4.目前,亟需一种在对定时器产品进行长周期的验证时可记录可观察的可分析的通用数据采集设备来进行验证纠错,实现无需人员看护。

技术实现要素:

5.本发明的目的是提供一种定时器开关数据采集系统,解决现有技术中对于定时器产品的验证试验的无人化监测的问题。

6.为了实现上述目的,本发明提供了一种定时器开关数据采集系统,包括电源转换模块、信号转接模块和数据采集模块:

7.所述电源转换模块,一端与定时器产品连接,一端与信号转接模块连接,采集定时器产品输出的交流开关信号,并转换为直流电平通断信号发送给信号转接模块;

8.所述信号转接模块,与数据采集模块连接,将直流电平通断信号合并,转换为高低电平信号发送给数据采集模块;

9.所述数据采集模块,将高低电平信号转换为数字信号,根据数字信号判断定时器产品的开关通断状态,同步输出对应时间,对相应的定时器产品通断进行记录供处理及显示。

10.在一实施例中,所述数据采集模块,设置数字滤波器,通过调整数字滤波器的时钟周期,过滤小于滤波器时钟周期的采样脉冲信号,进行有效采样。

11.在一实施例中,所述电源转换模块的数量为多个,每一个电源转换模块与一个定时器产品连接,采集对应的定时器产品输出的交流开关信号。

12.在一实施例中,当数据采集模块检测到单个电源转换模块对应的高低电平信号发生高至低或低至高的转换时,对所有的电源转换模块采集的信号进行检测。

13.在一实施例中,所述电源转换模块,包括供电单元、采集单元和ac/dc转换单元:

14.所述供电单元,对定时器产品供电;

15.所述采集单元,采集定时器产品输出的交流开关信号,并发送给ac/dc转换单元;

16.所述ac/dc转换单元,将交流开关信号转换为直流电平通断信号后输出。

17.在一实施例中,当定时器产品输出为断开状态,对应的采集单元无交流开关信号,对应的ac/dc转换单元无直流电平通断信号,信号转接模块输出低电平信号;

18.当定时器产品输出为接通状态,对应的采集单元输出交流开关信号,对应的ac/dc转换单元输出直流电平通断信号,信号转接模块输出高电平信号。

19.在一实施例中,所述信号转接模块,包括转接板和接线盒:

20.所述转接板,一端与电源转换模块连接,另一端与接线盒连接,将多个电源转换模块输出的直流电平通断信号汇集转接后输出至接线盒;

21.所述接线盒,将多个直流电平通断信号合并,并且转换为高低电平信号后发送至数据采集模块。

22.在一实施例中,所述ac/dc转换单元与数据采集模块之间,安装有下拉电阻,通过调整下拉电阻的阻值,将ac/dc转换单元内部电容的剩余能量进行快速释放;

23.其中,下拉电阻的阻值为50到100ω。

24.在一实施例中,所述数据采集模块,包括pci板卡和上位机;

25.所述pci板卡,将高低电平信号转换为数字信号;

26.所述上位机,根据数字信号判断定时器产品的开关通断状态。

27.在一实施例中,所述pci板卡,设置数字滤波器,通过编程控制滤波的指定时间间隔,过滤小于滤波器时钟周期的采样脉冲信号,进行有效采样;

28.滤波器时钟周期为指定时间间隔的持续时间的一半;

29.所述指定时间间隔,包括:160ns、10.24us和5.12ms。

30.在一实施例中,所述电源转换模块的数量为96个;

31.在一实施例中,所述接线盒为scb

‑

100接线盒或cb

‑

50/cb

‑

50lp接线盒,通过sh100

‑

100

‑

f柔性线缆或r1005050带状线缆与pci板卡连接。

32.本发明提供的定时器开关数据采集系统,基于pc的数据采集,通过模块化硬件、应用软件和计算机的结合,通过对定时器产品的通断信号进行数据信号采集、处理,监控外接定时器产品的工作状态,同时通过调节下拉电阻阻值、设置数字滤波器进行有效采样,从而实现对定时器产品测试环境的无人化、高精度、高准确度监控。

附图说明

33.本发明上述的以及其他的特征、性质和优势将通过下面结合附图和实施例的描述而变的更加明显,在附图中相同的附图标记始终表示相同的特征,其中:

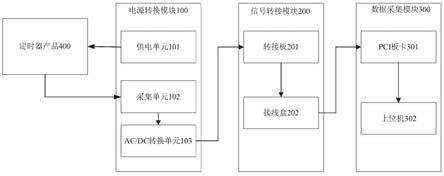

34.图1揭示了根据本发明一实施例的定时器开关数据采集系统的原理框图;

35.图2揭示了根据本发明一实施例的定时器开关数据采集系统的连接示意图;

36.图3揭示了根据本发明一实施例的接线盒示意图;

37.图4揭示了根据本发明一实施例的接线盒与pci板的连接示意图;

38.图5揭示了根据本发明一实施例的pci板卡的原理示意图;

39.图6揭示了根据本发明一实施例的数字滤波时序图。

40.图中各附图标记的含义如下:

41.100电源转换模块;

42.101供电单元;

43.102采集单元;

44.103ac/dc转换单元;

45.200信号转接模块;

46.201转接板;

47.202接线盒;

48.300数据采集模块;

49.301pci板卡;

50.311输入输出接口;

51.312定时采样单元;

52.313数字滤波器;

53.314pci总线;

54.302上位机;

55.400定时器产品。

具体实施方式

56.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释发明,并不用于限定发明。

57.本发明提出的一种定时器开关数据采集系统,对民用定时器产品的通断进行数据信号采集、处理和监控,检查满足设计要求或按程序完成步骤。民用定时器产品包括家用和类似用途自动控制器定时器和定时开关的产品。

58.一般来说,数据采集是指从传感器和其它待测设备等模拟和数字被测单元中自动采集非电量或者电量信号,送到上位机中进行分析处理。数据采集系统是结合基于计算机或者其他专用测试平台的测量软硬件产品来实现灵活的、用户自定义的测量系统。

59.尽管数据采集系统根据不同的应用需求有不同的定义,但各个系统采集、分析和显示信息的目的却都相同。数据采集系统整合了信号、传感器、激励器、信号调理、数据采集设备和应用软件。

60.图1揭示了根据本发明一实施例的定时器开关数据采集系统的原理框图,图2揭示了根据本发明一实施例的定时器开关数据采集系统的连接示意图,如图1和图2所示的定时器开关数据采集系统,包括电源转换模块100、信号转接模块200和数据采集模块300:

61.所述电源转换模块100,一端与定时器产品400连接,一端与信号转接模块200连接,采集定时器产品400输出的交流开关信号,并转换为直流电平通断信号;

62.所述信号转接模块200,与数据采集模块300连接,将直流电平通断信号合并,转换为高低电平信号;

63.所述数据采集模块300,将高低电平信号转换为数字信号,根据数字信号判断定时器产品的开关通断状态,同步输出对应时间,对相应的定时器产品400的通断进行记录供处理及显示。

64.在图2所示的实施例中,电源转换模块100的数量为96个,集成为一个测试架,每一个电源转换模块100与一个定时器产品连接,采集对应的定时器产品输出的交流开关信号。

65.在图2所示的实施例中,电源转换模块100,包括供电单元101、采集单元102和ac/dc转换单元103:

66.所述供电单元101,对定时器产品供电;

67.所述采集单元102,采集定时器产品输出的交流开关信号,并发送给ac/dc转换单元103;

68.所述ac/dc转换单元103,将交流开关信号转换为直流电平通断信号后输出。

69.在本实施例中,交流开关信号为定时器产品输出的220/110v的交流信号,不能直接用于信号采集。

70.ac/dc转换单元103将220/110v的交流信号转换为5v的直流信号,便于后续转化为数据采集模块300可以接受的信号。因此,ac/dc转换单元103的组成结构没有特殊要求。

71.当被测的定时器产品输出为断开状态,对应的采集单元无220/110v的交流开关信号,对应的ac/dc转换单元无5v的直流电平通断信号,信号转接模块输出低电平信号,对应的数据采集模块的输入端即为低电平信号;

72.当被测的定时器产品输出为接通状态,对应的采集单元输出220/110v的交流开关信号,对应的ac/dc转换单元输出5v的直流电平通断信号,信号转接模块输出高电平信号,对应的数据采集模块的输入端即为高电平信号。

73.所述信号转接模块200,包括转接板201和接线盒202:

74.所述转接板201,一端与电源转换模块100连接,另一端与接线盒202连接,将多个电源转换模块输出的直流电平通断信号汇集转接后输出至接线盒202;

75.所述接线盒202,将多个直流电平通断信号合并,并且转换为高低电平信号后发送至数据采集模块300。

76.在本实施例中,转接板201用于将96个电源转换模块对应的被测定时器产品的5v的直流电平通断信号,汇集转接至接线盒202。

77.接线盒202,将96个5v的直流电平通断信号转换为高低电平信号后合并发送至数据采集模块300。

78.图3揭示了根据本发明一实施例的接线盒示意图,如图3所示,本实施例中的接线盒202的型号为scb

‑

100接线盒。

79.当ac/dc转换单元没有输出5v的直流电平通断信号,则接线盒202输出低电平信号;

80.当ac/dc转换单元有输出5v的直流电平通断信号,则接线盒202输出高电平信号。

81.在图2所示的实施例中,所述数据采集模块300,包括pci板卡301和上位机302;

82.所述pci板卡301,将高低电平信号转换为数字信号;

83.所述上位机302,根据数字信号判断定时器产品的开关通断状态。

84.pci板卡301,将高电平信号转换为数字信号(1),将低电平信号转换为数字信号(0)。

85.图4揭示了根据本发明一实施例的接线盒与pci板的连接示意图,在图4所示的实施例中,pci板卡301的型号为pci

‑

6509板卡,与接线盒202连接。接线盒202为scb

‑

100接线盒。

86.ac/dc转换单元103,对应数量为96个,每8个组成一个通路,通过转接板201与接线

盒202连接。

87.pci

‑

6509板卡,将采集的96通道的5v ttl/cmos数字i/o模块数据,经pci总线接pc上位机302。

88.上位机302,同步当前时间输出同步时钟,对被测定时器产品通断数据进行记录供处理。

89.更进一步的,上位机302,通过labview程序,采集信号数据输出,进行图型及数据通断状态及时间显示。

90.更进一步的,当上位机302检测到pic

‑

6509板卡的数字信号的转变(从0

‑

1)或(1

‑

0)时,意味着单个电源转换模块对应的高低电平信号发生高至低或低至高的转换,此时,对所有的96个电源转换模块采集的信号进行逐一状态检测更新。

91.在本实施例中,scb

‑

100接线盒与pci6509板卡,通过sh100m

‑

100m柔性线缆连接起来,可方便地接接数字i/o接接器并能更方便的扩展方案元件,并满足符合相关标准的电磁兼容(emc)规范。

92.在其他实施例中,接线盒202的型号为cb

‑

50/cb

‑

50lp接线盒,则cb

‑

50/cb

‑

50lp接线盒与pci6509板卡,通过r1005050带状线缆连接起来。

93.本发明提出的定时器开关数据采集系统,将被测定时器产品的强电信号状态,经过ac/dc转换为弱电信号状态,经过pci板卡采集得到数据经过处理后反馈强电信号状态,继而监控定时器产品的运行状态。

94.更进一步的,受制于ac/dc转换单元与pci板卡对高低电平的采样时差,定时器开关数据采集系统的采样精度受到影响,无法提高,采样精度在1

‑

10s。

95.原因在于,当ac/dc转换单元的输入端无电压时,内部电容有剩余能量,ac/dc转换单元输出端的外接电阻在10kω左右,ac/dc转换单元的输出电压降到pci板卡默认低电平2.2v时间约为10s左右。而外部定时器产品上电到输出高电平的时间约为0.3s。

96.本发明提出的定时器开关数据采集系统,在ac/dc转换单元103和数据采集模块300之间安装有下拉电阻,通过调整下拉电阻的阻值,将ac/dc转换单元内部电容有剩余能量尽快进行释放,从而,ac/dc转换单元103的输出电压的下降时间,接近或低于外部定时器产品上电到输出高电平的时间(约0.3s),从而提高了定时器开关数据采集系统的采样精度。

97.可选的,下拉电阻安装在ac/dc转换单元103和转接板201之间。

98.可选的,下拉电阻安装在接线盒202和转接板201之间。

99.可选的,下拉电阻安装在接线盒202和pci板301之间。

100.如图4所示的实施例中,pci6509板卡的i/o口配置为输入口,内部无上拉/下拉设置。

101.下拉电阻r1设置在转接板201和接线盒202之间。

102.本实施例中,下拉电阻r1的阻值范围为50到100ω。

103.此时,ac/dc转换单元103的输出电压的下降时间接近或低于外部定时器产品上电到输出高电平的时间(约0.3s)。

104.其中,当下拉电阻的阻值为100ω时,ac/dc转换单元的输出电压降到pci板卡默认低电平的时间为1s。

105.更进一步的,由于外接定时器产品的交流开关信号可能存在不稳定信号或虚假信号,或者整个定时器开关数据采集系统中存在噪音信号,如果不对其进行处理,会引起对外接定时器产品的工作状态的误判。

106.因此,本发明的数据采集模块300,设置数字滤波器313,通过调整数字滤波器的时钟周期,过滤时间间隔小于滤波器时钟周期的采样信号脉冲,进行有效采样。

107.图5揭示了根据本发明一实施例的pci板卡的原理示意图,如图5所示的pci板卡301,包括输入输出接口311、定时采样单元312、数字滤波器313和pci总线314。

108.输入输出接口311,接收信号转接模块200的高低电平信号作为外部输入信号并发送给定时采样单元312;

109.定时采样单元312,根据采样时钟对外部输入信号进行采样,形成外部输入采样信号并发送给数字滤波器313;

110.数字滤波器313,对外部输入采样信号进行数字滤波,过滤小于滤波器时钟周期的外部输入采样信号,形成有效采样信号;

111.pci总线314,将有效采样信号发送至上位机302。

112.在本实施例中,pic

‑

6509板卡的数字滤波器,通过编程控制滤波的指定时间间隔,过滤小于滤波器时钟周期的无效采样脉冲信号,减少检测次数的更改及过程。

113.滤波器时钟周期为指定时间间隔的持续时间的一半。

114.指定时间间隔,有多种时间可选,包括但不限于:160ns、10.24us和5.12ms。

115.本实施例中,指定时间间隔采用10.24us,则数字滤波器313的时钟周期为5.12us,外部输入信号变化大于5.12us宽度,即为有效采样。

116.图6揭示了根据本发明一实施例的数字滤波时序图,如图6所示,外部输入信号即输入至数据采集模块300的数字滤波器313的高低电平信号,通过采样时钟信号进行采样,外部输入采样信号必须在滤波器时钟周期中(具体判断为两个滤波时钟的上升沿时间间隔),满足采样信号都为高电平脉冲或低电平脉冲,才是有效采样。

117.外部输入采样信号a、b和c均为在一个滤波器时钟周期的采样信号,其中,外部输入采样信号a和外部输入采样信号b对应于外部输入信号中圆圈部分的无效信号。

118.外部输入采样信号a为“hllhh”,即3个高电平(h)信号和2个低电平(l)信号,因此是无效采样。

119.外部输入采样信号b为“hllhh”,同样是3个高电平(h)信号和2个低电平(l)信号,因此也是无效采样。

120.外部输入采样信号c为“hhhhh”,全部是高电平(h)信号,因此是有效采样。

121.从而,本发明通过在pci板卡的数字滤波器设置时间间隔,过滤了外部输入信号中的无效信号,进一步提高了采样准确性,减少了对定时器产品的开关通断状态出现误判的可能性。

122.本发明提供的定时器开关数据采集系统,基于pc的数据采集,通过模块化硬件、应用软件和计算机的结合,通过对定时器产品的通断信号进行数据信号采集、处理,监控外接定时器产品的工作状态,同时通过调节下拉电阻阻值、设置数字滤波器进行有效采样,从而实现对定时器产品测试环境的无人化、高精度、高准确度监控。

123.尽管为使解释简单化将上述方法图示并描述为一系列动作,但是应理解并领会,

这些方法不受动作的次序所限,因为根据一个或多个实施例,一些动作可按不同次序发生和/或与来自本文中图示和描述或本文中未图示和描述但本领域技术人员可以理解的其他动作并发地发生。

124.本领域技术人员将进一步领会,结合本文中所公开的实施例来描述的各种解说性逻辑板块、模块、电路、和算法步骤可实现为电子硬件、计算机软件、或这两者的组合。为清楚地解说硬件与软件的这一可互换性,各种解说性组件、框、模块、电路、和步骤在上面是以其功能性的形式作一般化描述的。此类功能性是被实现为硬件还是软件取决于具体应用和施加于整体系统的设计约束。技术人员对于每种特定应用可用不同的方式来实现所描述的功能性,但这样的实现决策不应被解读成导致脱离了本发明的范围。

125.如本申请和权利要求书中所示,除非上下文明确提示例外情形,“一”、“一个”、“一种”和/或“该”等词并非特指单数,也可包括复数。一般说来,术语“包括”与“包含”仅提示包括已明确标识的步骤和元素,而这些步骤和元素不构成一个排它性的罗列,方法或者设备也可能包含其他的步骤或元素。

126.上述实施例是提供给熟悉本领域内的人员来实现或使用本发明的,熟悉本领域的人员可在不脱离本发明的发明思想的情况下,对上述实施例做出种种修改或变化,因而本发明的保护范围并不被上述实施例所限,而应该是符合权利要求书提到的创新性特征的最大范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1