一种适用于低电压的带隙基准修调电路的制作方法

1.本发明涉及锂电池电源管理技术领域,具体涉及一种适用于低电压的带隙基准修调电路。

背景技术:

2.现有技术的直接用低阻抗poly或metal al fuse电阻连接可修调的电阻串联结构。在基准电压修调时,只能单向从最低电压开始往高电压方向修调基准电压。在测试开始时就必须先烧写修调基准电压值到目标值,才能得到比较合理的基准电压值,不然与基准相关的电路可能存在初始基准电压过低,导致测试与基准电压有联系的其他功能或电参数时存在测试功能或电参数异常,无法在烧写前先判断系统功能是否正常。同时存在fuse烧写电阻烧写后还存在不确定的阻抗,会因为后续的封装由于外界条件的沾污影响已经烧断的电阻值,直接影响基准电压值。不适用于高精度的基准电压电路。

3.后来出现有技术的改进方案采用mos开关管的开关来屏蔽或释放基准修调电阻值,并且通过修调逻辑单元,可以设置最大烧写位初始电阻被释放,使基准电压初始值就设定在中心值,解决了直接采用fuse电阻初始短接修调基准电阻存在初始基准值低,修调后的fuse电阻阻抗不确定影响基准电压值。参见图7,采用mos晶体管开关替代直接的低阻抗fuse电阻存在输入电压过低(在1.8v

‑

2.5v内)时,mos管开启导通电阻增大,影响基准电压值,在带隙基准电路输入低电压工作时会导致基准电压值增大,影响基准电压的一致性。输入低电压应用领域存局限性。在低电压电源输入情况下,不能实现很好的基准电压一致性。

技术实现要素:

4.本发明的目的是针对现有技术存在的不足,提供一种适用于低电压的带隙基准修调电路。

5.为实现上述目的,本发明提供了一种适用于低电压的带隙基准修调电路,包括:带隙基准修调电路,与输入电源vdd连接,用以产生基准电压vref、分压vber、控制电压信号vbp和控制电压信号vbn;振荡器电路,与所述输入电源vdd和带隙基准修调电路分别连接,用以根据基准电压vref和分压vber产生一个时钟信号clk;电压侦测电路,用以根据输入电源vdd和基准电压vref对所述输入电源vdd的电压进行侦测,并在所述输入电源vdd的电压低于设定阈值范围时,输出高电平的使能信号en;电荷泵电路,与电压侦测电路和振荡器电路分别连接,用以根据所述时钟信号clk和使能信号en对输入电源vdd进行升压,并获得升压后的电源vcc;逻辑电路,与输入电源vdd、电源vcc和带隙基准修调电路分别连接,用以接收所述控制电压信号vbp和控制电压信号vbn,并根据控制电压信号vbp和控制电压信号vbn输出修调信号,当所述输入电源vdd在设定阈值以上时,所述修调信号中的高电平为电源vdd,当所述输入电源vdd的电压低于设定阈值范围时,所述修调信号中的高电平为电源vcc,所述带

隙基准修调电路根据所述修调信号调整基准电压值vref。

6.进一步的,所述带隙基准修调电路包括依次连接的启动电路、带隙基准电路和修调电路rt,所述带隙基准电路包括由pmos晶体管p11、nmos晶体管n11、电阻r11、双极pnp晶体管q11、pmos晶体管p12、nmos晶体管n12、双极pnp晶体管q12组成widllar电流偏置电路,还包括源极与输入电源vdd连接的pmos晶体管p13,所述pmos晶体管p13的漏极依次与修调电路rt、电阻r12和电阻r13串联,所述电阻r13与双极pnp晶体管q13的发射极连接,所述双极pnp晶体管q13的集电极和基极均接地,所述基准电压vref产生于pmos晶体管p13的漏极与修调电路rt之间,所述分压vber产生于电阻r12和电阻r13之间。

7.进一步的,所述修调电路rt包括若干修调电阻,每一修调电阻的两端均并联有一pmos晶体管和一nmos晶体管,所述pmos晶体管和nmos晶体管的栅极分别与逻辑电路连接。

8.进一步的,所述逻辑电路包括若干修调逻辑驱动电路,每一修调逻辑驱动电路连接有电源切换电路,所述电源切换电路包括源极分别与电源vcc连接的pmos晶体管p25和pmos晶体管p26,所述pmos晶体管p25和pmos晶体管p26的栅极分别与pmos晶体管p26和pmos晶体管p25的漏极连接,所述pmos晶体管p25和pmos晶体管p26的漏极分别与nmos晶体管n25和nmos晶体管n26的漏极分别连接,所述nmos晶体管n25和nmos晶体管n26的源极均接地,且其栅极分别与修调逻辑驱动电路连接。

9.进一步的,所述电压侦测电路包括一端与输入电源vdd连接的电阻r41,所述电阻r41的另一端与电阻r42的一端和比较器cmp41的第一输入端连接,所述电阻r42的另一端接地,所述比较器cmp41第二输入端用于接入基准电压vref,当输入电源vdd与基准电压vref之差在设定阈值范围内时,所述比较器cmp41输出高电平的使能信号en。

10.进一步的,所述振荡器电路包括运算放大器op51,所述运算放大器op51的第一输入端用以接入分压vber,其输出端与nmos晶体管n51的栅极连接,所述nmos晶体管n51的源极与运算放大器op51的第二输入端和电阻r51的一端分别连接,所述电阻r51的另一端接地,所述nmos晶体管n51的漏极与pmos晶体管p51的漏极和基极以及pmos晶体管p52的基极分别连接,所述pmos晶体管p51和pmos晶体管p52的源极分别与输入电源vdd连接,所述pmos晶体管p52的漏极与电容c51的一端、nmos晶体管n52的漏极和比较器cmp51的第一输入端分别连接,所述电容c51的另一端和nmos晶体管n52的源极接地,所述比较器cmp51的第二输入端用于接入基准电压vref,且其输出端与nmos晶体管n52的栅极和t触发器的输入端分别连接,所述t触发器的输出端用于输出所述时钟信号clk。

11.进一步的,所述电荷泵电路包括逻辑组合电路和与逻辑组合电路连接的驱动开关电路,所述逻辑组合电路和驱动开关电路分别与开关电容升压电路分别连接,所述开关电容升压电路并联有二极管d5。

12.进一步的,所述逻辑组合电路包括奇数个首尾依次连接的反向器,位于首端的反向器的输入端用于输入使能信号en,且其输入端与与非门nand2_1、与非门nand2_3和与非门nand2_2的第一输入端分别连接,位于末端的反向器的输出端与开关电容分压电路连接,所述与非门nand2_1的第二输入端用于输入时钟信号clk,且其输出端与反向器inv_4的输入端连接,所述反向器inv_4的输出端与反向器inv_5和与非门nand2_3的第二输入端分别连接,所述反向器inv_5的输出端与与非门nand2_2的第二输入端连接,与非门nand2_2和与非门nand2_3的输出端分别与反向器inv_6和反向器inv_7的输入端分别连接,所述反向器

inv_6和反向器inv_7的输出端分别与驱动开关电路连接。

13.进一步的,所述驱动开关电路包括第一驱动开关电路和第二驱动开关电路,所述第一驱动开关电路包括栅极与反向器inv_6连接的pmos晶体管p61和nmos晶体管n61,所述pmos晶体管p61的源极与输入电源vdd和pmos晶体管p62的源极分别连接,所述pmos晶体管p61的漏极与pmos晶体管p62和nmos晶体管n62的栅极以及nmos晶体管n61的漏极分别连接,所述nmos晶体管n61 和nmos晶体管n62的源极接地,所述pmos晶体管p62和nmos晶体管n62的漏极均与开关电容升压电路连接;所述第二驱动开关电路包括栅极与反向器inv_7连接的pmos晶体管p64和nmos晶体管n63,所述pmos晶体管p63的源极与输入电源vdd和pmos晶体管p64的源极分别连接,所述pmos晶体管p63的漏极与pmos晶体管p64和nmos晶体管n64的栅极以及nmos晶体管n63的漏极分别连接,所述nmos晶体管n63 和nmos晶体管n64的源极接地,所述pmos晶体管p64和nmos晶体管n64的漏极均与开关电容升压电路连接。

14.进一步的,所述开关电容升压电路包括源极与输入电源vdd连接的pmos晶体管p65,所述pmos晶体管p65的栅极与所述位于末端的反向器的输出端连接,且其漏极依次正向连接有二极管d4、二极管d3、二极管d2和二极管d1,所述pmos晶体管p62和nmos晶体管n62的漏极与二极管d3和二极管d2之间连接有电容c63,所述pmos晶体管p64和nmos晶体管n64的漏极与二极管d4和二极管d3之间连接有电容c64,且其漏极与二极管d2和二极管d1之间连接有电容c2。

15.有益效果:本发明在采用mos开关管来控制修调带隙基准电压的基础之上,通过引入振荡器电路、电荷泵电路和电源切换电路等,在输入电源vdd偏低的情况下,提高mos开关管的控制电压,确保mos开关管能够充分导通,减小导通电阻对带隙基准修调电路中的电阻影响,有效的解决带隙基准电路在输入供电电源低电压状态下基准电压升高的问题,提高带隙基准电路在全电压输入下的基准电压的一致性。

附图说明

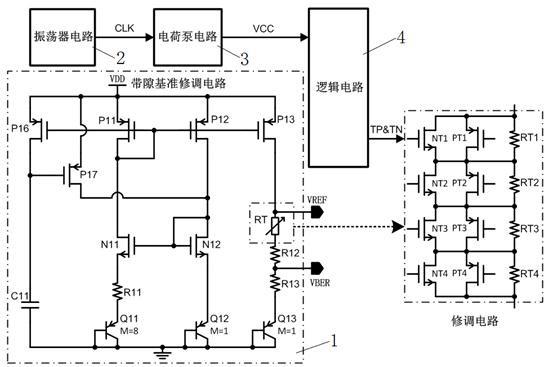

16.图1是本发明实施例的适用于低电压的带隙基准修调电路的原理示意图;图2是本发明实施例的带隙基准修调电路的原理图;图3是本发明实施例的逻辑电路的原理图;图4是本发明实施例的电压侦测电路的原理图;图5是本发明实施例的振荡器电路的原理图;图6是本发明实施例的电荷泵电路的原理图;图7是现有的带隙基准修调电路输入电压对应的基准电压曲线;图8是本发明实施例的带隙基准修调电路输入电压对应的基准电压曲线。

具体实施方式

17.下面结合附图和具体实施例,进一步阐明本发明,本实施例在以本发明技术方案为前提下进行实施,应理解这些实施例仅用于说明本发明而不用于限制本发明的范围。

18.如图1至6所示,本发明实施例提供了一种适用于低电压的带隙基准修调电路,包括带隙基准修调电路1、振荡器电路2、电压侦测电路、电荷泵电路3和逻辑电路4。

19.其中,带隙基准修调电路1与输入电源vdd连接,用以产生基准电压vref、分压

vber、控制电压信号vbp和控制电压信号vbn。其中,基准电压vref的初始值可设置为中心值。

20.振荡器电路2与输入电源vdd和带隙基准修调电路1分别连接,用以根据基准电压vref和分压vber产生一个时钟信号clk。

21.电压侦测电路用以根据输入电源vdd和基准电压vref对输入电源vdd的电压进行侦测,并在输入电源vdd的电压低于设定阈值范围时,输出高电平的使能信号en。

22.电荷泵电路3与电压侦测电路和振荡器电路2分别连接,用以根据时钟信号clk和使能信号en对输入电源vdd进行升压,并获得升压后的电源vcc。

23.逻辑电路4与输入电源vdd、电源vcc和带隙基准修调电路1分别连接,用以接收带隙基准修调电路1产生的控制电压信号vbp和控制电压信号vbn,并根据控制电压信号vbp和控制电压信号vbn输出修调信号,当输入电源vdd在设定阈值以上时,修调信号中的高电平为电源vdd,当输入电源vdd的电压低于设定阈值范围时,修调信号中的高电平为电源vcc,带隙基准修调电路1根据修调信号调整基准电压值vref。

24.具体的,参见图1和2,本发明实施例的带隙基准修调电路1包括依次连接的启动电路、带隙基准电路和修调电路rt。启动电路和带隙基准电路的主体结构均为现有技术,其中,启动电路包括pmos晶体管p16、pmos晶体管p17和电容c11,pmos晶体管p16和电容c11串联在输入电源vdd与gnd之间,pmos晶体管p17的栅极接在pmos晶体管p16和c1公共端。带隙基准电路包括pmos晶体管p11、pmos晶体管p12、nmos晶体管n11和nmos晶体管n12等,由pmos晶体管p11、nmos晶体管n11、电阻r11、双极pnp晶体管q11、pmos晶体管p12、nmos晶体管n12、双极pnp晶体管q12组成widllar电流偏置电路,还包括源极与输入电源vdd连接的pmos晶体管p13, pmos晶体管p13的漏极依次与修调电路rt、电阻r12和电阻r13串联,电阻r13与双极pnp晶体管q13的发射极连接,双极pnp晶体管q13的集电极和基极均接地,基准电压vref产生于pmos晶体管p13的漏极与修调电路rt之间,分压vber产生于电阻r12和电阻r13之间。在电路上电启动时,由于电容c11的正端电压不能突变,所以pmos晶体管p17的栅极电位为0v,pmos晶体管p17开启,输出电流给nmos晶体管n11和nmos晶体管n12的栅极,使其分别导通工作,widllar电流偏置电路产生ptat电流。pmos晶体管p16产生的电流对电容c11充电,当电容c11的正端电压达到vdd时,pmos晶体管p17彻底关断,启动电流为0a,同时widllar电流偏置电路建立完成并正常工作,由pmos晶体管p11镜像到pmos晶体管p13的ptat电流注入到修调电路rt、电阻r2、电阻r3和双极pnp晶体管q3串联支路中,输入电源vdd的电压在一定范围内时,可产生约1.2v的基准电压vref。

25.本发明实施例的修调电路rt优选包括若干修调电阻,修调电阻的具体数量可根据实际需要进行变化。参见图1,优选的修调电阻包括电阻rt1、电阻rt2、电阻rt3和电阻rt4,其中,电阻rt1的一端与pmos晶体管p13的漏极、nmos晶体管nt1的漏极和pmos晶体管pt1的源极分别连接,且其另一端与nmos晶体管nt1的源极、pmos晶体管pt1的漏极、nmos晶体管nt2的漏极、pmos晶体管pt2的源极和电阻rt2的一端分别连接,电阻rt2的另一端与nmos晶体管nt2的源极、pmos晶体管pt2的漏极、nmos晶体管nt3的漏极、pmos晶体管pt3的源极和电阻rt3的一端分别连接,电阻rt3的另一端与nmos晶体管nt3的源极、pmos晶体管pt3的漏极、nmos晶体管nt4的漏极、pmos晶体管pt4的源极和电阻rt4的一端分别连接,电阻rt4的另一端与nmos晶体管nt4的源极、pmos晶体管pt4的漏极和电阻r2的一端分连接,nmos晶体管

nt1、pmos晶体管pt1、nmos晶体管nt2、pmos晶体管pt2、nmos晶体管nt3、pmos晶体管pt3、nmos晶体管nt4、pmos晶体管pt4的栅极分别与逻辑电路4连接。逻辑电路4输出的修调信号控制上述nmos晶体管nt1、nmos晶体管nt2、nmos晶体管nt3、nmos晶体管nt4、pmos晶体管pt1、pmos晶体管pt2、pmos晶体管pt3和pmos晶体管pt4工作,来实现对电阻rt1、电阻rt2、电阻rt3和电阻rt4的屏蔽或释放。

26.参见图3,本发明实施例的逻辑电路4包括若干个修调逻辑驱动电路,每一修调逻辑驱动电路连接有一个电源切换电路。修调逻辑驱动电路和电源切换电路的数量与修调电阻的数量相同,一组修调逻辑驱动电路和电源切换电路控制一个修调电阻并联的nmos晶体管和pmos晶体管工作。具体的,修调逻辑驱动电路的结构为现有技术,其具体包括pmos晶体管p21、pmos晶体管p22、pmos晶体管p23、pmos晶体管p24、nmos晶体管n21、nmos晶体管n22、nmos晶体管n23、nmos晶体管n24和fuse电阻rf21等,pmos晶体管p21、pmos晶体管p22和nmos晶体管n21构成偏置电流源,pmos晶体管p21和nmos晶体管n21的栅极用于接入带隙基准修调电路1产生的控制电压信号vbp和控制电压信号vbn,设定pmos晶体管p21和pmos晶体管p22偏置电流相同并小于nmos晶体管n21的偏置电流。pmos晶体管p21和nmos晶体管n21串联,nmos晶体管n21的源极通过fuse电阻rf21短接到gnd。nmos晶体管n22的栅接pmos晶体管p21和nmos晶体管n21之间的公共端,和pmos晶体管p22构成共源放大器。pmos晶体管p23和nmos晶体管n23构成反相器,pmos晶体管p24和nmos晶体管n24构成反相器。初始态nmos晶体管n21电流大于pmos晶体管p21电流,nmos晶体管n22的栅极低电平,pmos晶体管p22与nmos晶体管n22的公共端为高电平;fuse电阻rf1烧断后,nmos晶体管n21下拉电流变为0a,nmos晶体管n22栅极为高电平,pmos晶体管p22与nmos晶体管n22的公共端为低电平。电源切换电路包括源极分别与电源vcc连接的pmos晶体管p25和pmos晶体管p26,pmos晶体管p25和pmos晶体管p26的栅极分别与pmos晶体管p26和pmos晶体管p25的漏极连接,pmos晶体管p25和pmos晶体管p26的漏极分别与nmos晶体管n25和nmos晶体管n26的漏极分别连接,nmos晶体管n25和nmos晶体管n26的源极均接地,且其栅极分别与修调逻辑驱动电路连接。具体的,nmos晶体管n25的栅极与pmos晶体管p24和nmos晶体管n24的栅极公共端连接,nmos晶体管n26的栅极与pmos晶体管p24和nmos晶体管n24的漏极公共端连接。

27.参见图4,本发明实施例的电压侦测电路包括一端与输入电源vdd连接的电阻r41,电阻r41的另一端与电阻r42的一端和比较器cmp41的第一输入端连接,电阻r42的另一端接地,比较器cmp41第二输入端用于接入基准电压vref。由于基准电压vref相对稳定,因此可通过输入电源vdd与基准电压vref之差可判断输入电源vdd的电压值,当输入电源vdd与基准电压vref之差在设定阈值范围内时,比较器cmp41输出高电平的使能信号en。一般情况下,可设定为在输入电源vdd为1.8至2.5v时,也就是与基准电压vref之差在0.6v至1.3v时,比较器cmp4输出高电平的使能信号en,从而使电荷泵电路3开始工作。

28.参见图5,本发明实施例的振荡器电路2包括运算放大器op51,运算放大器op51的第一输入端用以接入分压vber,其输出端与nmos晶体管n51的栅极连接,nmos晶体管n51的源极与运算放大器op51的第二输入端和电阻r51的一端分别连接,电阻r51的另一端接地,nmos晶体管n51的漏极与pmos晶体管p51的漏极和基极以及pmos晶体管p52的基极分别连接,pmos晶体管p51和pmos晶体管p52的源极分别与输入电源vdd连接,pmos晶体管p52的漏极与电容c51的一端、nmos晶体管n52的漏极和比较器cmp51的第一输入端分别连接,电容

c51的另一端和nmos晶体管n52的源极接地,比较器cmp51的第二输入端用于接入基准电压vref,且其输出端与nmos晶体管n52的栅极和t触发器的输入端分别连接,t触发器的输出端用于输出所述时钟信号clk。运算放大器op51输入vber电压,通过负反馈,加在电阻r51上的电压为vber,产生的电流为vber/r51,由pmos晶体管p51作为主镜转递出去。pmos晶体管p52电流为零温漂电流,给振荡器电容c51充电,当电容c51的电压达到vref电压值时,比较器cmp51输出控制nmos晶体管n52导通,将电容c51上的电荷释放,电压回到0v,完成一个振荡周期。比较器cmp51的输出接t触发器,产生一个50%占空比的时钟信号clk提供给电荷泵电路3。

29.参见图6,本发明实施例的电荷泵电路3包括逻辑组合电路和与逻辑组合电路连接的驱动开关电路,逻辑组合电路和驱动开关电路分别与开关电容升压电路分别连接,开关电容升压电路并联有二极管d5。当输入电源vdd在设定阈值范围以上时,逻辑组合电路、驱动开关电路和开关电容升压电路均不工作,输入电源vdd通过二极管d5后成为电源vcc。优选的逻辑组合电路包括奇数个首尾依次连接的反向器,图6中示意的3个反向器的电路结构,位于首端的反向器的输入端用于输入使能信号en,且其输入端与与非门nand2_1、与非门nand2_3和与非门nand2_2的第一输入端分别连接,位于末端的反向器的输出端与开关电容分压电路连接,与非门nand2_1的第二输入端用于输入时钟信号clk,且其输出端与反向器inv_4的输入端连接,反向器inv_4的输出端与反向器inv_5和与非门nand2_3的第二输入端分别连接,反向器inv_5的输出端与与非门nand2_2的第二输入端连接,与非门nand2_2和与非门nand2_3的输出端分别与反向器inv_6和反向器inv_7的输入端分别连接,反向器inv_6和反向器inv_7的输出端分别与驱动开关电路连接。

30.本发明实施例的驱动开关电路包括第一驱动开关电路和第二驱动开关电路,第一驱动开关电路与第二驱动开关电路的结构相同,具体的,第一驱动开关电路包括栅极与反向器inv_6连接的pmos晶体管p61和nmos晶体管n61,pmos晶体管p61的源极与输入电源vdd和pmos晶体管p62的源极分别连接,pmos晶体管p61的漏极与pmos晶体管p62和nmos晶体管n62的栅极以及nmos晶体管n61的漏极分别连接,nmos晶体管n61 和nmos晶体管n62的源极接地,pmos晶体管p62和nmos晶体管n62的漏极均与开关电容升压电路连接。第二驱动开关电路包括栅极与反向器inv_7连接的pmos晶体管p64和nmos晶体管n63,pmos晶体管p63的源极与输入电源vdd和pmos晶体管p64的源极分别连接,pmos晶体管p63的漏极与pmos晶体管p64和nmos晶体管n64的栅极以及nmos晶体管n63的漏极分别连接,nmos晶体管n63 和nmos晶体管n64的源极接地,pmos晶体管p64和nmos晶体管n64的漏极均与开关电容升压电路连接。

31.本发明实施例的开关电容升压电路包括源极与输入电源vdd连接的pmos晶体管p65,pmos晶体管p65的栅极与位于末端的反向器的输出端连接,且其漏极依次正向连接有二极管d4、二极管d3、二极管d2和二极管d1,pmos晶体管p62和nmos晶体管n62的漏极与二极管d3和二极管d2之间连接有电容c63,pmos晶体管p64和nmos晶体管n64的漏极与二极管d4和二极管d3之间连接有电容c64,且其漏极与二极管d2和二极管d1之间连接有电容c2。上述反向器inv_1、反向器inv_2和反向器inv_3构成的使能逻辑电路,输出控制pmos晶体管p65的开关,在vdd电压低于2.5v时,pmos晶体管p65导通。第一驱动开关电路输出具有驱动能力的50%占空比的开关电压波形vsw2,驱动电容c63一端电压在gnd和vdd之间变化。第二驱动

开关电路输出具有驱动能力的50%占空比开关电压波形vsw1,驱动电容c62、电容c64一端电压在gnd和vdd之间变化。vsw1和vsw2开关波形互为反向。交替开关使vsw3端的电压为2*vdd

‑

vd,vsw4端电压为3*vdd

‑

2*vd,vsw5端电压4*vdd

‑

3*vd。其中,vd为二极管正向导通电压。vsw5通过二极管d1整流后得到vcc电压为4*(vdd

‑

vd)。还可在d1的后端连接电阻r61和电容c61,由电阻r61与电容c61连接组成的rc滤波电路进行滤波。还可在rc滤波电路的后侧连接由pmos晶体管p66、pmos晶体管p67、pmos晶体管p68和pmos晶体管p69构成的钳位电路,将电源vcc的电压最终钳位在vdd+4*vgs,其中,vgs是钳位电路里面的每个pmos晶体管的栅极与源极之间的电压。输出的vcc电压给修调电路的输出端供电,使驱动修调电路的开关管栅极电位达到vcc电压,减小导通时的阻抗,在vdd低电压下,减小对修调电阻的阻值影响。具体参见图7和8,通过对比可以看出,本发明有效的解决带隙基准电路在输入供电电源低电压状态下基准电压升高的问题,提高带隙基准电路在全电压输入下的基准电压的一致性。

32.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,其它未具体描述的部分,属于现有技术或公知常识。在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1