动态偏置高PSRR低压差线性稳压器的制作方法

动态偏置高psrr低压差线性稳压器

技术领域

1.本发明涉及集成电路技术。

背景技术:

2.低压差线性稳压器一方面由于它面积较小,另一方面它的性能优势包括压降低、高psrr、带宽大、输出纹波电压小等,这些特点使得它被广泛应用于便携式电子设备当中。

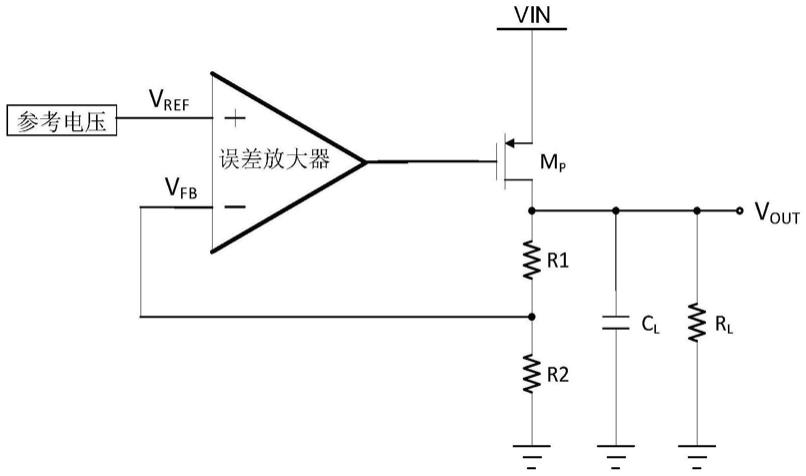

3.低压差线性稳压器一个重要的作用是可以隔绝外部供电电源的噪声,从而为所驱动的电路提供干净的电源。在高精度的电路系统中,这一点尤为重要。因此设计一个高电源抑制比的低压差线性稳压器是必要的。传统的低压差线性稳压器实现高的psrr是通过增加低频增益实现的,即需要高增益的运放,如图1,但该方法只是在低频段获得了较好的psrr特性,在中高频段完全依靠片外电容提高psrr。还有利用前馈技术,引入前馈通路,通过适当调节,消除反馈通路中的噪声,从而提高了psrr,结构如图2所示。但该结构引入了额外的放大器,使得电路功耗增加,设计变得复杂。因此,根据存在的问题,如何设计一种在中高频段仍具有高psrr的简易结构的低压差线性稳压器是值得考虑的。

技术实现要素:

4.针对以上缺陷,本发明所要解决的技术问题是,提出一种动态偏置高psrr低压差线性稳压器电路,使系统可以在较宽的频率范围获得较好的psrr值。

5.本发明解决所述技术问题采用的技术方案是,动态偏置高psrr低压差线性稳压器,包括误差放大器(2)、功率管(mp),功率管(mp)的栅端和误差放大器(2)的输出端连接,功率管(mp)的电流输出端作为末级输出端连接负载阻抗单元,其特征在于,

6.末级输出端通过电阻(6)连接参考点,参考点通过第七电流源(7)接地,功率管(mp)的栅端连接电流放大器(2)的输入端,电流放大器(2)的输出端连接参考点,参考点与误差放大器(2)的负性输入端连接;

7.一个动态偏置电路(3)的第一输入端接参考点,动态偏置电路(3)的第二输入端接功率管(mp)的栅端,动态偏置电路(3)的输出端接误差放大器的偏置信号端。

8.所述动态偏置电路(3)包括:

9.第一偏置mos管(mc),其源端接高电平,漏端作为动态偏置电路(3)的第二输入端接功率管(mp)的栅端,栅端接第三十电流源(i30)的电流输入端,功率管(mp)的栅端通过第一电阻(rd)接第三十电流源(i30)的电流输入端,第三十电流源(i30)的电流输出端接地;

10.第十mos管(m10),其源端接第三十一mos管(i31)的电流输出端,栅端接第一偏置mos管(mc)的栅端,漏端接第三十二mos管的电流输出端;

11.第十一mos管(m11),其源端接地,漏端作为动态偏置电路(3)的输出端和栅端相接;

12.第十二mos管(m12),其源端接第三十三电流源(i33)的电流输出端,漏端接第三十二电流源(i32)的电流输出端,栅端接电容(c)的一端,电容(c)的另一端作为动态偏置电路

(3)的第一输入端接参考点;

13.第三十一电流源(i31)、第三十二电流源(i32)、第三十三电流源(i33)的电流输入端接高电平。

14.第二偏置mos管(md),其源端接高电平,栅端和漏端接功率管(mp)的栅端。

15.所述电流放大器包括一个放大mos管(mp1)和第四十电流源(i40),放大mos管(mp1)的栅端接功率管的栅端,漏端通过第四十电流源(i40)接地,源端接高电平。

16.本发明的有益效果为,本发明的低压差线性稳压器,与现有提高psrr的低压差线性稳压器相比,引入了动态偏置技术,使得在负载变化时,系统的全部零极点跟随负载变化,即环路中的零点、其它极点能够自适应的跟随输出极点变化,使得系统在全负载范围具有较大的带宽并且维持稳定,本发明偏置电路的结构较现有改善psrr的电路结构简单,并且在中高频时依然有较高的psrr值。

附图说明

17.图1为高增益运放改善低频psrr低压差线性稳压器电路图。

18.图2为前馈技术提高psrr低压差线性稳压器电路图。

19.图3为动态偏置高psrr低压差线性稳压器电路图。

20.图4为实施例1的电路图。

21.图5为实施例2的电路图。

具体实施方式

22.如图3所示,本发明的动态偏置高psrr低压差线性稳压器包括:参考电压单元1、误差放大器单元2、动态偏置电路3、电流放大器单元4、pmos功率管mp单元5、电阻rc单元6、第七电流源i70单元7和负载阻抗单元8。误差放大器的输出端接功率管mp的栅极和电流放大器的输入,误差放大器的正端接参考电压vref,误差放大器的负端接反馈电压vfb,所述pmos功率管源极接电源电压vin,漏极与电阻rc的一端、负载阻抗的一端接输出电压vout,所述负载阻抗的另一端接地,所述电阻rc的另一端、第七电流源i70的一端、电流放大器的输出接电压vfb,所述第七电流源i70的另一端接地,所述动态偏置电路的输入接电压vfb,输出接误差放大器和功率管的栅极。

23.为方便对照附图理解,以下以图中的标记作为器件的简称,例如,mos管m1简写为m1。

24.图4示出了第一个实施例,误差放大器单元2包括mos管m0、m1、m2、m3、m4、m5、m6、m7、m8、m9,电阻r1、r2、ro1,电流源i20。mos管m0的栅极接参考电压,源极与mos管m1的源极接mos管m2的漏极,漏极接mos管m3的源极和电阻r1的一端,所述mos管m1的栅极接vfb,漏极接mos管m4的源极和电阻r2的一端,所述电阻r1和电阻r2的另一端接电源vin,所述mos管m3、m4的栅极接vbp,m3的漏极接电阻ro1的一端和mos管m5的漏极、源极、mos管m6的栅极,m4的漏极、电阻ro1的另一端、m6的漏极接vo1,所述mos管m5、m6的源极分别接mos管m7、m8的漏极,所述mos管m2、m7、m8的源极接地,栅极接vbn,所述mos管m9的栅极接vo1,源极接地,漏极和电流源i20的一端接vo2,所述电流源i20的另一端接vin。

25.本发明的动态偏置电路单元3包括mos管mc、m10、m11、m12,电阻rd,电容c以及电流

源i30、i31、i32、i33。所述mos管mc的栅极、电流源i30的一端、电阻rd的一端、mos管m10的栅极接vc,mos管mc的漏极、电阻rd的另一端接vo2,所述电流源i30的另一端接地,所述mos管m10的漏极、mos管m12的漏极、mos管m11的栅极和漏极和电流源i32的一端接vbn,所述电流源i32的另一端接地,mos管m10的源极接电流源i31的一端,所述电流源i31的另一端接vin,所述mos管m12的栅极接电容c的一端,源极接电流源i33的一端,所述电流源i33的另一端接vin,所述电容c的另一端接vfb。

26.本发明的电流放大器单元4的一种简单实现方式包括pmos管mp1、电流源i40,其中mos管mp1是功率管mp按宽度缩小一定倍数的同类型pmos管。所述pmos管mp1的栅极接vo2,源极接vin,漏极与电流源i40的一端接vfb,所述电流源i40的另一端接地。

27.电流源i32为误差放大器的第一级提供静态偏置,(i20

‑

i30)为第二级提供静态偏置,电流源i70为功率管提供静态偏置。当负载电流接近零时,电流源i70、i30、i32、i20都很小,vo2接近vin,mp、mc趋近关断,r

out

很大,输出点为主极点;此时mc、m10未能打开,imc、i31为零。vo1和vo2处极点频率相当并远远高于主极点频率,系统带宽内只有单一极点。随着负载电流增加,一条快通路和一条慢通路共同对偏置电流有动态影响。快通路:负载电流增加,由于有限环路带宽和mp栅较大寄生电容原因vo2尚未反应,则vfb下降δv

fb

,由电容的高通特性,δv

fb

快速经电容c耦合到m12栅级上,此时m12打开,i33叠加到ibiasn。慢通路:负载电流增加,经环路反应到vo2点,mc打开,调整流过m9的电流,从而使r

o2

骤降,i31叠加到ibiasn,imc、ibiasn、mp1管的漏电流随负载电流增加,故r

o1

、r

o2

、r

out

减小,g

m1

、g

m2

、g

mp

增加,r

o1

的最大值被限制在ro1的一半。r

o1

、r

o2

、r

out

分别是误差放大器第一级、第二级及功率极的输出阻抗,g

m1

、g

m2

、g

mp

分别为各级跨导。所以,pout向高频移动、po1向高频移动的速度要落后于po2被移到很高频率点上速度。当电流继续增加直到m10、m12完全打开:ibiasn恒定,imc继续增加,g

m1

、r

o1

不变、r

o2

减少且之后随电流增加而减少的速度变慢、r

out

减小到最小drop voltage后则不再减少。

28.图5为第二个实施例,和图4相比,其动态偏置电路增加了mos管md。所述mos管md的栅极与漏极接vo2,源极接vin。较图4结构而言,图5增加的mos管md作vin的前馈通路,使得系统的高频段psrr特性变得更好,同时,imd随着负载电流的增加而增加,r

o2

和g

m2

变化速度更快,故po2移动到高频的速度变快,防止由于po2移动的较慢而使得系统带宽减小致使系统在中频段的电源抑制性能变差。

29.通过以上分析,负载变化时,系统的全部零极点跟随变化,使得系统在全负载范围具有较大的带宽并且维持稳定,这样就可以在较宽的频率保持较高的psrr。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1