高压调节器的制作方法

高压调节器

1.相关申请的交叉引用

2.本技术要求基于2021年2月5日提交的、申请号为102021000002618的意大利专利申请的优先权,该意大利专利申请的公开内容通过引用整体并入本文。

技术领域

3.本公开涉及一种高压调节器。

4.本公开涉及一种用于向非易失性存储器提供偏置电压的高压调节器。

背景技术:

5.在各种类型的闪速存储器装置中,nand型闪速存储器装置作为一种高容量数据存储介质得到了越来越多的应用。高压调节器用于向nand堆栈提供不同的电压电平。例如,闪速存储器的每个单元需要被编程以通过在浮置栅极中捕获电子来存储信息。编程操作是通过将强正电压驱动到控制栅极上以迫使电流从通道流过浮置栅极到达控制栅极来执行的。通常,需要不同电平的编程电压,使用高压调节器来提供不同电平的电压。

6.类似地,在读取操作和擦除操作期间也需要高压偏置电平。

7.更特别地,nand闪速存储器通常包括高压或hv线性调节器,其是能够输出高于电源电压的模拟电压的dac(数模转换器)块。

8.图1a示出根据现有技术的方法实现的用于nand闪速存储器的hv线性调节器。

9.hv线性调节器100包括第一级110,第一级110包括运算放大器opamp,用于接收参考电压vref和反馈电压vfeedback以输出对参考电压vref和反馈电压vfeedback之差进行放大的电压。hv线性调节器100进一步包括第二级120,第二级120插入在电荷泵电压vpump和地gnd之间并包括共源配置,该共源配置包括一系列的进一步电阻器r3和nmos晶体管m3,它们在内部节点x3处互连,进而连接到第三级130的nmos晶体管mout的栅极端子。第二级120的nmos晶体管m3的栅极电连接到第一级110的运算放大器opamp的输出。此外,第三级130的nmos晶体管mout插入在hv线性调节器100的电荷泵电压vpump与输出端子out之间,并且充当在电荷泵电路(未示出)的输出端子处获得的电荷泵电压vpump供应的源极跟随器级。

10.通常,第三级130的nmos晶体管mout和第二级120的nmos晶体管m3是高压晶体管。此外,运算放大器opamp通常仅包括低压晶体管。

11.最后,hv线性调节器100包括分压器140,分压器140由插入在输出端子out和接地gnd之间的一系列第一电阻器r1和第二电阻器r2形成,并且具有向运算放大器opamp提供反馈电压vfeedback的公共节点xfb。特别地,第一电阻器r1插入在公共节点xfb和接地gnd之间,并且第二电阻器r2插入在输出端子out和公共节点xfb之间。

12.数字信号总线可能改变r1或r2(或两者)电阻值以进行d/a(数模)转换,如图1b所示。在这种情况下,每个电阻器r1和r2包括多个电阻器r和多个使能mos晶体管,并且多个电阻器r中的每一个可以具有相同的电阻值或不同的电阻值。例如,每个电阻器r1和r2包括一

系列的多个电阻元件以及连接到电阻元件的不同互连节点的多个使能mos晶体管,以根据需要启用不同数量的电阻元件,使能mos晶体管连接到数字信号。

13.用于高压nmos晶体管的“高压”意指在编程步骤中的电压范围为5或6伏至24伏。高压的典型范围可以是7或8伏至20伏。

14.运算放大器opamp形成反馈网络,该反馈网络接收参考电压vref和反馈电压vfeedback,该反馈电压vfeedback是由分压器的r1和r2形成的电阻网络分压的电压。供应到第二级120的电流值i2nd由以下公式确定:

[0015][0016]

由于使用电荷泵电路来提供电流效率远低于1的电荷泵电压,因此最小化第二级120和第三级130的dc偏置电流是很重要的。更特别地,第二级120的dc偏置电流取决于以下值:hv线性调节器100的输出端子out处的输出电压vout的电平;以及第三级130的nmos晶体管mout的栅极端子和源极端子之间的电压值vgs(mout)和第二级120的进一步电阻器r3的值。

[0017]

当输出电压vout的电平根据调节器设置而变化时,电压值vgs(mout)和进一步电阻器r3的值会随着模型拐角和温度而变化。因此,为了降低电流值i2nd,第二级120的进一步电阻器r3的值将增加。

[0018]

然而,进一步电阻器r3值的增加导致hv线性调节器100整体的面积损失和寄生增加。

[0019]

为了避免增加这种电阻的大小,还可以使用电流镜。特别地,以三星电子有限公司名义申请的、公开号为kr 10-2009-0101739的韩国专利中公开了一种包括放大器和镜像电路的电压加法器。更特别地,根据该韩国专利申请,根据从放大器输出的电压形成电流路径,并且通过提供在电压端子与接地端子之间的镜像电路来控制电流,该镜像电路包括pmos或nmos晶体管。

技术实现要素:

[0020]

本发明的各个实施例涉及一种调节器,特别是向非易失性存储器提供偏置电压的高压线性调节器,该调节器包括能够降低电荷泵电压所供应的共源电流而不增加整个调节器面积占用并且允许使用具有低击穿电压的高压pmos晶体管的电流镜,这在nand闪存技术中很常见。

[0021]

在本发明的实施例中,该调节器包括:高压电源端子、低压电源端子、输出端子、接地端子和内部节点;输入放大器,插入在低压电源端子与接地端子之间,并且根据分别在其负输入端子和正输入端子提供的参考电压和反馈电压在第一中间输出节点处输出第一输出电压;镜像电路,分别在内部节点与接地端子之间以及在内部节点与调节器的第二中间输出节点之间形成两个电流路径;以及共源共栅块,耦合在高压电源端子与内部节点之间,并且响应于调节器的第二中间输出节点处的电压而操作,在该第二中间输出节点处的两个电流路径中的一个由镜像电路形成。

[0022]

调节器可以进一步包括输出级(output stage),该输出级包括:最终晶体管(final transistor),插入在调节器的高压电源端子和输出端子之间,用作源极跟随器级,

该最终晶体管具有与调节器的第二中间输出节点连接的控制端子;以及分压器级,由插入在调节器的输出端子与调节器的接地端子之间的一系列第一电阻器和第二电阻器形成,并且具有向输入放大器提供反馈电压的公共节点。更特别地,最终晶体管具有耦合到第二中间输出节点的栅极端子以及电阻器反馈网络。

[0023]

此外,调节器可以进一步包括共源晶体管,该共源晶体管插入在第二中间输出节点与接地端子之间,并且具有连接到第一中间输出节点的栅极端子。

[0024]

利用根据本技术的调节器拓扑结构,调节器第二级的偏置电流即流经共源晶体管的漏极端子的电流由镜像电路的输入端子处的偏置电流确定。

[0025]

在本发明的另一实施例中,耦合到镜像电路的输入端子的偏置电流由附加晶体管生成,该附加晶体管的漏极端子耦合到镜像电路的输入端子,其源极端子与地耦合,并且其栅极端子耦合到输入放大器的第二内部节点。

[0026]

调节器可以进一步包括两个另外的共源共栅晶体管,另外的两个共源共栅晶体管分别连接在镜像电路的输入端子与附加晶体管的漏极之间以及第二中间输出端子与共源晶体管的漏极之间。这两个另外的共源共栅晶体管的栅极连接到偏置电压。

[0027]

调节器可以进一步包括预充电晶体管,该预充电晶体管与第一共源共栅晶体管并联地插入在高压电源端子与内部节点之间,并且其栅极接收预充电偏置电压。

[0028]

最后,调节器可以进一步包括米勒补偿电容器以及反馈电容器。

[0029]

在本发明的另一实施例中,调节器包括:放大器,适于将参考电压和反馈电压进行比较以生成中间电压;第一晶体管,耦合在中间节点与地之间,并且可根据中间电压进行操作;第二晶体管,耦合在高压电源和输出节点之间,并且可根据中间节点的电压电平进行操作;分压器级,耦合在输出节点与地之间,并且适用于生成反馈电压;第三晶体管,耦合在高压电源与内部节点之间,并且可根据中间节点的电压电平进行操作;以及镜像电路,耦合到内部节点,并且适于生成从内部节点流向地的第一电流以及从内部节点流向中间节点的第二电流。

附图说明

[0030]

根据下面的参照附图通过指示性和非限制性示例的方式给出的实施例描述,本公开的特征和优点将变得显而易见,其中

[0031]

图1a示意性地示出现有技术的高压调节器的电路图。

[0032]

图1b示意性地示出根据现有技术的方法的改变电阻器值以获得d/a转换的电路图。

[0033]

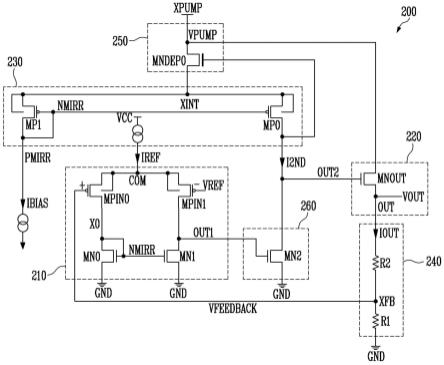

图2示意性地示出根据本发明的实施例的调节器的电路图。

[0034]

图3至图8示意性地示出根据本发明的可选实施例的调节器的电路图。

具体实施方式

[0035]

下面将参照附图详细描述本发明的各个实施例。虽然结合本发明的实施例示出和描述了本发明,但是对于本领域技术人员而言显而易见的是,可以在不脱离本发明的精神和范围的情况下进行各种修改。说明书和权利要求书中使用的术语和词语不应被解释为它们的普通意义或字典意义。另外,可以省略本领域众所周知的构造的详细描述以避免不必

要地模糊使本发明的要旨。

[0036]

图2示意性地示出根据本发明的实施例的用于非易失性存储器的调节器(特别是高压线性调节器)的电路图。

[0037]

调节器200包括:高压电源端子xpump,特别是接收在电荷泵电路(未示出)的输出端子处获得的电荷泵电压vpump;接地端子gnd;以及输入放大器210,根据分别在其负输入端子和正输入端子提供的参考电压vref和反馈电压vfeedback而在第一中间输出节点out1处输出第一输出电压。因此,输入放大器210也被表示为第一级。

[0038]

更特别地,输入放大器210插入在低电源电压vcc和接地端子gnd之间,并且包括电流生成器,该电流生成器连接在低电源电压vcc和公共节点com之间并且向该输入放大器210提供参考电流iref。

[0039]

此外,输入放大器210包括第一输入晶体管mpin0,第一输入晶体管mpin0插入在公共节点com和第一电路节点x0之间并在其栅极端子处接收反馈电压vfeedback,该第一输入晶体管的栅极端子是输入放大器210的正输入端子(+)。输入放大器210还包括第二输入晶体管mpin1,第二输入晶体管mpin1插入在公共节点com与输入放大器210的第一中间输出节点out1之间并在其栅极端子处接收参考电压vref,该第二输入晶体管的栅极端子是输入放大器210的负输入端子(-)。

[0040]

此外,输入放大器210包括:第一输出晶体管mn0,以二极管方式连接,并且耦合在第一电路节点x0与接地端子gnd之间;以及第二输出晶体管mn1,插入在第一中间输出节点out1与接地端子gnd之间。第二输出晶体管mn1进一步具有在镜像电路节点nmirr处连接到第一输出晶体管mn0的栅极端子的栅极端子。

[0041]

第一输入晶体管mpin0和第二输入晶体管mpin1可以是在图中所示的示例中各自的体端子(bulk terminal)连接到公共节点com的pmos晶体管。第一输出晶体管mn0和第二输出晶体管mn1可以是nmos晶体管。在实施例中,输入放大器210的所有晶体管可以是低压晶体管。在另一实施例中,第一输出晶体管mn0和第二输出晶体管mn1可以是高压晶体管。

[0042]

调节器200进一步包括镜像电路230,该镜像电路230在高压电源端子xpump和接地端子gnd之间形成电流路径,并且进一步连接到第二级260的共源晶体管mn2以及输出级220。输出级220包括插入在调节器200的高压电源端子xpump和输出端子out之间的最终晶体管mnout。因此,输出级220也被表示为第三级。

[0043]

更特别地,镜像电路230包括第一镜像晶体管mp0,第一镜像晶体管mp0插入在处于内部电压的内部节点xint与第二中间输出节点out2之间,并且具有连接到第二镜像晶体管mp1的栅极端子的栅极端子,该第二镜像晶体管mp1以二极管方式连接并且插入在内部节点xint与连接到偏置电流ibias的偏置电流生成器的另一镜像电路节点pmirr之间。第二中间输出节点out2进而连接到输出级220的最终晶体管mnout的栅极端子以及第二级260的共源晶体管mn2的漏极端子,并且向其提供第二级电流i2nd。

[0044]

最终,共源晶体管mn2插入在第二中间输出节点out2与接地端子gnd之间,并且具有连接到第一中间输出节点out1的栅极端子。因此,这种共源晶体管mn2从第二中间输出节点out2接收第二级电流i2nd。

[0045]

第一镜像晶体管mp0和第二镜像晶体管mp1可以是各自的体端子连接到内部节点xint的pmos晶体管。

[0046]

根据实施例,第一镜像晶体管mp0、第二镜像晶体管mp1、共源晶体管mn2和最终晶体管mnout可以是高压晶体管。

[0047]

调节器200进一步包括分压器级240,分压器级240由插入在输出端子out与接地端子gnd之间的一系列第一电阻器r1和第二电阻器r2形成,并且具有向输入放大器210提供反馈电压vfeedback的公共节点xfb。特别地,第一电阻器r1插入在公共节点xfb与接地端子gnd之间,并且第二电阻器r2插入在输出端子out与公共节点xfb之间。

[0048]

可以验证,第二级电流i2nd表示如下。

[0049][0050]

此处,w和l分别是相应晶体管的宽度和长度。

[0051]

第二级电流i2nd通常表示如下。

[0052][0053]

对于设计良好的电流镜,在通常情况下,当晶体管mp0和mp1具有相同的长度l时,第二级电流i2nd表示如上。

[0054]

为了简化对其余部分的描述,l(mp0)=l(mp1),而不限制本技术的范围。

[0055]

以这种方式,图2的调节器200通过适当地设计镜像晶体管的大小比w(mp0)/w(mp1),特别是相对于已知的解决方案通过在整体上对调节器200的面积影响很小的情况下减小这种大小比,能够在几乎没有面积损失的情况下减小第二级电流i2nd。

[0056]

此外,第二级电流i2nd现在独立于调节器200的输出电压电平vout以及电荷泵电压vpump。

[0057]

此外,连接到调节器200的电荷泵电路所产生的总电流等于ibias+i2nd+iout,该iout是分压器级240中流动的电流。

[0058]

调节器200还包括共源共栅块250中的第一共源共栅晶体管mndep0,该第一共源共栅晶体管mndep0耦合在高压电源端子xpump和镜像电路230(特别地,在镜像电路230的内部节点xint)之间,并且响应于第二中间输出节点out2的电压而操作,镜像电路230在第二中间输出节点out2处形成电流路径。

[0059]

在实施例中,第一共源共栅晶体管mndep0可以是nmos耗尽型晶体管。例如,第一共源共栅晶体管mndep0可以是高压nmos耗尽型晶体管。

[0060]

nmos耗尽型晶体管的阈值电压低于零。高压nmos耗尽型晶体管的典型电压阈值可以在-3v至-1v的范围内。

[0061]

以这种方式,共源共栅块250中的第一共源共栅晶体管mndep0能够防止镜像电路230中的晶体管的击穿,特别是防止第一镜像晶体管mp0的击穿。

[0062]

事实上,可用于nand闪存技术的高压pmos晶体管通常具有较低的结击穿电压(junction breakdown voltage)bv,通常在8v~10v左右,而相同技术中的高压nmos晶体管的结击穿电压bv高于24v。

[0063]

在共源共栅块250中没有第一共源共栅晶体管mndep0的情况下,第一镜像晶体管

mp0在其源极和漏极端子之间的电压差vsd以及其体和漏极端子之间的电压差vbd(均等于vpump-vout+vgs(mnout))高于其击穿电压bv时,可能会发生击穿。

[0064]

为了避免第一镜像晶体管mp0的击穿,将第一共源共栅晶体管mndep0插入在高压电源端子xpump与作为第一镜像晶体管mp0和第二镜像晶体管mp1的共源端子的内部节点xint之间,其中其控制端子或栅极端子连接到第一镜像晶体管mp0的漏极端子,其源极端子连接到第一镜像晶体管mp0的源极端子。以这种方式,通过以下等式来验证:

[0065]

vsd(mp0)=vbd(mp0)=-vgs(mndep0)

[0066]

第一共源共栅晶体管mndep0的栅-源电压差vgs等于第一镜像晶体管mp0的漏-源电压差vds和漏-体电压差vdb。

[0067]

这意指在调节器200的导通状态期间,第一镜像晶体管mp0的源-漏电压差vsd和体-漏电压差vbd由共源共栅块250的第一共源共栅晶体管mndep0的栅-源电压差vsg设置,该栅-源电压差vsg在-3v~-1v的范围内,该第一共源共栅晶体管mndep0是nmos耗尽型晶体管。

[0068]

因此,第一镜像晶体管mp0的源-漏电压差vsd和体-漏电压差vbd也被设置在1v~3v范围内,低于第一镜像晶体管mp0的击穿电压bv。

[0069]

以这种方式,图2的调节器200能够保护第一镜像晶体管mp0免受击穿电压bv的影响。

[0070]

图3示意性地示出根据本发明的可选实施例的调节器的电路图。

[0071]

图3的调节器200包括图2的调节器200中由相同附图标记表示的所有元件。

[0072]

根据可选实施例,调节器200进一步包括电流缓冲晶体管mn3,电流缓冲晶体管mn3插入在镜像电路230的另一镜像电路节点pmirr与接地端子gnd之间并接收偏置电流ibias。电流缓冲晶体管mn3的栅极端子连接到输入放大器210的镜像电路节点nmirr。

[0073]

在实施例中,电流缓冲晶体管mn3可以是高压nmos晶体管。

[0074]

以这种方式,在不增加dc电流消耗的情况下,调节器200的转换速率(slew rate)增加。除其它因素之外,高压调节器的转换速率最大值由提供到输出级220的最大电流值确定,而该最大电流值又由调节器200的镜像电路230的第二中间输出节点out2处的电流值确定,并且具有较高转换速率允许调节器的快速启动或快速输出下降恢复,这是调节器最重要的参数之一。

[0075]

如前所述,提供到第二中间输出节点out2的电流即第二级电流i2nd由ibias*w(mp0)/w(mp1)给出,并且可以通过增加偏置电流ibias或镜像pmos晶体管大小比的值来增加转换速率值。这种方法的主要缺点与调节器200整体的dc或静止状态下的电流消耗的相应增加有关。

[0076]

根据图3所示的可选实施例,偏置电流ibias是固定的dc电流,由电流缓冲晶体管mn3提供,电流缓冲晶体管mn3的栅极与第一输出晶体管mn0的栅极和漏极端子相连,mn3和mn0以这种方式处于电流镜像配置中。

[0077]

因此,偏置电流ibias的值取决于输入放大器210的参考电流iref,其dc值由下式给出。

[0078]

[0079]

类似地,可以验证,第二级电流i2nd表示如下。

[0080][0081]

其dc值由下式给出。

[0082][0083]

如前所述,所有镜像晶体管已经被视为具有相同的长度,这通常是电流镜设计良好的情况,而不限制本技术的范围。

[0084]

例如,调节器200可以根据以下大小来设计:w(mp0)=w(mp1)并且w(mn3)=w(mn0)。在这种情况下,第二级电流i2nd等于iref/2,即,参考电流iref是输入放大器210的dc偏置电流ibias。

[0085]

需要注意的是,在启动时或在转换速率条件下输出电压下降期间,反馈电压vfeedback远低于参考电压vref。这意指输入放大器210内部的第一输入晶体管mpin0汲取几乎所有的参考电流iref,而第二输入晶体管mpin1不汲取任何电流。

[0086]

以这种方式,第一输出晶体管mn0汲取所有参考电流iref(而不是dc条件期间的iref/2),而且电流缓冲晶体管mn3、第二镜像晶体管mp1和第一镜像晶体管mp0汲取的电流值等于参考电流iref(而不是dc条件期间的iref/2)。

[0087]

为此,在转换速率条件下第二中间输出节点out2处的电流值相对于dc电流值增加了两倍,而调节器200的dc消耗没有增加。

[0088]

因此,图3的调节器200具有高转换速率,允许快速启动和输出下降恢复操作。

[0089]

图4示意性地示出根据本发明的另一可选实施例的调节器的电路图。

[0090]

图4的调节器200包括图3的调节器200中由相同附图标记表示的所有元件。

[0091]

根据该可选实施例,调节器200的共源共栅块250进一步包括预充电晶体管mndep1,预充电晶体管mndep1与第一共源共栅晶体管mndep0并联插入,即,插入在高压电源端子xpump和镜像电路230的内部节点xint之间。此外,预充电晶体管mndep1的栅极端子接收预充电偏置电压vbias1,以确保在所有情况下启动。

[0092]

在实施例中,预充电晶体管mndep1可以是nmos耗尽型晶体管。例如,预充电晶体管可以是高压nmos耗尽型晶体管。

[0093]

可以验证,从第二中间输出节点out2约为0v的初始条件开始,调节器200中包括的所有晶体管处于关断状态。

[0094]

为简单起见,镜像电路230的pmos晶体管,特别是第一镜像晶体管mp0和第二镜像晶体管mp1具有相同的阈值电压vth(mp)。

[0095]

可以验证,在开始启动操作时,如果第一共源共栅晶体管mndep0的阈值电压的绝对值大于pmos晶体管的阈值电压的绝对值(|vth(mndep0)|》|vth(mp)|),则即使第二中间输出节点out2最初处于0v,第一共源共栅晶体管mndep0、第一镜像晶体管mp0和第二镜像晶体管mp1也将导通。另一方面,如果第一共源共栅晶体管mndep0的阈值电压的绝对值小于pmos晶体管的阈值电压的绝对值(|vth(mndep0)|《|vth(mp)|),则第二中间输出节点out2处的初始电压值等于0v不足以导通第一共源共栅晶体管mndep0、第一镜像晶体管mp0和第二镜像晶体管mp1。

[0096]

然而,由于预充电晶体管mndep1的栅极端子连接预充电偏置电压vbias1,这种预充电偏置电压vbias1是具有能够在所有角落(corner)保证以下条件的值的正电压(》0v)就足够了。

[0097]

vbias1+|vth(mndep0)|》|vth(mp)|

[0098]

更特别地,预充电偏置电压vbias1可以是合适的模拟电压以满足上述关系;可选地,如果调节器200的逻辑使能信号的高态(high state)电压值保证上述关系,则该逻辑使能信号可以用作预充电偏置电压vbias1。

[0099]

以这种方式,图4的调节器200能够确保在所有条件下启动。

[0100]

需要注意的是,预充电偏压值vbias1应选择低于第二中间节点out2处的电压电平,以使预充电晶体管mndep1在调节器导通状态期间始终关断。以这种方式,预充电晶体管mndep1仅在调节器启动期间操作,并且在调节器200已经完成启动时自动关断。

[0101]

图5示意性地示出根据本发明的可选实施例的调节器的电路图。

[0102]

图5的调节器200包括图4的调节器200中由相同附图标记表示的所有元件。

[0103]

根据可选实施例,调节器200进一步包括补偿电容器cm,补偿电容器cm插入在镜像电路230的第二中间输出节点out2和输入放大器210的第一中间输出节点out1之间。

[0104]

可选地,如图6所示,补偿电容器cm插入在调节器200的输出端子out和输入放大器210的第一中间输出节点out1之间。

[0105]

补偿电容器cm作为米勒电容器(miller capacitor),连接到输入放大器210,根据图5的实施例,其由镜像电路230驱动,根据图6的实施例,其由输出级220驱动,该输出级220是可以提供更多电流的源极跟随器。

[0106]

以这种方式,图5和图6的调节器200能够确保稳定的反馈条件。

[0107]

对于本领域技术人员而言将显而易见的是,在不偏离本技术的思想的情况下,图5和图6的实施例中表示的频率补偿电容器可以由一系列的补偿电容器和补偿电阻器或者任何其它频率补偿布置代替。

[0108]

图7示意性地示出根据本发明的可选实施例的调节器的电路图。

[0109]

图7的调节器200包括图6的调节器200中由相同附图标记表示的所有元件。

[0110]

根据可选实施例,调节器200进一步包括共源共栅配置中的两个nmos晶体管。

[0111]

具体地,调节器200包括:第二共源共栅晶体管mnc2,连接在第二中间输出节点out2与共源晶体管mn2的漏极之间,并且具有接收偏置电压vbias的栅极端子;以及类似的第三共源共栅晶体管mnc3,插入在另一镜像电路节点pmirr与电流缓冲晶体管mn3的漏极之间,并且具有接收偏置电压vbias的栅极端子。

[0112]

通过插入第二共源共栅晶体管mnc2和第三共源共栅晶体管mnc3,可以使电流缓冲晶体管mn3与输入放大器210的第一输出晶体管mn0匹配,并且使共源晶体管mn2与输入放大器210的第二输出晶体管mn1匹配。

[0113]

需要注意的是,使电流缓冲晶体管mn3与第一输出晶体管mn0匹配并且使共源晶体管mn2与第二输出晶体管mn1匹配意指这些晶体管的长度相同并且类型相同,例如它们是lv晶体管。

[0114]

这种匹配减少了调节器200的电压输入偏移的不利影响,从而提高了d/a转换精度。

[0115]

在实施例中,共源共栅晶体管mnc2和mnc3可以是高压晶体管并且偏置电压vbias可以是合适的模拟电压。

[0116]

以这种方式,共源晶体管mn2和电流缓冲晶体管mn3可以由低压晶体管构成,这提高了分别与第一输出晶体管mn0和第二输出晶体管mn1的匹配。

[0117]

还应注意的是,插入共源共栅晶体管mnc2和mnc3还具有增加调节器200的dc增益的有益效果。

[0118]

图8示意性地示出根据本发明的另一可选实施例的调节器的电路图。

[0119]

图8的调节器200包括图7的调节器200中由相同附图标记表示的所有元件。

[0120]

根据可选实施例,调节器200进一步包括反馈电容器cf,反馈电容器cf插入在输出端子out与另一内部节点node_f之间,该另一内部节点node_f对应于电流缓冲晶体管mn3与第三共源共栅晶体管mnc3之间的连接节点。

[0121]

以这种方式,当输出端子out下降时,另一内部节点node_f就会突然下降,因为它是通过反馈电容器cf与输出端子out处的电压电容性耦合的。由于第三共源共栅晶体管mnc3的栅-源电压差vgs的相应增加,这种另一内部节点node_f的突然下降导致偏置电流ibias突然增加到其稳态值以上。反过来,偏置电流ibias的突然增加导致第二级电流i2nd突然增加到其稳态值以上,从而使第二中间输出节点out2快速增加。

[0122]

最终,由于反馈电容器cf导致第二中间输出节点out2的快速增加,调节器200的输出端子out的下降快速恢复。

[0123]

以这种方式,图8的调节器200具有改进的下降恢复性能。

[0124]

前述调节器使用电流镜以及用来保护这种电流镜(特别是其第一镜像晶体管)免受击穿电压bv影响的共源共栅,该电流镜允许通过降低其第二级电流来使dc偏置电流最小化而不会导致面积损失和寄生增加。

[0125]

此外,通过使用缓冲晶体管,可以提高调节器的转换速率,以允许这种调节器快速启动和快速恢复输出下降。

[0126]

还可以使用合适的预充电晶体管来确保调节器在所有条件下正确启动,并且米勒电容器可以使反馈调节器稳定。

[0127]

最后,可以提供共源共栅配置以最小化调节器偏移,并且可以插入另外的反馈电容器以进一步提高调节器的下降恢复性能。

[0128]

从上文可以理解,尽管为了说明的目的已经在本文中描述了本发明的特定实施例,但是在不偏离本发明的精神和范围的情况下可以进行各种修改。因此,本发明不受所附权利要求书的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1