一种验证I2C总线噪声容限的夹具的制作方法

一种验证i2c总线噪声容限的夹具

技术领域

1.本实用新型涉及通讯技术领域,尤其涉及一种验证i2c总线噪声容限的夹具。用于验证在不同电源噪声大小的情况下i2c电路能否正常工作。主要用于研发阶段验证i2c电路电源噪声对clock和data的影响。

背景技术:

2.为了保证i2c电路能够正常工作,就需要进行不同环境下的验证,比如高温低温等极端环境,在不同的环境下,i2c电路的电源噪声会随环境的变化而变大或变小,而正常的验证是无法进行这种极端验证的,那就需要变换思维,改用某种方式去替代这种极端环境下引起电源噪声的变化差异,那就通过电源噪声源注入的方式进行,通过这种方式就可以验证出不同电源噪声大小下的i2c电路的工作情况。

技术实现要素:

3.本实用新型的目的在于针对上述现有技术的不足,提供一种成本低、操作方便的验证i2c总线噪声容限的夹具,通过注入电源噪声,模拟出不同环境下i2c电路能否正常工作的情况。

4.为解决上述问题,本实用新型所采取的技术方案是:

5.一种验证i2c总线噪声容限的夹具,包括第一输入端、第二输入端、第三输入端、第四输入端、第一输出端、第二输出端和第三输出端,所述第一输入端和第二输入端串联后与三极管q1的集电极相连,所述三极管q1的发射极与第一输出端相连,所述三极管q1的基极通过第一控制线与外部控制电路连接,所述第三输入端与三极管q2的集电极相连,所述三极管q2的发射极与第二输出端相连,所述三极管q2的基极通过第二控制线与外部控制电路连接,所述第四输入端与三极管q3的集电极相连,所述三极管q3的发射极与第三输出端相连,所述三极管q3的基极通过第三控制线与外部控制电路连接。

6.更进一步的技术方案是,所述第一控制线上串联有电阻r1,所述三极管q1的基极还连接有与第一控制线并联的第一接地线,所述第一接地线另一端接地,所述第一接地线上串联有电容c1。

7.更进一步的技术方案是,所述第二控制线上串联有电阻r2,所述三极管q2的基极还连接有与第二控制线并联的第二接地线,所述第二接地线另一端接地,所述第二接地线上串联有电容c2。

8.更进一步的技术方案是,所述第三控制线上串联有电阻r3,所述三极管q3的基极还连接有与第三控制线并联的第三接地线,所述第三接地线另一端接地,所述第三接地线上串联有电容c3。

9.更进一步的技术方案是,所述第一输入端、第二输入端、第三输入端、第四输入端、第一输出端、第二输出端和第三输出端均为3.5mm sma母头座子。

10.采用上述技术方案所产生的有益效果在于:实现起来容易,能够验证i2c电路电源

噪声的容限,并验证i2c总线在不同的噪声干扰下能否正常工作,此方案成本低廉,极具性价比。

附图说明

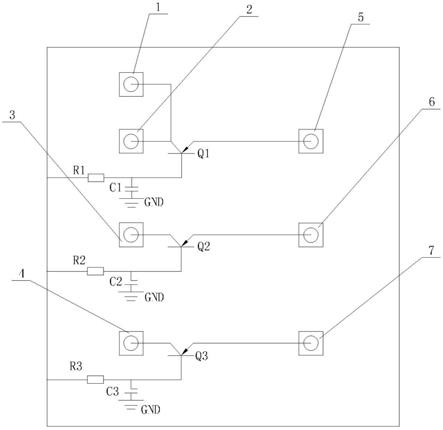

11.图1是本实用新型的示意图;

12.图中:1、第一输入端;2、第二输入端;3、第三输入端;4、第四输入端;5、第一输出端;6、第二输出端;7、第三输出端。

具体实施方式

13.下面结合附图和实施例对本实用新型的实施方式作进一步详细描述。以下实施例用于说明本实用新型,但不能用来限制本实用新型的范围。

14.如图1所示,一种验证i2c总线噪声容限的夹具,包括第一输入端1、第二输入端2、第三输入端3、第四输入端4、第一输出端5、第二输出端6和第三输出端7,所述第一输入端1和第二输入端2串联后与三极管q1的集电极相连,所述三极管q1的发射极与第一输出端5相连,所述三极管q1的基极通过第一控制线与外部控制电路连接,所述第三输入端3与三极管q2的集电极相连,所述三极管q2的发射极与第二输出端6相连,所述三极管q2的基极通过第二控制线与外部控制电路连接,所述第四输入端4与三极管q3的集电极相连,所述三极管q3的发射极与第三输出端7相连,所述三极管q3的基极通过第三控制线与外部控制电路连接。

15.所述第一控制线上串联有电阻r1,所述三极管q1的基极还连接有与第一控制线并联的第一接地线,所述第一接地线另一端接地,所述第一接地线上串联有电容c1。

16.所述第二控制线上串联有电阻r2,所述三极管q2的基极还连接有与第二控制线并联的第二接地线,所述第二接地线另一端接地,所述第二接地线上串联有电容c2。

17.所述第三控制线上串联有电阻r3,所述三极管q3的基极还连接有与第三控制线并联的第三接地线,所述第三接地线另一端接地,所述第三接地线上串联有电容c3。

18.所述第一输入端1、第二输入端2、第三输入端3、第四输入端4、第一输出端5、第二输出端6和第三输出端7均为3.5mm sma母头座子。

19.原理如下:电源噪声发生器与第一输入端1连接,产生带有噪声的干扰信号,i2c的3.3v电源由外部电路接入到第二输入端2,再由控制电路决定是否将三极管打开或者关断,从而将带有噪声注入的信号和3.3v一起送到第一输出端5。i2c的clock和data输入端分别接入到第三输入端3和第四输入端4,再由控制电路决定是否将三极管打开或者关断,从而决定是单独输出clock或data,还是两路同时输出,即可单独验证clock或者data,或者是两路同时打开同时进行验证。

20.当使用该方案进行验证时,首先将电源噪声发生器打开,设定一个噪声参数值,如100mv,再将i2c输入3.3v电源接入,第一控制线设定为高电平,从而打开三极管q1,将带有100mv噪声的3.3v电源输出到i2c电路中,之后将i2c的clock和data接入到第三输入端3和第四输入端4上,实现信号输入,再将第二控制线和第三控制线设定为高电平,实现i2c的clock和data信号的输出,此时可以观察带有100mv噪声的3.3v电源对i2c的clock和data的影响,如果i2c电路能够正常工作,即可证明100mv噪声对该电路没有影响,直至增大噪声到电路不能工作,记录此时的噪声输入值,即可得到i2c电路对电源噪声容限的承受能力,此

测试方案操作简单,易于实现,方便操作。

21.最后应说明的是:以上实施例仅用以说明本实用新型的技术方案,而非对其限制;尽管参照前述实施例对本实用新型进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1