射频识别整合集成电路以及射频识别码提供方法与流程

1.本发明关于一种射频识别(rfid)的技术,更进一步来说,本发明关于一种减少接脚数的射频识别整合集成电路以及射频识别码提供方法。

背景技术:

2.无线射频识别(英语:radio frequency identification,rfid)是一种无线通讯技术,可以通过无线电信号识别特定目标并读写相关数据,而无需识别系统与特定目标之间建立机械或者光学接触。无线电的信号是通过调成无线电频率的电磁场,把数据从附着在物品上的标签上传送出去,以自动辨识与追踪该物品。某些标签在识别时从识别器发出的电磁场中就可以得到能量,并不需要电池;也有标签本身拥有电源,并可以主动发出无线电波。标签包含了电子储存的信息,数公尺之内都可以识别。与条形码不同的是,射频标签不需要处在识别器视线之内,也可以嵌入被追踪物体之内。

3.无线射频识别的用途极为广泛,许多行业都运用了无线射频识别技术。将无线射频标签附着在一辆正在生产中的汽车,厂方便可以追踪此车在生产线上的进度。仓库可以追踪药品的位置。无线射频标签也可以附于牲畜与宠物上,方便对牲畜与宠物的积极识别(防止数只牲畜使用同一个身份)。无线射频识别的身份识别卡可以使员工得以进入建筑锁住的部分,汽车上的射频应答器也可以用来征收收费路段与停车场的费用。

4.然而,一般射频识别芯片在生产时,皆已经固定其识别码。以生产产品来说,若有20个产品,需要20个不同识别码的射频识别芯片。然而,此20个产品的销售状况有可能不同,导致20个不同识别码的射频识别芯片消耗量不同。若为了20个不同识别码分别生产20个不同识别码的射频识别芯片,对一般公司来说是极大的浪费。

技术实现要素:

5.本发明的一目的在于提供一种减少接脚数的射频识别整合集成电路以及射频识别码提供方法,用以生产同一个射频识别芯片,便可以用外部电路改变识别码,不受脚位数限制,电路更有弹性。

6.有鉴于此,本发明提供一种减少接脚数的射频识别整合集成电路以及减少接脚数的方法,此减少接脚数的整合集成电路,适用于一射频识别电路,其中该射频识别电路至少包括一谐振线圈以及一谐振电容,此减少接脚数的整合集成电路包括一第一输入输出接脚、一第二输入输出接脚以及一第三输入输出接脚,其中,当上述减少接脚数的整合集成电路启动时,判定第一输入输出接脚、第二输入输出接脚以及第三输入输出接脚是否耦接线圈,其中,根据耦接线圈的接脚以及未耦接线圈的接脚的电压状态,该减少接脚数的整合集成电路决定所输出的识别码。

7.本发明另外提供一种减少接脚数的射频识别码提供方法,适用于一射频识别整合集成电路,其中,该射频识别整合集成电路包括至少一第一输入输出接脚、一第二输入输出接脚以及一第三输入输出接脚,其中,该减少接脚数的射频识别码提供方法包括:当该减少

接脚数的整合集成电路启动时,判定该第一输入输出接脚、该第二输入输出接脚以及该第三输入输出接脚是否耦接线圈;以及根据耦接线圈的接脚以及未耦接线圈的接脚的电压状态,该减少接脚数的整合集成电路决定所输出的识别码。

8.依照本发明较佳实施例所述的减少接脚数的射频识别整合集成电路以及减少接脚数的射频识别码提供方法,上述任两个输入输出接脚之间具有一整流电路,故任两输入输出接脚耦接谐振线圈与谐振电容,并且接收到射频信号时,可以启动该减少接脚数的射频识别整合集成电路。

9.依照本发明较佳实施例所述的减少接脚数的射频识别整合集成电路以及减少接脚数的射频识别码提供方法,其中,当减少接脚数的整合集成电路启动时,判定该第一输入输出接脚、该第二输入输出接脚以及该第三输入输出接脚是否耦接线圈包括:减少接脚数的整合集成电路将第一输入输出接脚、第二输入输出接脚设定为浮动,该减少接脚数的整合集成电路在第三输入输出接脚输出指定电压,判断第一输入输出接脚、第二输入输出接脚的任一接脚是否随着该指定电压变动。

10.依照本发明较佳实施例所述的减少接脚数的射频识别整合集成电路以及减少接脚数的射频识别码提供方法,其中,当该减少接脚数的整合集成电路启动时,判定该第一输入输出接脚、该第二输入输出接脚以及该第三输入输出接脚是否耦接线圈更包括:该减少接脚数的整合集成电路判断该第一输入输出接脚、该第二输入输出接脚、该第三输入输出接脚任两接脚所接收到的信号的相位是否相反,借此判定该第一输入输出接脚、该第二输入输出接脚以及该第三输入输出接脚是否耦接线圈。

11.本发明的精神在于每一个输入输出接脚皆可以耦接谐振线圈与谐振电容,当谐振线圈与谐振电容耦接的脚位不同时,减少接脚数的射频识别整合集成电路会发出不同的射频识别码。因此,生产射频识别整合集成电路仅需要一个生产线,事后可以利用外部电路改变所产生的射频识别码。在进一步的实施例中,还可以配合其他接脚上耦接的电压,产生更多不同的识别码。

12.为让本发明的上述和其他目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附图式,作详细说明如下。

附图说明

13.图1a绘示为本发明一较佳实施例的射频识别电路的供电电路图。

14.图1b绘示为本发明一较佳实施例的射频识别电路的供电电路图。

15.图2a绘示为本发明一较佳实施例的射频识别电路的识别码设定示意图。

16.图2b绘示为本发明一较佳实施例的射频识别电路的识别码设定示意图。

17.图2c绘示为本发明一较佳实施例的射频识别电路的识别码设定示意图。

18.图3a绘示为本发明一较佳实施例的射频识别电路的供电电路图。

19.图3b绘示为本发明一较佳实施例的射频识别电路的供电电路图。

20.图3c绘示为本发明一较佳实施例的射频识别电路的供电电路图。

21.图4绘示为本发明一较佳实施例的射频识别电路的检测线圈耦接的接脚的示意图。

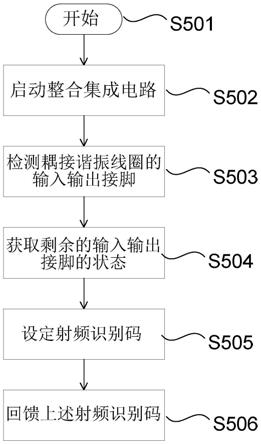

22.图5绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的流程图。

23.图6a绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的步骤s503的流程图。

24.图6b绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的步骤s503的流程图。

25.图6c绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的步骤s503的流程图。

26.图7绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的步骤s503的流程图。

27.【符号说明】

28.101:整合集成电路

29.102:谐振线圈

30.103:谐振电容

31.io1:第一输入输出接脚

32.io2:第二输入输出接脚

33.io3:第三输入输出接脚

34.d01、d02、d03:整流电路

35.vdd:第一电源接脚

36.vss:第二电源接脚

37.s501~s506:本发明实施例的减少接脚数的射频识别码提供方法的各步骤

38.s601~s609:本发明实施例的减少接脚数的射频识别码提供方法的步骤s503的子步骤

39.s701:本发明实施例的减少接脚数的射频识别码提供方法的步骤s503的子步骤

具体实施方式

40.图1a绘示为本发明一较佳实施例的射频识别电路的供电电路图。请参考图1a,此射频识别电路包括一整合集成电路101、一谐振线圈102以及一谐振电容103。此整合集成电路101在此实施例具有第一输入输出接脚io1、第二输入输出接脚io2以及一整流电路d01。图1b绘示为本发明一较佳实施例的射频识别电路的供电电路图。请参考图1b,同样地,此射频识别电路包括一整合集成电路101、一谐振线圈102以及一谐振电容103。此整合集成电路101在此实施例具有第一输入输出接脚io1、第二输入输出接脚io2以及一整流电路d01。图1a与图1b的差别在于,谐振线圈102以及谐振电容103的位置不同,此为所属领域技术人员可以理解的谐振技术,故在此不予赘述。

41.在此实施例中,谐振线圈102以及谐振电容103接收到射频能量时,会通过第一整流电路d01整流而将能量储存于第一电源接脚vdd与第二电源接脚vss之间的电容,以启动上述整合集成电路101。在此实施例中,虽然仅绘示第一输入输出接脚io1、第二输入输出接脚io2,然此仅为了说明射频识别电路的供电原理,实际上接脚数并不受限于此实施例,在此不予赘述。

42.图2a绘示为本发明一较佳实施例的射频识别电路的识别码设定示意图。图2b绘示为本发明一较佳实施例的射频识别电路的识别码设定示意图。图2c绘示为本发明一较佳实

施例的射频识别电路的识别码设定示意图。请同时参考图2a、图2b以及图2c,在此实施例中,整合集成电路101包括第一输入输出接脚io1、第二输入输出接脚io2以及第三输入输出接脚io3。图2a、图2b以及图2c的电路差异在于,谐振线圈102以及谐振电容103所耦接的脚位不同。在图2a中,谐振线圈102以及谐振电容103耦接第一输入输出接脚io1以及第二输入输出接脚io2。在图2b中,谐振线圈102以及谐振电容103耦接第二输入输出接脚io2以及第三输入输出接脚io3。在图2c中,谐振线圈102以及谐振电容103耦接第一输入输出接脚io1以及第三输入输出接脚io2。由于所有的输入输出接脚皆可以当作线圈的输入使用,所以本实施例以变化线圈所耦接输入输出接脚来改变整合集成电路101所输出的射频识别码。

43.图3a、图3b以及图3c绘示为本发明一较佳实施例的射频识别电路的供电电路图。请参考图3a、图3b以及图3c,图3a、图3b以及图3c的差异在于,谐振线圈102以及谐振电容103所耦接的脚位不同,因此,为了让整合集成电路101能顺利启动,任两个接脚皆有耦接整流电路d01、d02、d03。在图3a中,整流电路d01的第一输入端耦接第一输入输出接脚io1,整流电路d01的第二输入端耦接第二输入输出接脚io2。在图3b中,整流电路d02的第一输入端耦接第二输入输出接脚io2,整流电路d02的第二输入端耦接第三输入输出接脚io3。在图3c中,整流电路d03的第一输入端耦接第三输入输出接脚io3,整流电路d03的第二输入端耦接第一输入输出接脚io1。上述整流电路d01、d02、d03的第一输出接脚与第二输出接脚分别耦接第一电源接脚vdd与第二电源接脚vss。

44.在上述图2a、图2b以及图2c的实施例中,整合集成电路101必须要判断谐振线圈所耦接的输入输出接脚(io1、io2、io3)。为了使本领域技术人员可以通过本实施例内容来实施本发明,以下举例说明几种检测方法。第一种方法,利用线圈具有导电的特性,当2个输入输出接脚(io1、io2、io3)通过线圈接在一起时,一个输入输出接脚(io1、io2、io3)如果是浮动电压(floating)且另一个输入输出接脚(io1、io2、io3)有高低电压切换变化的话,则浮动电压的输入输出接脚(io1、io2、io3)会受到另一个输入输出接脚(io1、io2、io3)的影响。因此,当整合集成电路101被启动时(power on),先让第一输入输出接脚io1切换电压,检测其余的输入输出接脚io2、io3是否有随着电压变化,如无变化,再让第二输入输出接脚io1切换电压,检测输入输出接脚io1、io3,之后让第三输入输出接脚io3切换电压,检测输入输出接脚io1、io2,借此,整合集成电路101便可以检测出有接上线圈的输入输出接脚(io1、io2、io3)。

45.第二种方法可以例如在整合集成电路101的处理速度足够快的情况下使用。请参考图4,图4绘示为本发明一较佳实施例的射频识别电路的检测线圈所耦接的接脚的示意图。如图4所示,在此实施例中,假设线圈耦接在第一输入输出接脚io1以及第二输入输出接脚io2。由于在输入输出接脚io1、io2上的谐振波形是反相的,所以如果整合集成电路101的处理速度够快的话,可以直接检测任两个输入输出接脚(io1、io2、io3)的相位,如果一直相反则可判断为有耦接线圈的输入输出接脚(io1、io2、io3)。

46.上述实施例中,虽然是以三个输入输出接脚(io1、io2、io3)做举例,然所属领域技术人员,参考上述实施例后,应当可以理解,4个接脚以上(包含)仍可以实现本发明的技术,故本发明不限制三个输入输出接脚。另外,在图2a、图2b以及图2c,未使用的接脚虽然绘图上是以vdd或vss作为举例,也就是说,在上述例子中,三个输入输出接脚(io1、io2、io3)可以表示6个射频识别码,然而,在实际电路上,未使用的输入输出接脚除了耦接vdd或vss外,

还可以浮接(floating),故在另一较佳实施例中,上述三个输入输出接脚(io1、io2、io3)的例子实际上可以有9个射频识别码。若输入输出接脚数扩展成4个,若另外两个输入输出接脚只有耦接vdd或vss的情况下,将会有「io1;io2」、「io1;io3」、「io1;io4」、「io2;io3」、「io2;io4」、「io3;io4」6种排列组合配上其余的io可以做4个射频识别码的组合,故共有24个射频识别码。若未使用的输入输出接脚除了耦接vdd或vss外,还包含浮接(floating),此种情况,此电路就可以表示54个射频识别码。

47.图5绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的流程图。请参考图5,此减少接脚数的射频识别码提供方法包括下列步骤:

48.步骤s501:开始。

49.步骤s502:启动整合集成电路。

50.步骤s503:检测耦接谐振线圈的输入输出接脚。

51.步骤s504:获取剩余的输入输出接脚的状态。以图2为例,当第二与第三输入输出接脚io2、io3被检测到耦接至谐振线圈时,第一输入输出接脚io1将被作为剩余接脚。由于所输出的识别码是由谐振线圈与输入输出接脚的耦接关系与剩余接脚的电压状态所决定,故当剩余接脚的电压状态被决定后,所输出的识别码便可以被决定。

52.步骤s505:依照上述输入输出接脚状态以及耦接谐振线圈的输入输出接脚,设定射频识别码。

53.步骤s506:回馈上述射频识别码。

54.图6a绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的步骤s503的流程图。请参考图6a,检测耦接谐振线圈的输入输出接脚的步骤包括:

55.步骤s601:将第一输入输出接脚、第二输入输出接脚设定为浮动。

56.步骤s602:在第三输入输出接脚输出一指定电压。第三输入输出接脚例如是输出逻辑高电压或逻辑低电压或者交互输出逻辑高电压以及逻辑低电压。

57.步骤s603:判断第一输入输出接脚、第二输入输出接脚的任一接脚是否随着该指定电压变动。

58.图6b绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的步骤s503的流程图。请参考图6b,检测耦接谐振线圈的输入输出接脚的步骤包括:

59.步骤s604:将第二输入输出接脚、第三输入输出接脚设定为浮动。

60.步骤s605:在第一输入输出接脚输出指定电压。第一输入输出接脚例如是输出逻辑高电压或逻辑低电压或者交互输出逻辑高电压以及逻辑低电压。

61.步骤s606:判断第二输入输出接脚、第三输入输出接脚的任一接脚是否随着该指定电压变动。

62.图6c绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的步骤s503的流程图。请参考图6c,检测耦接谐振线圈的输入输出接脚的步骤包括:

63.步骤s607:将第一输入输出接脚、第三输入输出接脚设定为浮动。

64.步骤s608:在第二输入输出接脚输出指定电压。第二输入输出接脚例如是输出逻辑高电压或逻辑低电压或者交互输出逻辑高电压以及逻辑低电压。

65.步骤s609:判断第一输入输出接脚、第三输入输出接脚的任一接脚是否随着该指定电压变动。

66.如上所述,通过上述步骤s601~步骤s609,便可以判断出哪两个输入输出接脚耦接谐振线圈。

67.图7绘示为本发明一较佳实施例的减少接脚数的射频识别码提供方法的步骤s503的流程图。请参考图7与图4,检测耦接谐振线圈的输入输出接脚的步骤包括:

68.步骤s701:判断第一输入输出接脚、第二输入输出接脚、第三输入输出接脚任两接脚所接收到的信号的相位是否相反。借此,整合集成电路可判定第一输入输出接脚、第二输入输出接脚以及第三输入输出接脚是否耦接线圈。

69.综上所述,本发明的精神在于每一个输入输出接脚皆可以耦接谐振线圈与谐振电容,当谐振线圈与谐振电容耦接的脚位不同时,减少接脚数的射频识别整合集成电路会发出不同的射频识别码。因此,生产射频识别整合集成电路仅需要一个生产线,事后可以利用外部电路改变所产生的射频识别码。在进一步的实施例中,还可以配合其他接脚上耦接的电压,产生更多不同的识别码。

70.在较佳实施例的详细说明中所提出的具体实施例仅用以方便说明本发明的技术内容,而非将本发明狭义地限制于上述实施例,在不超出本发明的精神及以下申请专利范围的情况,所做的种种变化实施,皆属于本发明的范围。因此本发明的保护范围当视权利要求保护范围所界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1