冲刷涉及持久性存储器的高速缓存行的制作方法

1.本公开总体上涉及集成电路上的冲刷操作。更具体地,本公开涉及在一个或多个电路管芯上的冲刷操作期间处理持久性存储器。

背景技术:

2.本节旨在向读者介绍可能与本公开的各个方面相关的技术的各个方面,这些方面在下面进行了描述和/或要求保护。该讨论被认为有助于为读者提供背景信息以促进更好地理解本公开的各个方面。因此,可以理解的是,这些陈述将在此情况下阅读,而不是作为对现有技术的承认。

3.外围组件互连快速(pcie)链路可以用于将设备(例如,现场可编程门阵列(fpga))连接到中央处理单元。设备可以从中央处理单元接收指令,并且可以根据指令采取动作以执行一项或多项任务。设备还可以连接到一个或多个存储器,但是由于pcie链接的限制,该一个或多个存储器可能是设备专用的(例如,中央处理单元不容易访问)。因此,中央处理单元和一个或多个存储器的设备或存储器控制器可能需要执行直接介质访问(dma)操作,以彼此通信并与一个或多个存储器通信(例如,以执行对一个或多个存储器的存储器读取或存储器写入)。这种dma在电力和时间上都是昂贵的。

4.为了克服外围组件互连快速(pcie)链路的存储器相关限制,可以使用通信链路(例如,一致性链接)来增加计算机处理单元(cpu)可访问且由操作系统管理的存储器或存储设备(storage)的量。事实上,当使用一致性链路将设备连接到中央处理单元时,设备和中央处理单元可以参与彼此的存储器池(在不进行直接介质访问(dma)操作的情况下)。也就是说,经由一致性链路与中央处理单元耦合或由其管理的存储器和由设备耦合或由其管理的存储器可以是标准存储器并且在逻辑上是相似的。这种应用被称为存储器扩展。

5.可以耦合到中央处理单元的一种类型的存储器是持久性存储器。持久性存储器存储即使在断电时也能被维持的数据。也就是说,在断电事件期间或之后,保存在持久性存储器中的数据被保留。可以耦合到中央处理单元的另一种类型的存储器是易失性存储器。易失性存储器存储在易失性存储器断电时丢失的数据。类似类型的存储器可以耦合到设备。一致性链路允许耦合到中央处理单元和设备中的任一个的持久性存储器和易失性存储器二者用作操作系统的标准存储器。冲刷指令可以将指向持久性存储器的高速缓存行和指向易失性存储器的高速缓存行从中央处理单元移动到其目的地存储器(例如,耦合到设备的持久性存储器和耦合到设备的易失性存储器)。然而,在存储器层级中可能不存在持久性存储器高速缓存行或易失性存储器高速缓存行之间的标记或区别。

附图说明

6.通过阅读以下详细描述和参考附图,可以更好地理解本公开的各个方面,在附图中:

7.图1是根据本公开的实施例的包括中央处理单元、设备和一致性链路的集成电路

系统的框图,其中,设备耦合到持久性存储器和易失性存储器;

8.图2是根据本公开的实施例的可能导致电力损耗流的组件的框图;

9.图3是根据本公开的实施例的具有用于单通道存储器控制器的高速缓存行的数据路径流的组件的框图;

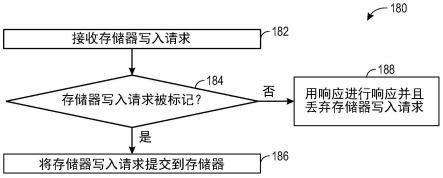

10.图4是示出根据本公开的实施例的用于标记指向持久性存储器并存储存储器写入请求的高速缓存行的过程的流程图;以及

11.图5是示出根据本公开的实施例的用于确定是提交还是优雅地丢弃存储存储器写入请求的高速缓存行的过程的流程图。

具体实施方式

12.下面将描述一个或多个具体实施例。为了提供这些实施例的简明描述,在说明书中并未描述实际实现方式的所有特征。应该理解,在任何此类实际实现方式的开发中,就像在任何工程或设计项目中一样,必须做出许多特定于实现方式的决策来实现开发人员的特定目标,例如遵守与系统相关和与业务相关的约束,这可能因实现方式而异。此外,应当理解,这样的开发工作可能是复杂和耗时的,但是对于受益于本公开的普通技术人员而言,它仍然是设计、制造和生产的例行工作。

13.在介绍本公开的各种实施例的元素时,冠词“一(a)”、“一个(an)”和“该(the)”旨在表示存在一个或多个元素。术语“包括”、“包含”和“具有”旨在是包括性的,并且表示除了所列元素之外可能还有附加元素。此外,应当理解,对本公开的“一个实施例”或“实施例”的引用并不旨在被解释为排除也包含所记载的特征的附加实施例的存在。

14.集成电路系统可以包括中央处理单元和经由一致性链路连接到中央处理单元的设备。该设备可以支持或耦合到持久性存储器和易失性存储器。由于中央处理单元和设备被一致性连接,因此耦合到设备的存储器可以参与中央处理单元的存储器池。因此,耦合到中央处理单元的存储器和耦合到设备的存储器在逻辑上可以是相似的并且用作标准存储器。在不同的时间,集成电路系统可能接收到电源故障信号。在电源故障事件期间和之后,集成电路系统维持一定的存储器是有益的。事实上,只有某些类型的存储器可以在断电后维持数据。

15.中央处理单元和设备可以耦合到各种类型的存储器,包括易失性存储器和持久性存储器。易失性存储器存储在易失性存储器断电时丢失的数据。因此,在断电事件之后,存储在易失性存储器中的数据是不可恢复的,因为易失性存储器需要一定量的电力来维持其状态。

16.持久性存储器存储的数据即使在断电时也被维持。也就是说,在断电事件期间或之后,存储在持久性存储器中的数据被保留。在断电事件期间,冲刷(flush)并确保指向持久性存储器的高速缓存行到达持久性存储器是有益的,因为存储在高速缓存行中的数据在其进入持久性存储器之前不是持久性的。

17.本实施例总体上涉及用于将高速缓存行冲刷到持久性存储器的系统和方法。本文提供的系统和方法包括标记高速缓存行以提供指向持久性存储器的高速缓存行和指向易失性存储器的高速缓存行之间的区别。例如,这些高速缓存行可以被标记为在集成电路系统的存储器层级中指向持久性存储器和/或指向易失性存储器。还可以标记指向存储设备

的高速缓存行。本文公开的系统和方法在集成电路系统上的断电事件期间可能特别有用。例如,响应于集成电路系统接收到正在发生断电事件的指示,指向易失性存储器的高速缓存行可以被优雅地完成(例如,用响应进行响应以及丢弃),而指向持久性存储器的高速缓存行可以被提交到持久性存储器目的地。本文公开的系统和方法的优点包括优化以下项目:存储器控制器处理延迟,读取处理延迟,易失性写入处理延迟和持久性写入处理延迟,等等。实际上,使用本技术,存储器控制器处理延迟、读取处理延迟、易失性写入处理延迟和持久性写入处理延迟被优化,因为集成电路系统可以处理和完全冲刷:仅被标记的高速缓存行,或仅未标记的高速缓存行,这可能是在断电事件期间特别有用。

18.图1是根据本公开的实施例的集成电路系统10的框图。集成电路系统10包括中央处理单元12、设备14、将设备14附接到中央处理单元12的通信链路(例如,在所示实施例中,一致性链路16)和备用电池40。中央处理单元12可以是任何合适的中央处理单元,例如处理器。设备14可以是任何合适的设备,例如现场可编程门阵列(fpga)设备或专用集成电路(asic)设备。中央处理单元12和设备14经由一致性链路16(例如,一致性附接致动器或一致性连接设备)彼此耦合。例如,一致性链路16可以是任何合适的一致性链路,例如ultra path interconnect(upi)或computer express link(cxl)。集成电路系统10还包括耦合到中央处理单元12的存储器18和存储设备20以及耦合到设备14的存储器22和存储设备24。

19.具体地,在所示实施例中,中央处理单元12耦合到易失性存储器26(例如,双倍数据速率4(ddr4)、双倍数据速率5(ddr5)、低功率双倍数据速率4(lpddr4)中的一个或多个)、持久性存储器28(例如,optane

tm

持久性存储器、optane

tm

固态设备(ssd)、optane

tm

双列直插存储器模块(dimm))和存储设备20。易失性存储器26、持久性存储器28和存储设备20由集成电路系统10的操作系统管理。设备14耦合到易失性存储器30、持久性存储器32和存储设备24,它们也由集成电路系统10的操作系统管理。一致性链路16允许设备14用作中央处理单元12的易失性存储器30和持久性存储器32的存储器控制器。一致性链路16还允许易失性存储器30和持久性存储器32用作标准操作系统存储器,中央处理单元12可以在不使用直接介质访问(dma)的情况下访问该标准操作系统存储器。耦合到设备14的存储设备24也是标准操作系统存储设备,并且因此可由中央处理单元12访问而不使用直接介质访问(dma)。易失性存储器26、持久性存储器28和存储设备20在逻辑上可以类似于易失性存储器30、持久性存储器32和存储设备24,它们均用作标准操作系统存储器或存储设备。这样,在中央处理单元12和设备14之间的直接介质访问(dma)操作对于中央处理单元12向持久性存储器32、易失性存储器30或存储设备24写入或从其读取可能不是必需的。

20.数据可以以被称为高速缓存行的数量(例如,64字节)在集成电路系统10周围移动。高速缓存行还可以携带诸如读取或写入请求之类的请求,该请求用于从存储器或存储设备读取或向其写入。来自中央处理单元12的高速缓存行可以通过一致性链路16提供给设备14。一致性链路16可以被配置为执行包括解码和将高速缓存行指向特定存储器通道的操作。设备14包括易失性存储器数据路径34、持久性存储器数据路径36和存储设备数据路径38。这些数据路径用于处理指向相应数据路径的高速缓存行。即,涉及易失性存储器30的高速缓存行可以被发送到易失性存储器数据路径34,涉及持久性存储器32的高速缓存行可以被发送到持久性存储器数据路径36,并且涉及存储设备24的高速缓存行可以被放置在存储

设备数据路径38上。在一些实施例中,设备14中仅有的数据路径是持久性存储器数据路径36。此外,在一些实施例中,设备14、存储器22和存储设备24可以位于外围组件互连快速(pcie)卡或在集成电路系统10的主板上。

21.集成电路系统10被配置为识别指向持久性存储器的高速缓存行,并标记元数据以区分在存储器层级中指向持久性存储器的高速缓存行和指向易失性存储器的高速缓存行。例如,中央处理单元12的逻辑电路可以被配置为:用指示指向持久性存储器28的高速缓存行的元数据来标识和标记高速缓存行所指向的持久性存储器(persistent memory directed cache lines),并且设备14的或在设备14上的逻辑电路或软逻辑可以被配置为:用指示指向持久性存储器32的高速缓存行的元数据来标识和标记高速缓存行所指向的持久性存储器。在一些情况下,集成电路系统10可以确定与高速缓存行的目的地地址相关联的存储器或存储设备类型。存储器或存储设备类型可以是持久性(例如,持久性存储器、存储设备)或非持久性(例如,易失性存储器),并且高速缓存行的标记可以包括:以指示与目的地地址相关联的存储器或存储设备类型的方式用元数据标记高速缓存行。

22.虽然本文讨论的系统和技术具体参考一致性链路(例如,一致性链路16),但应当注意,实施例不限于一致性链路。实际上,本文讨论的系统和技术可能涉及集成电路设备,该集成电路设备涉及非一致性链路(例如,标准外围组件互连快速(pcie))而不是一致性链路16。因此,在一些实施例中,集成电路设备可以替代地包括将设备14耦合到中央处理单元12的非一致性链路。

23.当集成电路系统10操作时,中央处理单元12可以执行涉及持久性存储器、易失性存储器和/或存储设备的操作。因此,高速缓存行可以从中央处理单元12移动到期望的持久性存储器目的地、期望的易失性存储器目的地和/或期望的存储设备目的地。中央处理单元12可以将高速缓存行冲刷到存储器或存储设备目的地。例如,当中央处理单元12接收到电源故障信号时,中央处理单元12可以将高速缓存行冲刷到电源故障保护域以保护数据。冲刷可以涉及:将涉及诸如写入请求之类的请求的高速缓存行移动到写入请求的特定目的地。例如,由中央处理单元12发起并存储对持久性存储器28的写入请求的高速缓存行可以被冲刷到持久性存储器28,其是高速缓存行的最终目的地。高速缓存行可以从中央处理单元12冲刷到易失性存储器26、持久性存储器28或存储设备20。高速缓存行也可以从中央处理单元12冲刷到易失性存储器30、持久性存储器32或存储设备24。将高速缓存行冲刷到易失性存储器30、持久性存储器32或存储设备24花费有限的时间量。目的地为易失性存储器30、持久性存储器32或存储设备24的高速缓存行是未决的(pending)(例如,未提交到目的地),直到它们到达易失性存储器30、持久性存储器32或存储设备24。例如,指向持久性存储器32的高速缓存行在高速缓存行仍处于一致性链路16、中央处理单元12的存储器层级中或在设备14中时是未决的。实际上,高速缓存行未被提交到存储器,直到高速缓存行到达特定存储器或存储设备目的地。注意到这一点很重要,因为如果集成电路系统10没有足够的电力将高速缓存行提交到其存储器目的地,则未决的高速缓存行可能会被丢弃。

24.冲刷操作可以包括将高速缓存行传输到存储器目的地。例如,源自中央处理单元12的高速缓存行可以被引导到耦合到设备14的持久性存储器32。这样,高速缓存行将从中央处理单元12通过一致性链路16传输到设备14,并最终到持久性存储器32。在一些情况下,为了响应于接收到电源故障信号而加速完成冲刷操作,集成电路系统10可以仅将指向持久

性存储器28或持久性存储器32的被标记的高速缓存行提交到存储器。在这些情况下,选择性地仅将指向持久性存储器28或持久性存储器32的高速缓存行提交到存储器(如标记所指示),同时避免将指向易失性存储器26或易失性存储器30的高速缓存行提交到存储器目的地,可以加快冲刷操作的完成。实际上,这种基于标记的选择性提交可以用于:加速冲刷操作,并减少维持集成电路系统10所需的电量(在集成电路系统10检测到电源故障之后)。这样,冲刷所有高速缓存行的总时间可以减少到冲刷包含指向持久性存储器28的高速缓存行和指向持久性存储器32的高速缓存行的队列的总时间。

25.在某一时间,集成电路系统10上可能会发生电源故障。也就是说,集成电路系统10的供电装置可能无法经由例如交流(a/c)电源为集成电路系统10提供足够的电力以继续操作。当发生电源故障时,集成电路系统10可能容易丢失存储在未决高速缓存行中的信息(这些高速缓存行是尚未被提交到存储器或存储设备目的地的高速缓存行)和/或存储在易失性存储器26和易失性存储器30中的信息。如上所述,持久性存储器28、持久性存储器32、存储设备20和存储设备24可能不容易丢失提交到持久性存储器或存储设备的高速缓存行数据,因为持久性存储器和存储设备在断电时被保持。这样,在没有将指向持久性存储器的高速缓存行冲刷和提交到持久性存储器的情况下,集成电路系统10可能丢失在指向持久性存储器的高速缓存行中的信息。此外,冲刷高速缓存行可能会消耗有限的时间量来完成。因此,当集成电路系统10检测到电源故障时,期望具有辅助电源或可以向集成电路系统10提供电力的电源,使得其高速缓存行(尤其是其指向持久性存储器目的地的高速缓存行)分配足够时间以完全冲刷到持久性存储器。

26.牢记这一点,为了减轻电源故障的影响,集成电路系统10包括备用电池40。备用电池40被配置为响应于检测到集成电路系统10的供电装置的电源故障,而为集成电路系统10或集成电路系统10的特定组件供电。备用电池40可以在有限的时间量(例如,100微秒、10毫秒)内向集成电路系统10的组件提供电力。例如,这种电力可以用于将高速缓存行(例如,存储器写入请求)从中央处理单元12冲刷到易失性存储器30、持久性存储器32或存储设备24。在本实施例中,备用电池40被配置为提供足够的电力以将未决的持久性存储器高速缓存行提交到持久性存储器。在一些实施例中,备用电池40可以被配置为提供足够的电力以将未决的持久性存储器高速缓存行提交到持久性存储器,并将未决的存储设备高速缓存行提交到存储设备。例如,维持电力的持续时间可以基于需要被冲刷到持久性存储器或存储设备的高速缓存行的数量来确定。可以针对冲刷持久性存储器高速缓存行来优化备用电池40,而不考虑冲刷易失性存储器高速缓存行。事实上,易失性存储器高速缓存行可能不需要被冲刷到系统存储器,因为易失性存储器在其无法接收电力之后失去其状态。

27.当断电事件发生时,仍然未决的(例如,不在持久性存储器28或持久性存储器32、存储设备20或存储设备24、或易失性存储器26或易失性存储器30中)高速缓存行可能无法到达它们的存储器目的地。例如,即使可能打算将高速缓存行提交到持久性存储器28或持久性存储器32,但该高速缓存行不是持久的,直到该高速缓存行被提交到持久性存储器28或持久性存储器32。这样,当高速缓存行被指向持久性存储器但仍然未决(例如,不在持久性存储器中)并且发生电源故障时,高速缓存行将不会被维持,而是将丢失或被丢弃。如果在丢弃指向持久性存储器28或持久性存储器32的高速缓存行之后恢复集成电路系统10的电力,则中央处理单元12可能无法从持久性存储器28或持久性存储器32读取该高速缓存

行,因为该高速缓存行在其进入持久性存储器28或持久性存储器32之前被丢弃了。同样,涉及持久性存储器28或持久性存储器32、存储设备20或存储设备24、或易失性存储器26或者易失性存储器30的高速缓存行不被认为将被冲刷,直到高速缓存行已经到达持久性存储器28或持久性存储器32、存储设备20或存储设备24、或易失性存储器26或易失性存储器30。

28.来自备用电池40的电力可以被集成电路系统10用来在电源故障的情况下将高速缓存行冲刷到它们相应的存储器或存储设备目的地。响应于接收到电源故障的指示,集成电路系统10可以被配置为优先冲刷某些高速缓存行。例如,集成电路系统10可以被配置为仅处理指向持久性存储器28或持久性存储器32的高速缓存行。如上所述,元数据标记可以指示指向持久性存储器28或持久性存储器32的高速缓存行。由于经由元数据标记将指向持久性存储器28或持久性存储器32的高速缓存行与指向其它存储器的高速缓存行区分开来,因此集成电路系统10可以识别和处理指向持久性存储器目的地的高速缓存行,并优雅地完成(例如,用响应(例如,默认响应)进行响应并丢弃)、丢弃不指向持久性存储器目的地(例如,持久性存储器28或持久性存储器32)的高速缓存行,如元数据标记所指示的。优雅完成操作可以包括用默认响应(例如,一个或多个零)来响应高速缓存行。因此,由于需要提交到存储器目的地的高速缓存行的数量减少,所以备用电池40可以具有减少的电力维持要求。例如,在集成电路系统10的供电装置(例如,交流(a/c)供电装置)发生电源故障之后,备用电池40可能只需要具有足够的电力来将高速缓存行提交到持久性存储器目的地10。将指向持久性存储器28或持久性存储器32的高速缓存行提交到存储器,并优雅地完成(例如,用响应进行响应以及丢弃)指向易失性存储器26或易失性存储器30的高速缓存行可能是有用的,因为当集成电路系统10关闭时,直接到易失性存储器26或易失性存储器30的高速缓存行将丢失。这是因为存储在易失性存储器26和易失性存储器30中的数据在易失性存储器26和易失性存储器30断电时丢失。易失性存储器26和易失性存储器30需要电力来维持存储在相应易失性存储器26或易失性存储器30中的任何信息。在一些情况下,将指向存储设备20或存储设备24的高速缓存行提交到存储设备也是有用的,同时避免提交其它高速缓存行。实际上,在一些实施例中,可以选择性地确保将指向持久性存储器28、持久性存储器32、存储设备20和/或存储设备24的高速缓存行(如基于高速缓存行的元数据标记所指示的)提交到持久性存储器和存储设备目的地,以将这些高速缓存行的处理与易失性存储器高速缓存行区别开来。在这样的实施例中,可以通过确保备用电池40具有足够的电力用于在电源故障之后将区分开的高速缓存行提交到持久性存储器目的地或存储设备目的地来确保这些区分开的高速缓存行的提交。

29.例如,在特定时间,一百个高速缓存行可能等待到达由设备14管理的存储器目的地。在一百个高速缓存行中,九十个高速缓存行可能去往易失性存储器30,而十个高速缓存行可能指向持久性存储器32。当集成电路系统10检测到电源故障时,集成电路系统10可以处理和提交指向持久性存储器32的十个高速缓存行,并且优雅地完成(例如,用响应进行响应以及丢弃)指向易失性存储器26的九十个高速缓存行。这样,使用本实施例,在处理和提交所有一百个高速缓存行所用的时间量的1/10内,备用电池40可以足以为集成电路系统10提供电力。冲刷指向持久性存储器的高速缓存行的时间量减少(其部分通过避免将易失性存储器高速缓存行提交到易失性存储器而引起)允许减小电池尺寸。因此,可以减少备用电池40,从而引起降低电池成本和电池尺寸。实际上,与冲刷一百个高速缓存行所需的电力相

反,在当前示例中,备用电池40仅需要为指向持久性存储器32的十个高速缓存行提供足够的电力。因此,由于在电源故障之后保持集成电路系统10存活(alive)所需的时间量减少了,所以备用电池40可以存储减少量的能量。

30.在一些实施例中,备用电池40是基于持久性存储器高速缓存行队列的深度来设计的。例如,备用电池40可以被设计为:在基于处理和提交持久性存储器高速缓存行队列的最后输出的持久性存储器高速缓存行(last out persistent memory cache line)的时间量计算出的时间段内,为集成电路系统10供电。实际上,可以对备用电池40进行定时以支持指向持久性存储器的高速缓存行,而不考虑指向易失性存储器目的地的高速缓存行。因此,在一些实施例中,当确定备用电池40的大小时,持久性存储器高速缓存行队列被考虑为因素而不是易失性存储器高速缓存行队列。在一些实施例中,可以基于持久性存储器高速缓存行队列的深度和存储设备高速缓存行队列的深度来设计备用电池40。

31.在一些实施例中,集成电路系统10可以选择性地在某些高速缓存行路径上提供备用电力,以减少与备用电池40相关联的备用电力的量和成本。具体地,设备14可以包括多个电源。多个电源中的每一个都可以为特定的存储器控制器供电。当发生电源故障时,备用电池40可以选择性地仅对持久性存储器32的存储器控制器供电。因此,为易失性存储器30供电的电源在没有备用电力的情况下发生故障。作为另一示例,备用电池40可以选择性地仅对持久性存储器数据路径36供电,而存储设备数据路径38和易失性存储器数据路径34不响应于电源故障而从电源接收备用电力。在不同的实施例中,可以存在其间的电池备用电力的其它组合。例如,备用电池40可以被配置为:为持久性存储器数据路径36和存储设备数据路径38供电,而易失性存储器数据路径34保持没有电力。

32.图2是根据本公开的示例性实施例的涉及集成电路系统10并响应于检测到电源故障而发生的流程的框图60。在所示实施例中,集成电路系统10的中央处理单元12包括平台控制器单元(pcu 62)、核心处理器(core 64)、存储器控制器(mc)66和存储设备控制器(sc)68。存储器控制器66代表两个存储器控制器——一个用于易失性存储器26,并且一个用于持久性存储器28。存储设备控制器68管理存储设备20。

33.在所示实施例中,设备14包括一致性链路逻辑70(例如,软ultra path interconnect(upi)逻辑),一致性链路逻辑70包括用于解码一致性链路请求的解码器72(例如,一致性链路解码器)和写未决队列(“wpq”)74。写未决队列74代表多个写未决队列——一个用于易失性存储器30,一个用于持久性存储器32,并且一个用于存储设备24。设备14还包括:用于管理存储设备24的存储设备控制器76,以及存储器控制器78。存储器控制器78代表两个存储器控制器——一个用于易失性存储器30,并且一个用于持久性存储器32。存储器控制器78可以包括非暂时的、有形的且计算机可读的介质,该介质包括可由存储器控制器78的处理器执行的指令。指令可以包括用于管理以下各项的指令:耦合到存储器控制器78的存储器,以及被配置为访问耦合到存储器控制器78的存储器的请求。存储设备控制器76和存储器控制器78可以被配置为存储未决操作(例如,读取请求、写入请求)。

34.在所示实施例中,供电装置80(例如,交流a/c供电装置)为集成电路系统10供电。在一些实施例中,当供电装置80为集成电路系统10供电时,集成电路系统10可以处理读取请求和写入请求二者,而不管在指向存储设备或存储器目的地的高速缓存行上是否检测到标记。在某个时间点,可以由集成电路系统10检测电源故障。响应于检测到电源故障,可以

断言(例如,由供电装置80)指示电源故障的信号以将检测到的电源故障通知平台逻辑82(例如,平台逻辑电路)。该信号还可以使平台逻辑82开始断电操作。命令启动定时器84(例如,平台控制中心adr定时器(platform control hub adr timer)),该定时器84跟踪在电源故障后可以对集成电路系统10供电多久,并且将信号发送到中央处理单元12和设备14两者以通知电源故障。响应于接收到该信号(例如,指示电源故障的数据分组),中央处理单元12可以准备发出其存储器层级的冲刷。具体地,中央处理单元12可以基于高速缓存行的元数据标记来选择性地将高速缓存行冲刷和提交到持久性存储器28和/或存储设备20,同时避免将指向易失性存储器26的高速缓存行提交到易失性存储器26。指向易失性存储器26的高速缓存行可以被优雅地完成(例如,用响应进行响应以及丢弃)。类似地,基于高速缓存行的元数据标记,设备14可以选择性地从提交指向持久性存储器32、易失性存储器30和存储设备24的高速缓存行改变为仅冲刷和提交指向持久性存储器32或存储设备24的高速缓存行,同时避免将指向易失性存储器30的高速缓存行提交到易失性存储器30。指向易失性存储器30的高速缓存行可以被优雅地处理(例如,用响应进行响应以及丢弃)。备用电池40可以在定时器所指定的时间段期间为集成电路系统10供电。可以基于用于将高速缓存行冲刷到持久性存储器28、持久性存储器32、存储设备20和/或存储设备24的最坏情况场景来识别或确定备用电池40和定时器84定时。例如,最坏情况场景可以包括或至少部分地基于中央处理单元12中的且目的地是持久性存储器28的一个或多个高速缓存行被冲刷到持久性存储器28所花费的时间。备用电池的大小可以基于与要提交到持久性存储器28的高速缓存行的数量相对应的队列长度、而不基于与要提交到易失性存储器30的高速缓存行的数量相对应的队列长度来确定。

35.如前所述,未决高速缓存行可以位于沿集成电路系统10的各个位置。例如,指向持久性存储器28、易失性存储器26和存储设备20中的任一个的高速缓存行可以位于中央处理单元12的存储器层级中,并且指向持久性存储器32、易失性存储器30和存储设备24中的任一个的高速缓存行可以位于中央处理单元12的存储器层级、一致性链路16或设备14中。在任一情况下,在响应于检测到电源故障而执行的操作期间,集成电路系统10可以自身从处理和提交指向每个存储器和存储设备目的地的未决高速缓存行改变为将指向持久性存储器或存储设备的相应高速缓存行识别并提交到持久性存储器或存储设备,并优雅地完成(例如,用响应进行响应以及丢弃)指向易失性存储器的高速缓存行。

36.图3是根据本公开的实施例从一致性链路16进入设备14并涉及单通道存储器控制器的存储器目的地(例如,来自中央处理单元12的存储器写入请求)的高速缓存行的数据路径流的框图。在一些实施例中,在集成电路系统10检测到电源故障时可以使用图3中所示的数据路径流。在所示实施例中,设备14包括第一管芯100和第二管芯102。在第一管芯100处,经由一致性链路16从中央处理单元12进入设备14的高速缓存行被记录到适当的队列中。高速缓存行还被配置为通过链路循环冗余校验(lcrc 104)。在所示的实施例中,可以基于高速缓存行的属性将高速缓存行记录到响应队列(resp fifo 106)、请求队列(req fifo 108)、写入批量队列(wb fifo 110)、非一致性旁路队列(ncb fifo 112)、非一致性标准队列(ncs fifo 114)或小睡队列(snooze queue)(snp fifo 116)。例如,涉及存储器写入请求的高速缓存行可以前进到写入批量队列(wb fifo 110)。在高速缓存行被记录在适当的队列中之后,高速缓存行前进到高级接口总线(aib 118),该总线将第一管芯100连接到第

二管芯102。然后高速缓存行前进到设备14的第二管芯102,其在所示实施例中包括一致性链路逻辑(cl logic 120)(例如,一致性链路软逻辑)。

37.在一致性链路软逻辑120内,解码器122识别指向持久性存储器的高速缓存行并用元数据标记它们。替代地,在一些实施例中,指向易失性存储器的高速缓存行可以用元数据标记。高速缓存行及其标记(如果适用)随后继续下行到适当的队列,包括一致性读取未决队列(rpq-c 124)、非一致性读取未决队列(rpq-nc 126)以及写入未决队列(wpq 128)。在设备14的第二管芯102中,确定高速缓存行是否指向持久性存储器129。如果设备14确定高速缓存行指向持久性存储器129,则设备14将用指示高速缓存行指向持久性存储器129的元数据标记高速缓存行。替代地,如果设备14确定高速缓存行指向易失性存储器,则设备14可以用指示高速缓存行指向易失性存储器130的元数据标记高速缓存行。然后高速缓存行继续下行到存储器控制器132,其可以将高速缓存行接收到相应的队列134中。没有被标记为指向持久性存储器129的高速缓存行将被优雅地完成(例如,用响应进行响应以及丢弃),因为这些高速缓存行可能指向易失性存储器130。在一些实施例中,没有被标记为指向持久性存储器129的高速缓存行在一致性链路软逻辑120中或在存储器控制器132处被丢弃。在一些实施例中,硬逻辑、或者一致性链路软逻辑和硬逻辑的组合可以执行类似于一致性链路软逻辑120的操作。

38.在一些实施例中,一致性链路逻辑120中的控制和状态寄存器(csr)可以由所支持的下游存储器、存储器范围和存储器类型组成。下面的表1中提供了配置和状态寄存器的每个存储控制器定义的示例。

[0039][0040]

在表1中,基于由存储器控制器控制的存储器的配置指示了各种类型的存储器。如果存储器控制器仅管理持久性存储器,则类型字段可以指示persistent,或者如果存储器控制器仅管理易失性存储器则指示volatile。both_vp和both_pv类型指示对持久性存储器和易失性存储器两者的支持/管理。由于在所示实施例中,存储器控制器132管理持久性存储器129和易失性存储器130,因此存储器控制器所指示的类型是both_pv或both_vp。在该讨论中,将假设类型为both_vp,这表示start_range至partition中的存储器地址为易失性存储器130的存储器地址,并且在partition至end_range中的存储器地址为持久性存储器129的存储器地址。

[0041]

下面的表2提供了根据实施例标记哪些指向存储器控制器的高速缓存行的示例。

[0042]

如果(请求地址)在类型标记start_range至end_rangepersistentset

start_range至end_rangevolatileclrstart_range至partitionboth_pvsetpartition至end_rangeboth_pvclrstart_range至partitionboth_vpclrpartition至end_rangeboth_vpset

[0043]

在表2中,基于高速缓存行中的存储器地址的位置和/或由存储器控制器132管理的存储器类型来标记不同类型的高速缓存行。如果请求地址在start_range至end_range中并且存储器控制器所支持的存储器类型仅为持久性存储器,则一致性链路逻辑120(例如,解码器122)将高速缓存行标记为指向持久性存储器。如果请求地址在start_range至end_range中并且存储器控制器所支持的存储器类型仅为易失性存储器,则一致性链路逻辑120不将高速缓存行标记为指向持久性存储器。由于存储器控制器管理持久性存储器和易失性存储器两者,并且由于类型是both_vp,这表明在start_range至partition中的存储器地址是易失性存储器的存储器地址,并且在partition至end_range中的存储器地址是持久性存储器的存储器地址,因此确定高速缓存行中的存储器地址的位置来确定高速缓存行是否将被标记。例如,如果请求地址在start_range至partition中,并且存储器控制器所管理的存储器类型是both_vp,那么一致性链路逻辑120不标记高速缓存行,因为所请求的存储器地址是易失性存储器。如果请求地址在partition至end_range中,并且存储器控制器所管理的存储器类型是both_vp,那么一致性链路逻辑120标记高速缓存行,因为所请求的存储器地址是持久性存储器。

[0044]

应当注意,关于图3描述的类似过程也可以存在于涉及存储设备目的地(例如,来自中央处理单元12的存储设备写入请求)时高速缓存行从一致性链路16进入设备14的数据路径流中。实际上,存储设备控制器(图3中未示出)可以管理存储设备136,并且解码器122可以确定高速缓存行存储请求是否要被标记并且是否要被提交到存储设备136。

[0045]

在一些实施例中,如图3所示,指向易失性存储器130或指向存储设备136的高速缓存行另外和/或替代地用元数据标记。例如,可以用元数据标记指向易失性存储器130的存储器高速缓存行,并且可以识别未标记的存储器高速缓存行(例如,指向持久性存储器的高速缓存行)并将其提交到持久性存储器目的地。

[0046]

图4是用于标记指向持久性存储器并且存储存储器写入请求的高速缓存行的过程160。在一些实施例中,过程160可以由设备14、中央处理单元12或解码器72来执行。

[0047]

过程160包括接收(框162)存储器写入请求。存储器写入请求可以源自中央处理单元12,并且可以指向由设备14管理的持久性存储器。替代地,存储器写入请求可以源自中央处理单元12,并且可以指向由中央处理单元12管理的持久性存储器。

[0048]

确定(框164)存储器写入请求是否以持久性存储器为目的地。例如,可以经由解码器(例如,解码器122或中央处理单元12的解码器)对存储器写入请求的范围地址进行解码,以确定存储器写入请求的目的地。

[0049]

如果存储器写入请求的目的地是持久性存储器,则过程160继续,以将存储器写入请求标记(框166)为指向持久性存储器目的地。存储器写入请求可以用元数据标记。例如,响应于对存储器写入请求的范围地址进行解码并经由解码器确定范围地址是持久性存储器,解码器可以将存储器写入请求标记为指向持久性存储器。

[0050]

返回到框164,如果存储器写入请求的目的地不是持久性存储器,则过程160继续,以不标记(框168)存储器写入请求为指向持久性存储器。应当注意,在一些实施例中,未标记为目的地为持久性存储器的写入请求仍然可以被标记——标记为指向适当的目的地(例如,易失性存储器或存储设备)。在这些实施例中,这些不以持久性存储器为目的地的写入请求的标记可以指示不同的目的地。过程160中表示的类似操作可由存储设备控制器执行。此外,可以在过程160的实施例中利用存储涉及存储器目的地的其它请求(例如,读取请求)的高速缓存行。

[0051]

过程160的其它实施例包括标记或区分指向存储设备的高速缓存行和/或指向易失性存储器的高速缓存行。例如,可以经由解码器对指向存储设备目的地的高速缓存行进行解码,以确定存储设备目的地的范围地址。基于确定指向存储设备目的地的高速缓存行的范围地址,可以对高速缓存行进行标记或不标记。类似地,可以经由解码器对指向易失性存储器的高速缓存行进行解码以确定高速缓存行的存储器目的地的范围地址。基于确定高速缓存行的范围地址指向易失性存储器目的地,高速缓存行可以被标记,从而提供在持久性存储器高速缓存行和易失性存储器高速缓存行之间的区别特征。

[0052]

图5是根据本公开的实施例的用于确定是提交还是优雅地丢弃(例如,用响应进行响应以及丢弃)存储存储器写入请求的高速缓存行的过程180。在一些实施例中,过程180可以由中央处理单元12的存储器控制器或设备14的存储器控制器执行。

[0053]

在框182处,存储器控制器接收存储器写入请求。存储器写入请求可以涉及要写入到由存储器控制器管理的存储器的数据。

[0054]

存储器控制器继续以确定(框184)存储器写入请求是否被标记。例如,存储器写入请求可以用元数据标记,该元数据可以用来确定存储器写入请求的目的地——无论其是对持久性存储器还是对易失性存储器的存储器写入请求。元数据可以指示存储器写入请求指向持久性存储器。

[0055]

响应于存储器写入请求被标记,存储器控制器可以将存储器写入请求提交(框186)到存储器。例如,可以响应于存储器写入请求被标记为指向持久性存储器而将存储器写入请求提交到持久性存储器。

[0056]

返回到框184,如果存储器控制器确定存储器写入请求没有被标记,则存储器控制器可以优雅地完成(例如,用响应进行响应以及丢弃)(框188)存储器写入请求。过程180的这种动作可以是有益的,特别是如果被标记的存储器写入请求指向持久性存储器并且未被标记的存储器写入请求指向易失性存储器。特别地,在这种情况下,在电源故障期间,指向易失性存储器的存储器写入请求可以被优雅地完成(例如,用响应进行响应以及丢弃),因为在电源故障已经发生之后易失性存储器中的数据将丢失。

[0057]

当存储设备控制器接收到存储设备写入请求时,可以由存储设备控制器执行在过程180中表示的类似操作。此外,在过程180的实施例中可以利用存储其它请求(例如,读取请求)的高速缓存行。在电源故障事件期间,存储器控制器或存储设备控制器可以通过用零进行响应并且优雅地退出读取请求来选择性地处理读取请求。此外,在电源故障事件期间,存储器控制器或存储设备控制器可以通过以下方式来选择性地处理写入请求:向存储器或存储设备目的地提交被标记的写入请求,以及优雅地完成(例如,用响应进行响应以及丢弃)未标记的写入请求。

[0058]

本系统和技术涉及通过在电源故障期间优先化持久性高速缓存行冲刷来优化设备中的冲刷操作的实施例。特别地,本系统和技术通过选择性地避免完成某些高速缓存行冲刷(例如,不将高速缓存行提交到某些存储器或存储设备目的地)减少了在集成电路系统10检测到电源故障之后保持集成电路系统10存活所需的时间量。这种减少的时间量也减少了完成未决冲刷操作所需的电量。因此,备用电池大小可以基于指向持久性存储器的高速缓存行的数量,而不是基于指向持久性存储器的高速缓存行以及指向易失性存储器的高速缓存行的数量。

[0059]

示例性实施例

[0060]

示例性实施例1、一种方法,包括:

[0061]

经由一致性链路并且在集成电路系统的设备处,接收包括目的地地址的高速缓存行;

[0062]

经由设备确定与目的地地址相关联的存储器或存储设备类型,该存储器或存储设备类型包括持久性或非持久性;以及

[0063]

以指示与目的地地址相关联的存储器或存储设备类型的方式用元数据标记高速缓存行。

[0064]

示例性实施例2、示例性实施例1所述的方法,包括:

[0065]

响应于确定与目的地地址相关联的存储器或存储设备类型是持久性的:

[0066]

用指示高速缓存行指向持久性存储器的元数据标记高速缓存行;以及

[0067]

响应于确定与目的地地址相关联的存储器或存储设备类型是非持久性的:

[0068]

避免用指示高速缓存行指向持久性存储器的元数据标记高速缓存行;以及

[0069]

基于存在或缺少指示高速缓存行指向持久性存储器的元数据来处理高速缓存行。

[0070]

示例性实施例3、示例性实施例1所述的方法,包括:

[0071]

在集成电路系统处接收电源故障信号;以及

[0072]

响应于接收到电源故障信号和包括存储器写入请求的高速缓存行:

[0073]

当标记指示与所述目的地地址相关联的存储器或存储设备类型是持久性的时,选择性地将高速缓存行提交到持久性存储器;以及

[0074]

否则,当标记指示与所述目的地地址相关联的存储器类型是非持久性的时,选择性地避免将高速缓存行提交到易失性存储器。

[0075]

示例性实施例4、示例性实施例1所述的方法,包括:

[0076]

响应于接收到电源故障信号和包括存储器读取请求的高速缓存行:

[0077]

丢弃存储器读取请求并返回指示丢弃的响应。

[0078]

示例性实施例5、示例性实施例1所述的方法,包括:

[0079]

响应于接收到电源故障信号和包括存储设备写入请求的高速缓存行:

[0080]

将高速缓存行提交到存储设备。

[0081]

示例性实施例6、示例性实施例1所述的方法,包括:

[0082]

经由存储器或存储设备控制器处理高速缓存行,而不管高速缓存行的标记指示什么。

[0083]

示例性实施例7、示例性实施例1所述的方法,由设备中的一致性链路软逻辑执行。

[0084]

示例性实施例8、一种集成电路系统,包括:

[0085]

中央处理单元;

[0086]

设备,包括:

[0087]

存储器控制器,其被配置为管理耦合到所述设备的存储器;以及解码器,其被配置为解码高速缓存行以确定高速缓存行的目的地;

[0088]

将设备耦合到中央处理单元的通信链路;

[0089]

耦合到设备的易失性存储器;以及

[0090]

耦合到设备的持久性存储器;

[0091]

其中,集成电路系统被配置为:

[0092]

接收高速缓存行;

[0093]

识别高速缓存行是指向持久性存储器还是易失性存储器;以及

[0094]

用元数据标记高速缓存行以区分指向持久性存储器的高速缓存行和指向易失性存储器的高速缓存行。

[0095]

示例性实施例9、示例性实施例8所述的集成电路系统,其中,存储器控制器被配置为:

[0096]

接收电源故障信号;以及

[0097]

响应于接收到电源故障信号和包括存储器写入请求的高速缓存行:

[0098]

如果高速缓存行指向持久性存储器,则选择性地将高速缓存行提交到持久性存储器;以及

[0099]

否则,如果高速缓存行指向易失性存储器,则选择性地避免将高速缓存行提交到易失性存储器。

[0100]

示例性实施例10、示例性实施例9所述的集成电路系统,包括备用电池,其被配置为当在集成电路系统上断言电源故障信号时为集成电路系统供电,并且其中备用电池被配置为支持在电源故障信号之后提交持久性高速缓存行。

[0101]

示例性实施例11、示例性实施例15所述的集成电路系统,其中,基于与将被提交到持久性存储器的高速缓存行的数量相对应的队列长度,而不是基于与将被提交到易失性存储器的高速缓存行的数量相对应的队列长度,来确定所述备用电池的大小。

[0102]

示例性实施例12、示例性实施例8所述的集成电路系统,其中,存储器控制器被配置为:

[0103]

接收电源故障信号;以及

[0104]

响应于接收到电源故障信号和包含存储器读取请求的高速缓存行:

[0105]

用响应来响应高速缓存行,其中所述响应包括默认响应。

[0106]

示例性实施例13、示例性实施例8所述的集成电路系统,包括:

[0107]

耦合到设备的存储设备;

[0108]

其中,设备包括被配置为管理所述存储设备的存储设备控制器;

[0109]

其中,集成电路系统被配置为:

[0110]

接收第二高速缓存行;

[0111]

识别第二高速缓存行是指向持久性存储器、易失性存储器还是存储设备;以及

[0112]

用元数据标记高速缓存行以将所述高速缓存行与指向易失性存储器或持久性存储器的高速缓存行区分开来。

[0113]

示例性实施例14、示例性实施例8所述的集成电路系统,其中,设备包括现场可编程门阵列(fpga)设备或专用集成电路(asic)设备。

[0114]

示例性实施例15、示例性实施例8所述的集成电路系统,其中,设备上的逻辑被配置为:

[0115]

从中央处理单元接收第二高速缓存行;

[0116]

确定第二高速缓存行是否指向持久性存储器;

[0117]

响应于确定第二高速缓存行指向持久性存储器:

[0118]

用元数据标记第二高速缓存行,以确保将第二高速缓存行提交到持久性存储器;以及

[0119]

响应于确定第二高速缓存行不指向持久性存储器:

[0120]

优雅地丢弃第二高速缓存行。

[0121]

示例性实施例16、示例性实施例8所述的集成电路系统,其中,中央处理单元耦合到第二持久性存储器和第二易失性存储器,并且其中中央处理单元被配置为标记指向第二持久性存储器或到第二易失性存储器的第二高速缓存行,以区分指向第二持久性存储器的第二高速缓存行和指向第二易失性存储器的第二高速缓存行。

[0122]

示例性实施例17、一种包括指令的非暂时性、有形且计算机可读的介质,所述指令在由存储器控制器的处理器执行时使所述存储器控制器执行包括以下的操作:

[0123]

将高速缓存行接收到被配置为存储未决操作的队列中;

[0124]

基于所述高速缓存行是否用元数据标记来确定所述高速缓存行是指向持久性存储器还是非持久性存储器;

[0125]

识别电源故障;以及

[0126]

响应于识别到电源故障:

[0127]

响应于高速缓存行指向持久性存储器,将高速缓存行提交到存储器;以及

[0128]

响应于高速缓存行指向非持久性存储器,避免将高速缓存行提交到存储器。

[0129]

示例性实施例18、示例性实施例17所述的非暂时性、有形且计算机可读的介质,其中,所述操作包括在不存在电源故障的时间期间:

[0130]

将高速缓存行提交到存储器,而不管高速缓存行是指向持久性存储器还是非持久性存储器。

[0131]

示例性实施例19、示例性实施例17所述的非暂时性、有形且计算机可读的介质,其中,所述队列包括写入未决队列。

[0132]

示例性实施例20、示例性实施例17所述的非暂时性、有形且计算机可读的介质,其中,所述高速缓存行包括存储器读取请求,并且其中所述操作包括:

[0133]

当高速缓存行指向非持久性存储器时用默认响应来响应高速缓存行。

[0134]

虽然在本公开中阐述的实施例可易于进行各种修改和替代形式,但具体实施例已经通过示例的方式在附图中示出并且已经在本文中进行了详细描述。然而,应当理解,本公开并不旨在限于所公开的特定形式。本公开将涵盖落入由以下所附权利要求限定的本公开的精神和范围内的所有修改、等同物和替代方案。

[0135]

本文提出和要求保护的技术被引用并应用于实际性质的实物和具体示例,它们显著地改进了当前技术领域,因此,不是抽象的、无形的或纯理论的。此外,如果附于本说明书

的任何权利要求包含被指定为“用于[执行][功能]

……

的单元”或“用于[执行][功能]

……

的步骤”的元素,则旨在此类元素应根据35u.s.c.112(f)进行解释。然而,对于包含以任何其它方式指定的元素的任何权利要求,旨在此类元素不应根据35u.s.c.112(f)进行解释。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1